## ACRST=1833 ORIGINAL OFFICIAL TRANSCRIPT OF PROCEEDINGS

Agency:

Nuclear Regulatory Commission Advisory Committee on Reactor Safeguards

Title:

Subcommittee on Computers in Nuclear Power Plant Operations and Subcommittee on Instrumentation and Control Systems Joint Meeting

Docket No.

LOCATION:

Bethesda, Maryland

DATE:

Wednesday, February 6, 1991

1 - 228PAGES

## ACRS Office Copy - Retain for the Life of the Committee

011

TRO4 (ACRS) RETURN ORIGINAL TO B.J.WHITE, ACRS P-315

THANKS! BARBARA JO #27288

1612 K St. N.W., Suite 300 Washington, D.C. 20006 (202) 293-3950

ANN RILEY & ASSOCIATES, LTD.

02120281 910206 R ACR3

|   | 1  |                                                                 |

|---|----|-----------------------------------------------------------------|

| ) | 2  |                                                                 |

|   | 3  |                                                                 |

|   | 4  | PUBLIC NOTICE BY THE                                            |

|   | 5  | UNITED STATES NUCLEAR REGULATORY COMMISSION'S                   |

|   | 6  | ADVISORY COMMITTEE ON REACTOR SAFEGUARDS                        |

|   | 7  |                                                                 |

|   | 8  | DATE: February 6, 1991                                          |

|   | 9  |                                                                 |

|   | 10 |                                                                 |

|   | 11 |                                                                 |

|   | 12 |                                                                 |

| • | 13 | The contents of this transcript of the                          |

| , | 14 | proceedings of the United States Nuclear Regulatory             |

|   | 15 | Commission's Advisory Committee on Reactor Safeguards,          |

|   | 16 | (date)                                                          |

|   | 17 | as reported herein, are a record of the discussions recorded at |

|   | 18 | the meeting held on the above date.                             |

|   | 19 | This transcript has not been reviewed, corrected                |

|   | 20 | or edited, and it may contain inaccuracies.                     |

|   | 21 |                                                                 |

|   | 22 |                                                                 |

|   | 53 |                                                                 |

|   | 24 |                                                                 |

| ) | 25 |                                                                 |

|   |    |                                                                 |

| 1   | UNITED STATES OF AMERICA                                     |

|-----|--------------------------------------------------------------|

| 2   | NUCLEAR REGULATORY COMMISSIC.                                |

| 3   | ***                                                          |

| 4   | ADVISORY COMMITTEE ON REACTOR SAFEGUARDS                     |

| 5   | ***                                                          |

| 6   | SUBCOMMITTEE ON COMPUTERS IN NUCLEAR POWER PLANT OPERATIONS  |

| 7   | AND                                                          |

| 8   | SUBCOMMITTEE ON INSTRUMENTATION AND CONTROL SYSTEMS          |

| 9   | JOINT MEETING                                                |

| 3.0 |                                                              |

| · 1 |                                                              |

| 12  | Nuclear Regulatory Commission                                |

| 13  | 7920 Norfolk Avenue                                          |

| 14  | Bethesda, Maryland                                           |

| 15  |                                                              |

| 16  | Wednesday, February 6, 1991                                  |

| 17  |                                                              |

| 18  | The aby ve-entitled proceedings commenced at 8:30            |

| 19  | o'clock a.m., pursuant to notice, Harold W. Lewis, Chairman, |

| 20  | presiding:                                                   |

| 21  |                                                              |

| 22  |                                                              |

| 23  |                                                              |

| 24  |                                                              |

| 25  |                                                              |

|     |                                                              |

-

D.

2

| 3  | H. Lewis                                |

|----|-----------------------------------------|

| 4  | W. Kerr                                 |

| 5  | I. Catton                               |

| 6  | P. Shewmon                              |

| (y | C. Michelson                            |

| 8  | J. Carroll                              |

| 9  | E. Wilkins, Jr.                         |

| 10 | C. Wylie                                |

| 11 | P. Davis, Consultant                    |

| 12 | W. Lipinski, Consultant                 |

| 13 | T. Rotella, Cognizant ACRS Staff Member |

| 14 | M. El-Zeftawy, Federal Official         |

| 15 |                                         |

| 16 | PARTICIPANTS:                           |

| 17 |                                         |

| 18 | L. Rib, AECL Technologies               |

| 19 | N. Ichiyen, CANDU-3                     |

| 20 | K. Scarola, ABB/CE                      |

| 21 | G. Remley, Westinghouse                 |

| 22 | Barry Simon, GE                         |

| 23 |                                         |

| 24 |                                         |

| 25 |                                         |

## PROCEEDINGS

[8:30 a.m.]

MR. LEWIS: The meeting will now come to order. This is a joint Subcommittee meeting of the Advisory Committee on Reactor Safeguards-Computers in Nuclear Power Plant Operations -- I didn't know that was the name of our Subcommittee -- and the Instrumentation and Control System Subcommittees.

9 I'm Hal Lewis, Chairman of the first named

10 Subcommittee and Bill Kerr, to my left, is the Chairman of

11 the Instrumentation and Control Systems Subcommittee.

12 The ACRS members in attendance are Jay Carroll, 13 Ivan Catton, Carl Michelson, Paul Shewmon, Ernest Wilkins, 14 and Charlie Wylie. Also in attendance are ACRS Consultants 15 Pete Davis and Walt Lipinski. I don't see them. It says on 16 my piece of paper that they're here, but they are, in fact, 17 here in spirit and not in body.

The purpose of this meeting is to discuss computer software applications in future nuclear plants, software reliability assurance, software ".rification and validation, and software sabotage issues. T might just interject that that's news to me, because I thought we were going to discuss both software and hardware. But that will emerge as we go along.

Tom Rotella, to my right, is the Cognizant ACRS

25

.

P1 6

.

.

staff member for this meeting. Medhat El-Zeftawy is the designated Federal official, somewhere in the room. There is to my left.

1

2

3

The rules for participation in today's meeting have been announced as part of the notice of the meeting previously published in the Federal Register on January 23, 1991. Portions of this meeting will be closed due to discussions of company-proprietary information and that has been so noticed.

10 A transcript of the meeting is being kept and will 11 be made available as stated in the Federal Register Notice. 12 It is requested that each speaker first identify himself or 13 herself and speak with sufficient clarity and volume so that 14 he or she can be readily heard.

15 We have received no written comments or requests 16 to make oral statements from members of the public. As a 17 general pattern, this is an introductory meeting, so we will 18 go through a number of experiences that people have had 19 trying to cope with the change in technology that has come 20 with the computer evolution in the nuclear business.

We're fortunate today to have some participation from our neighbors to the north, and I'm told that Lewis Rib will introduce the operation.

24 Do any of the other members want to say anything 25 before we get into the meat of the operations?

MR. MICHELSON: Yes. We did have the hardware 1 2 discussion yesterday, which is listed in the Subcommittee 3 meeting notice. Today was to be the software. 4 MR. LEWIS: I see. Ivan? MR. CATTON: It's my understanding that you really 5 shouldn't separate the two when you're looking to see 6 7 whether or not the system is going to work reliably. Is 8 there any rationalization for this separation? 9 MR. LEWIS: None. MR. CARROLL: That's why we had the meetings one 10 11 day after the other. 12 MR. CATTON: So the connection is 12 hours. MR. MICHELSON: The connection is it takes two 13 days to cover both subjects and somehow you have to have one 14 15 first and then the next one. 16 MR. LEWIS: But Ivan's point is well taken. There 17 aren't two subjects. There's one subject. 3.8 MR. CATTON: That's right. 19 MR. LEWIS: I just confess that perhaps I haven't 20 been reading my mail. I didn't know that the hardware was 21 going to be covered yesterday. MR. KERR: Why don't we decide to do better next 22 time and go ahead with this meeting. 23 MR. LEWIS: I think we should, but there is an 24 25 important issue here.

MR. CARROLL: I think you're going to hear a fair

amount about hardware today anyway.

MR. SHEWMON: Otherwise it might be nice to have a summary of what was learned yesterday.

MR. LEWIS: Let's do that at an appropriate time and let's not interrupt the speaker. Let's proceed.

7 MR. RIB: I'm going to give just a very brief 8 introduction to the speaker. My name is Lewis Rib. I am 9 representing AECL Technologies, an American corporate 10 entity, with a local office in Rockville, Maryland.

Among other activities, AECL Technologies is representing AECL, which stands for Atomic Energy of Canada Limited, the AECL's CANDU-3 nuclear power plant design in the United States. The ACRS invited AECL Tech: plogies to participate in this Subcommittee meeting to describe our approach to the utilization of computers in nuclear power plant operations and instrumentation and control systems.

18 We welcome this opportunity as our second 19 appearance before the ACRS. I would like to introduce 20 Norman Ichiyen of CANDU-3 Design Team, who will make the 21 presentation on the CANDU computer control technology. 22 Normal Ichiyen's background includes a Bachelor's of 23 Engineering from McGiil, a Master of Applied Science from 24 the University of Toronto.

25

3

4

5

6

He started with AECL in 1973 in the safety systems

concept area. He was the program manager for the computer based shutdown systems development project in 1980 through

1982. This concept was implemented at the Darlington

Nuclear Generating Station. Currently, he is Manager of

CANDU-3 Computers and Control Centers Branch.

6 MR. ICHIYEN: Good morning. As Lewis said, I've 7 been asked to talk about the use of computers and digital 8 systems in CANDU nuclear power plants. As the agenda says, 9 and this is what I assumed you wanted to hear about today, 10 was from the perspective of mainly in the software issues, 11 future applications and plans, issues like software V&V, 12 software reliability, and sabotage was another topic.

How I propose to address these topics is shown in this outline next.

[Slide.]

16 MR. ICHIYEN: This is going to be awkward. I 17 think I'll stay on this side.

18 MR. WILKINS: I wonder if you could rotate this19 about ten degrees clockwise.

20

15

MR. ICHIYEN: Is that okay?

21 MR. WILKINS: Thank you. In order to talk about 22 where we're going to; that is our future applications and 23 plans; I felt it's important that you understand where we're 24 coming from. In CANDU technology, we try to use an 25 evolutionary process. So what I will talk about first and,

again, very briefly is a bit of history of our use of computers in CANDU stations, and then bring you up to date to the latest station that's in service, which is the Darlington Station that just went recently into service.

1

2

3

4

5 I'll use that as an example of the state of the 6 technology for our current plants. Getting to future 7 applications. I'll have a bit of a discussion on how we have 8 evolved in our design and concept of digital systems. For 9 this part of the talk, I'll use the CANDU-3 project, which I 10 am associated with, as an example of the kinds of things 11 that we're doing for that design.

12 As I understand, the main kind of issues you 13 wanted to get at were how to produce reliable software and 14 aspects of it, like verification and validation, software 15 reliability. So rather than talk about these pieces as 16 parts of the puzzle in isolation, I'd rather prefer to talk 17 about our whole software engineering process. We feel that 18 the integrated process, which is integration between 19 development, verification and testing, software reliability, 20 are all the more important part.

In order to be able to discuss this in the short timeframe that I have, I'm going to concentrate on safetycritical software where we've had some experiences with the Darlington shutdown system. In this part of the talk, I'm going to talk about our experience licensing the shutdown

systems on Darlington; more important, what lessons we learned from Darlington or what lessons we hope we've learned from Darlington; and, how we're applying these lessons in what we're doing in the future.

5 For AECL and Ontario Hydro, we feel that the 6 important movement is in the area of standards, and I'll 7 describe why and some of the aspects of that later. Then 8 I'll move into some of the fundamental principals of a high 9 level standard for safety-critical software which we have 10 just now issued for our own internal use.

When I'm talking about these fundamental principals, they really embody the features of V&V and software reliability. So that's how I propose to get at those issues, while talking about these aspects of the standard. Next I'll talk about the overall status, where we are with this program, where we will be in the future.

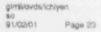

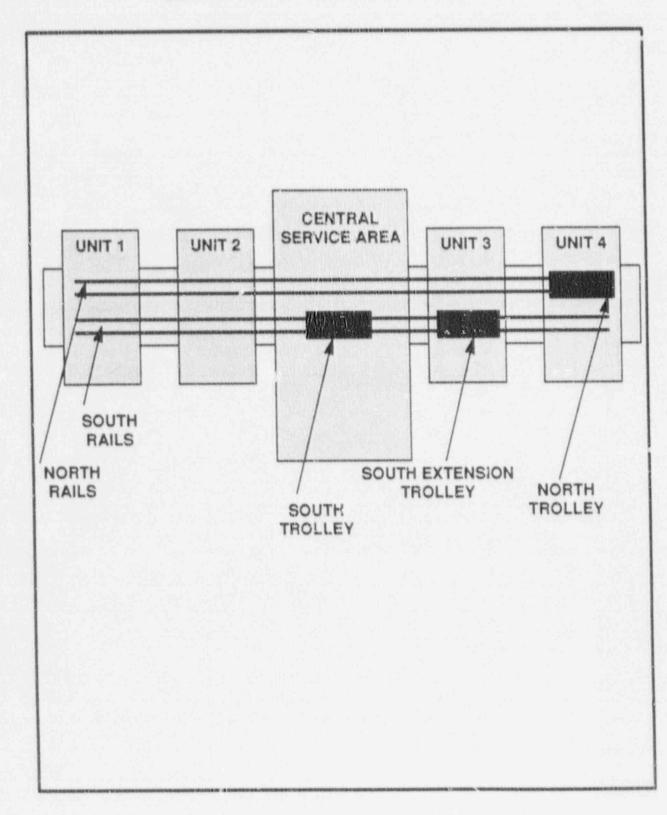

As a special item, I was asked by Tom Rotella to talk about our experiences with the Bruce fueling machine incident which I assume most of you are aware of. It's an event that happened about a year ago. I'll describe it very briefly with some conclusions and lessons learned from that experience.

[Slide.]

23

1

2

3

4

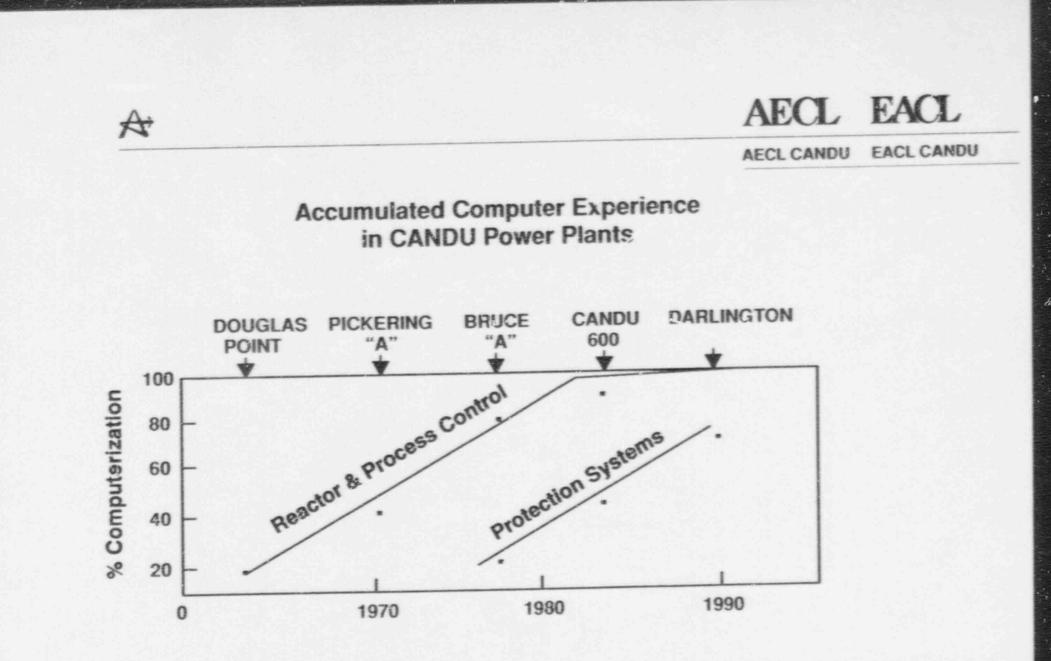

24 MR. ICHIYEN: Starting off with our experience 25 with computers in CANDU, this is just a simple slide, just

meant to show the timeline over the years of what we've been doing with computers and, on the vertical axis, the degree of computerization that we've used in these plants.

1

2

3

From our first plant at Douglas Point back in the late 1960s, we had a fair degree of computer control on a number of the main processes. With respect to reactor and process control, this has steadily increased so that at the point where our CANDU-600 designs were in service in the early 1980s, we had pretty well reached full computerization of all systems.

Darlington is, I would say, about 99 percent there, with most systems having computerization in some aspects. Only in the late 1970s did we start in the use of computers in production systems. Back in the late 1970s, we used computers for monitoring of important variables and shutdown system variables at the Bruce A reactor.

In the early 1980s, we used trip comparitors, digital trip comparitors for the shutdown systems, for the process trips. On Darlington, for the shutdown systems, we have full computerization. I'll talk about that. The reason it doesn't show 100 percent computerized is because not all of the other safety systems have full use of computers.

24 MR. SHEWMON: You'll explain later what you mean 25 by full computerization?

MR. ICHIYEN: Yes.

[Slide.]

1

2

25

MR. ICHIYEN: In terms of historically, again, I said I would talk about Darlington. In answer to your guestion about computerization, I think this gets at that. Again, I'm trying to compress this into a short period of time. So it is fairly general.

8 We have three kinds of classes of computers on the 9 Darlington system. In Canada, we've called the main control 10 computers DCCs, stands for Digital Control Computer. We've 11 used that terminology right from our first reactors. On 12 Darlington, all the reactor and process control is done in 13 the DCCs. It's a dual redundant central kind of system with 14 triplicated channels and dual redundancy on the computers.

15 On Darlington, an additional difference that we 16 didn't have on the CANDU-600 design was that the device 17 logic control was done in PLCs, with the Ontario Hydro 18 proprietary design called the OH-180.

19 Computers were also used for the operator 20 interface in the main control room, used for alarm 21 annunciation and data logging. In CANDU, we have on-line 22 fueling, I think as most of you are aware, and that is done 23 on computer control. So we have separate fuel handling 24 computers for that function.

In the safety systems on Darlington, that was the

first time we have used full computerization of the shutdown systems. What I mean by full computerization is we have a computer, set of processors that carry out the trip functions, the trip decision functions. If the heat transfer pressure is below a certain level, then it says initiate the trip signal.

1

2

3

4

5

6

7 We use it also for operator displays, the 8 interface to the operator in the main control room, 9 triplicated channels of information. Both in the main 10 control room and in CANDU designs, we have a secondary 11 control area for the seismic events, as well.

12 It's also used for operator aided testing. In 13 CANDU, we've used the philosophy that we test the shutdown 14 system right from the transducer to the final elements, and 15 we do that through actually inputting the pressure signals 16 and pressure transducers and checking that the channel, in 17 fact, does trip.

18 MR. LEWIS: I wonder if I could interject a couple 19 of questions. One is when you use the term computer all 20 through this, do you mean digital computer or are you just 21 using the term computer generically?

22 MR. ICHIYEN: In all these cases, they're general 23 purpose computers, except for this one which is a PLC.

24 MR. LEWIS: I understand they're general purpose, 25 but are they digital or analog?

MR. ICHIYEN: Digital, yes. MR. LEWIS: They're all digital. MR. ICHIYEN: Yes.

1

2

3

25

MR. LEWIS: Second question. For example, this last issue of testing of the shutdown system; when you say testing, you mean put in -- you said put in the pressure signals and temperature signal and what have you and see that the system works.

9 But you don't try all conceivable malfunctions

10 within the system to test it.

MR. ICHIYEN: No. Historically, this is a periodic tescing. Again, moving back a bit, in Canada, there's a requirement to show an unavailability that the shutdown meets ten-to-the-minus-three. In order to do that, you have to do periodic testing largely, historically, to detect hardware faults that have occurred since the last time of testing.

MR. LEWIS: I'm just ceasing this example to ask a deeper question. By testing, what you mean is assuring that the system will perform as required if it gets the expected malfunction signals, but not simulating failures in the computer that could generate off-line strange signals. That you don't do. That's V&V, which you will come to, presumably.

MR. ICHIYEN: That's right. We do things like

self-checks and self-tests in the computers to try and get at that aspect of it. Periodic tests are -- for hardware, they're pretty thorough because you actually -- as far as the shutdown system knows, it can't distinguish whether this is an actual challenge from an event or a test.

1

2

3

4

5

6

7

We don't test just the processor, for example. MR. LEWIS: I understand.

8 MR. ICHIYEN: In the past this was manually done 9 and now we have it -- those controls are controlled by a 10 separate computer called the Safety System Monitor Computer. 11 As I mentioned, we did, earlier on Bruce, monitoring 12 important shutdown system variables, through a separate 13 computer again, and that's also done on Darlington.

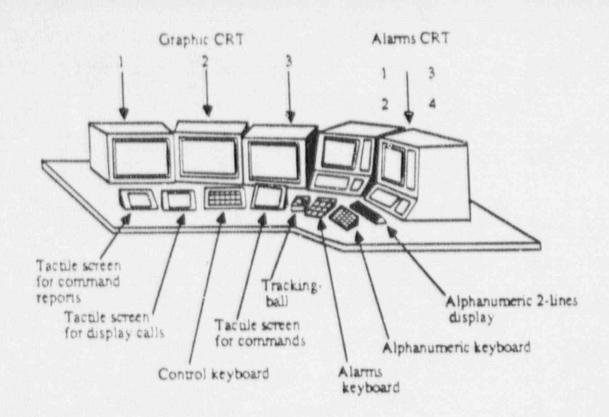

On Darlington, another safety system that had a degree of computerization was in the emergency core cooling system where we use the OH-180s for discreet logic control. I did have one slide to show you a picture of what the Darlington control room looks like. Actually, I've got to flip backwards.

20 When I mentioned before the shutdown system 21 interface, those are these 12 CRTs; one for Shutdown System 22 1, one for Shutdown System 2. You can see some of the 23 others. I think that's another safety system, emergency 24 core cooling, and that doesn't have the digital display. So 25 it's marked contrast from what we do with the shutdown

systems.

1

25

| 2  | All I'm trying to point out here is that we have a           |

|----|--------------------------------------------------------------|

| 3  | fairly high degree of reliance on the computer interface     |

| 4  | through the CRTs, the annunciation and the data logging.     |

| 5  | (Slide.)                                                     |

| 6  | MR. ICHIYEN: Moving on from Darlington, as Lewis             |

| 7  | said, the reactor design that I'm associated with now is the |

| 8  | CANDU-3. It's really our next generation CANDU after the     |

| 9  | Darlington station. I've just listed some of the features    |

| 10 | here, one of which is a v. y short construction schedule.    |

| 11 | That aspect of it is a contributor to the directions that    |

| 12 | we're going in CNI, and I'll talk about some of those later  |

| 13 | when I talk about the features of the CANDU-3.               |

| 14 | I'll just run through these quickly. Modula.                 |

| 15 | design construction techniques which most of the other       |

| 16 | competitors are using in order to meet this construction     |

| 17 | schedule; an interesting feature we call 100-year life, not  |

| 18 | that all components are going to last 100 years, but our     |

15

19 target is to have everything replaceable.

20 On previous CANDUs, it was not aimed for a rapid 21 fuel channel replacement. On CANDU-3, we are aiming at that 22 target as part of this overall target of a 90-day outage 23 within which we should be able to replace all equipment, 24 including steam generators.

As I said, this is a target. Currently, the fuel

channel replacement takes longer than 90 days. We're talking about fort to vive months is what we currently see now for a complete retubing, refueling, defueling and refueling and the whole process. That's the current state of the design and we're still trying to get that down to within that target.

(Slide.)

1

2

3

4

5

6

7

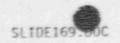

8 MR. ICHIYEN: I thought I'd talk now, since we're 9 talking CANDU-3, how the digital systems are evolving on 10 CANDU-3 from Darlington. So I'm using Darlington as a 11 reference and I will describe what features on the CANDU-3 12 are different from it. With respect to control, as I said 13 before, Darlington used a dual redundant hot standby kind of 14 configuration for the control systems.

Now we're moving from this redundant central type system to wha. I call a true distributed control system architecture. There are two features what I feel are the true distributed control system architecture. One is geographic distribution where the processes are distributed throughout the plant in the areas where they have the applications.

The second feature is what I call closing the loop over the highway. A lot of vendors' products that are called distributed control are really distributed processing and a lot of them don't do the closing of the loop over the

highway. What I mean by that is if an input signal is taken at one location but is needed for a control function in a different processor, then that information, in our concept, is done by sending it over the highway for use at the second proces

1

2

3

4

5

23

6 The other area where we're evolving from 7 Darlington is in the operator interface, where we have the 8 central system that did control and display. We're 9 splitting that functionality up so that there is a separate 10 what I'll call plant display system which is responsible for 11 the operator interface for presentation of information in 12 the main control room.

On safety systems where we're evolving to is a higher degree of computerization, using more systems. Emergency core cooling, as I said, Darlington used it for the device logic, but not for the displays. Here we'll use all functions using computers. The other area is software practices. We feel that we are evolving in these practices and those are the concepts we're going to use for CANDU-3.

Largely the rest of my talk deals with this aspect, the software practices that we see we are evolving to.

(Slide.)

24 MR. ICHIYEN: The agenda said that you wanted to 25 talk about V&V and software reliability. The way I said I

would do it is talk about the whole process in general. As I said, I will concentrate on safety-critical software in order to focus on this in the time that I do rather than talk at even higher levels of generality.

5 What I will describe is our overall approach for 6 producing reliable software. We don't feel that any one 7 component or factor is sufficient and we use an overall 8 approach. I will discuss the part played by V&V, software 9 reliability measures and so on.

10

1

2

3

4

[Slide.]

MR. ICHIYEN: Again, in order to say where we're going to, it's important to spend a little time talking about where we come from and our experiences on Darlington are very relevant in the directions that we're taking, especially with respect to safety-critical software.

I think for those of you who are unaware, we have been having a dialogue, I'll say, with our Atomic Energy Control Board from about 1985 to 1990 about the licensing of these shutdown systems and particularly the software. I could spend about a day talking about all the issues in sequence, but that wouldn't serve the purpose here.

I'd like to characterize it with a few features.

One was it was an extremely drawn out licensing process.

The regulatory group started off with one set of concerns

and the issues kept changing over the years. So we would

react and make some changes. This process was a very, very long drawn out affair.

1

2

3 There were a different set of issues that started in 1987 when the Control Board hired a consultant, Dr. 4 5 Parnas from Queens University. I think a lot of you are 6 probably familiar with his name. He's guite a well known 7 authority in the area of software and reliability of software and his name is associated with the Star Wars 8 9 designs in the U.S. earlier. He is a very competent and 10 knowledgeable person and the Control Board utilized his 11 services.

In terms of conclusions -- I should first say what actions we took coming out of that experience on the licensing. Again, these are just some of the major highlights. There are a whole lot of actions that we ended up taking, but the characteristic ones are the ones here.

Again, back to the name Dr. Parnas, this is one of the things that he instigated. We what I called backengineered a software design specification using mathematical notation, which is known as formal methods in the industry.

Previously we had vield an English language specification, a functional specification. I think it's fairly well agreed that a lot of errors that do occur start with that English language specification. English is not a

very precise language. It's guite ambiguous. A lot of the 2 errors that are made in any software engineering process either are errors in the functional requirements or errors in interpretation.

1

3

4

22

25

20

6 Either way, use of a mathematical notation was 6 felt to help understanding and other features, and I'll go 7 into those later in more detail.

8 MR. LEWIS: Is this a matter of mapping the output 9 to the input using the Bacchus Nuir notation or are we 10 talking about something else?

11 MR. ICHIYEN: What we did was we took the English 12 language specification and turned it into the mathematical 13 notation.

14 MR. LEWIS: I'm talking about which mathematical notation was used. 15

16 MR. ICHIYEN: In this case, we used Dr. Parnas' 17 particular notations.

18 MR. LEWIS: His own idiosyncratic, not one that is used by anyone else? 19

20 MR. ICHIYEN: Probably that's true, yes. It's not 21 a standard notation.

MR. LEWIS: I see. Thank you.

23 MR. WILKINS: Is it at least published by him 24 someplace?

MR. ICHIYEN: He's got a number of papers that are

published. He's probably one of the more prolific writers

in the field.

MR. LEWIS: I didn't know he used a notation different from the one other computer scientists use. That's news to me.

6 MR. ICHIYEN: I think in terms of notation, maybe 7 I'm causing some confusion. He uses certain notation to 8 describe constants, variables and what exact notation is 9 used for that probably isn't that critical.

10 MR. LEWIS: The one that is used by most computer 11 scientists is called the Bacchus Nuir notation. Never mind. 12 We'll go into that later.

MR. ICHIYEN: The second action that was taken 13 began really through Dr. Parnas' involvement. It was to 14 15 establish a walk-through in order to verify that the code met the formal software design specifications. In theory 16 this was a doable job, but neither he nor others had really 17 18 worked out the practical aspects of it. So that was one of the things that took a lot of time, was working out how we 19 do this in practice. 20

It involved creating new techniques that hadn't been used before, creating what we call program function tables from the code and comparing to the mathematical notations at the beginning. It involved establishing techniques and methodologies for doing that and how you

compare them.

1

| 2  | The third significant action is a random testing             |

|----|--------------------------------------------------------------|

| 3  | program. I won't go into more here. I'll talk about it       |

| 4  | later as we go. It's testing the processor. So it's          |

| 5  | putting inputs in, but it's not testing the whole system as  |

| 6  | an integrated system.                                        |

| 7  | MR. MICHELSON: Ivan, you need to use your                    |

| 8  | microphone.                                                  |

| 9  | MR. ICHIYEN: Sorry?                                          |

| 10 | MR. CATTON: I was being chastised for not                    |

| 11 | speaking into the microphone.                                |

| 12 | MR. LEWIS: I wonder if I could ask one question.             |

| 13 | In the specifications, do you distinguish between reliable   |

| 14 | operation and graceful failure modes when the system fails?  |

| 15 | That is do you go to the next level of assuring graceful     |

| 16 | failure when there are hardware failures?                    |

| 17 | MR. ICHIYEN: In the Darlington system, this is               |

| 18 | the shutdown system and not a control function. So what      |

| 19 | we're interested in in the safety features is that it's fail |

| 20 | safe. So wherever there is any doubt, the action is to       |

| 21 | if it's in an undefined stage or something that's not right, |

| 22 | we go to the trip state.                                     |

| 23 | MR. LEWIS: What I'm suggesting is, and that's why            |

23 MR. LEWIS: what I'm suggesting is, and that's why 24 I was extremely unhappy to learn that we'd separated 25 hardware from software in this meeting, the software has to

be written in such a way as to accommodate hardware failures, in such a way that it leads to a graceful failure of the overall system.

1

2

3

8

9

6 It's the job of the software to 20 that. Is that 5 within the specs that you laid dowr on the system?

6 MR. ICHIYEN: I wasn't that familiar with the 7 details.

MR. LEWIS: All right. Thank you.

MR. ICHIYEN: I could check into it.

10 MR. SHEWMON: A variant to that, which I will 11 bring up maybe twice, but at least later, has to do with the 12 Rancho Seco failure in which there was a power supply 13 failure, which is a variety of equipment failure that may 14 not have been safety primarily. But how the system copes 15 with something like that will come up also.

MR. ICHIYEN: Power supply fai ires?MR. SHEWMON: Yes.

18 MR. ICHIYEN: To the computers?

MR. SHEWMON: Well, this was a power supply to instrumentation and control in that case and then different systems went in different directions and the operator wasn't sure where they were. So he had a lot of problems.

23 MR. ICHIYEN: In the CANDU designs, which is 24 probably the same in other designs, the power supplies for 25 the safety systems are separate from the control systems.

We have a complete separation of safety and control. There 1 is no functional or equipment connections in any sort. 2 3 We use triplicated channels in the shutdown systems and there's two or three --4 6 MR. SHEWMON: Fine. I'll ask the question when we come to control and how it might interact with safety, then. 6 7 [Slide.] 8 MR. ICHIYEN: The real issue that came out of the 9 Darlington licensing experience, in our minds, was the lack of an accepted definition of the acceptable quality that 10 11 software has to have in order to be approved by our Atomic Energy Control Board. As I said before, the issues kept 12 13 changing. There was a lot of subjectivity and we feel that 14 the real cause of that was that it wasn't a real de facto 15 standard or real standard which set the requirements for 16 what is required. 17 So our objective now is to create a set of 18 standards, procedures and guidelines for software 19 engineering, overall categories of software. Our first task

20 is --

21 MR. CATTON: How do you define acceptable quality? 22 MR. WILKINS: Next two lines. It has to be 23 approved by the AECB. Of course, you can ask a different 24 question. How do you assure that it works? That's a 25 different matter.

MR. LEWIS: And still a third matter is how to be sure that when it doesn't work, it doesn't work in a relatively benign way, which is the third matter.

1

2

3

MR. ICHIYEN: As I said, our first task is the 4 5 creation of this set for safety-critical software. We're starting with that one because after all is said and done 6 7 and the plant is licensed, the Control Board has said the 8 effort to license the Darlington system required a lot of expertise and individual effort and a lot of subjectivity 9 10 even after having the formal specifications and the walk-11 throughs and so on.

12 So what they're setting as an objective for Ontario Hydro is to redesign the software over a period of 13 14 time of five to six years so that these problems do not 15 occur again. That's one of the main reasons for creating 16 this set of standards, so that we don't go into these same 17 problems again. We want to get an agreed set of requirements that we can both work towards and then use that 18 19 as the reference.

20 MR. CARROLL: The need to create a set of 21 standards in this area suggests that there are not adequate 22 standards already. What is your view of the existing U.S. 23 standards that are in the software area?

24 MR. ICHIYEN: I haven't read all of the U.S. 25 standards and so on. From what they're telling me, that the

standards are not aimed at the kind of applications or the techniques that we see or our requirements that we see.

There are a lot of good features in the standards. Some are more prescriptive and too low a level of detail. 4 5 What we're trying to achieve is a higher level standard 6 which, in a lot of ways, is methodology independent. We're 7 trying to specify what the core requirements are in a way that the Atomic Energy Control Board and the utilities and 8 9 ourselves can agree with, and then we work on our 10 methodologies.

11 We present these methodologies to the Control 12 Board and say does this meet the requirements as stated in 13 the standard. I'm saying we're trying to make it 14 methodology independent, but you really can't do that in all 15 areas. What we're trying to do is not limit the 16 methodologius unnecessarily.

17 I think maybe you'll get some of that picture when 18 I talk about some of our main principals to see whether those are embodied in the other standards. 19

[Slide.]

1

2

3

20

21 MR. ICHIYEN: There are really four parts to our 22 framework that we're developing. One is a categorization criteria. I think everybody would agree that software has 23 24 different categories in terms of what's required and what 25 kind of assurance requirements do you have for it, some of

which has no impact on safety, some of which is very important to safety, like a shutdown system, which is the last line of defense if there is an event.

1

2

3

25

4 The difficulty here is how do you quantify the attributes of what constitutes a category, how many 5 categories, what do you do with those categories. It's 6 7 clear the highest level being safety critical is an easy one to define. It gets a little fuzzier as you go through the 8 lower levels, like control software, monitoring software, 9 non-real time. It gets well beyond the plant software. You 10 11 get into analysis software and so on.

But we're starting with the safety critical one and working down from there.

MR. CARROLL: This standard would be broader than just control and protection. It would go into --

MR. ICHIYEN: Analysis software. 16 MR CARROLL: Analysis kind of software. 17 18 MR. ICHIYEN: We see it as a family of standards. For the real time ones, there should be a very close 19 relationship. So we're writing the safety critical one 20 21 first which, as I said, has been just issued for our own internal use. We are now working on the other categories. 22 Actually, I've already jumped ahead to my next slide. 23 24 [Slide.]

MR. ICHIYEN: Again, the four parts of this

framework at the categorization criteria, the high level standard which I've already described being largely aimed at being methodology independent, and then what a lot of people call sub-tier standards, which are a lot of the details and how-tos and specifics and things which are methodologyspecific.

Another aspect of what to do with developed 8 software, which is software that you purchase.

9 MR. KERR: Can you give me an example of a categorization criterion? 10

11 MR. ICHIYEN: Pardon?

1

2

3

4

5

6

7

MR. KERR: Can you give me an example of a 12 categorization criterion? 13

14 MR. ICHIYEN: Largely, the definition for safety critical, and I'll try and say this, safety critical 15 software would be software ... a system whose failure could 16 17 lead directly to a significant release of radiatio: to the 18 public or to the plant operations.

19 MR. KERR: Thank you.

MR. LEWIS: In this effort, which is more or less 20 a start from the bottom effort, did you bring in consultants 21 22 from other industries who have computerized themselves over the years, not just Parnas who is a well known person in the 23 24 business, but, for example, the 767 airplane, Boeing, is a 25 very highly computerized airplane. I would judge that it's

probably a factor of two less complicated than a nuclear

power plant, but not a factor of ten.

The telephone company is probably a factor of ten or 100 more complicated. So there's plenty of industrial experience with people who are trying to make very large computer systems work reliably and in a fail safe mode. Did those people get prought into this effort?

MR. ICHIYEN: We did what we thought was a fairly 8 extensive survey of not only the nuclear industry, but, as 9 you say, other industries. There is one distinction, 10 actually. With the way we do our designs, we felt that the 11 12 functionality of the trip functions that are true safety critical are not very complicated and the order of magnitude 13 is more like ten or 100 less than some of these larger 14 15 applications.

The number of lines of code in a Darlington t 16 computer is -- some people will say it's 3,000; some people, 17 if you take out the comments, you're down to 700. It's not 18 19 a lot of lines of code. We feel that for that specific kind 20 of application, a lot of the applications that are used for larger systems are not as precise or don't give as high 21 22 degree of confidence and the reliability that we feel that the methods for smaller systems can do. 23

In Canada, there's a telecommunications organization, Bell-Northern, and all the people, as you

said, the telephone industry are in conjunction with Dr.

Parnas. So they're doing work with him in that area, as

well. So the 're using techniques that are similar to a

large degree.

5 Within the nuclear industry, we did a jot of 6 talking to the people in the U.K. Actually, not in the 7 nuclear industry, but in the formal methods area. We've 8 talked to other people, France, the Westinghouse people and 9 what other vendors are doing in their software practices.

Having surveyed all of that, we feel that for our application the technology or the methodology that Dr. Parnas is refining, I'll say, is the one we feel the most comfortable with that will do the job for us. The thing about Dr. Parnas is that he hasn't defined what we think are workable methodologies.

16 He's been working on a lot of these things for 17 quite a long time. Things like trace specifications he's 18 been talking about for ten or twelve years. But it's only 19 when you get into real situations that you have to make the 20 methodologies work and you extend the boundaries of the 21 knowledge of a system.

So we've been working with these systems. In fact, we haven't defined our methodology yet. Again, I'm jumping ahead, but I'll say it now. We expect by the fall or mid-year of 1991 to have completed our studies on the

methodologies. AFCL and Ontario Hydro are working quite closely in this respect.

MR. LEWIS: The reason I started with the 767 example is that the complexity of the 767 is really not all that far from the complexity of a nuclear power plant. Certainly both of them are well below the Star Wars system. Even in the great Star Wars controversy, Parnas was really pretty much a minority of one on that advisory committee.

9 So he doesn't reflect at least the majority 10 sentiment of American -- forgive me -- of U.S. computer 11 scientists. But please go on. I'm slowing you down and 12 you're running behind.

[Slide.]

1

2

13

24

25

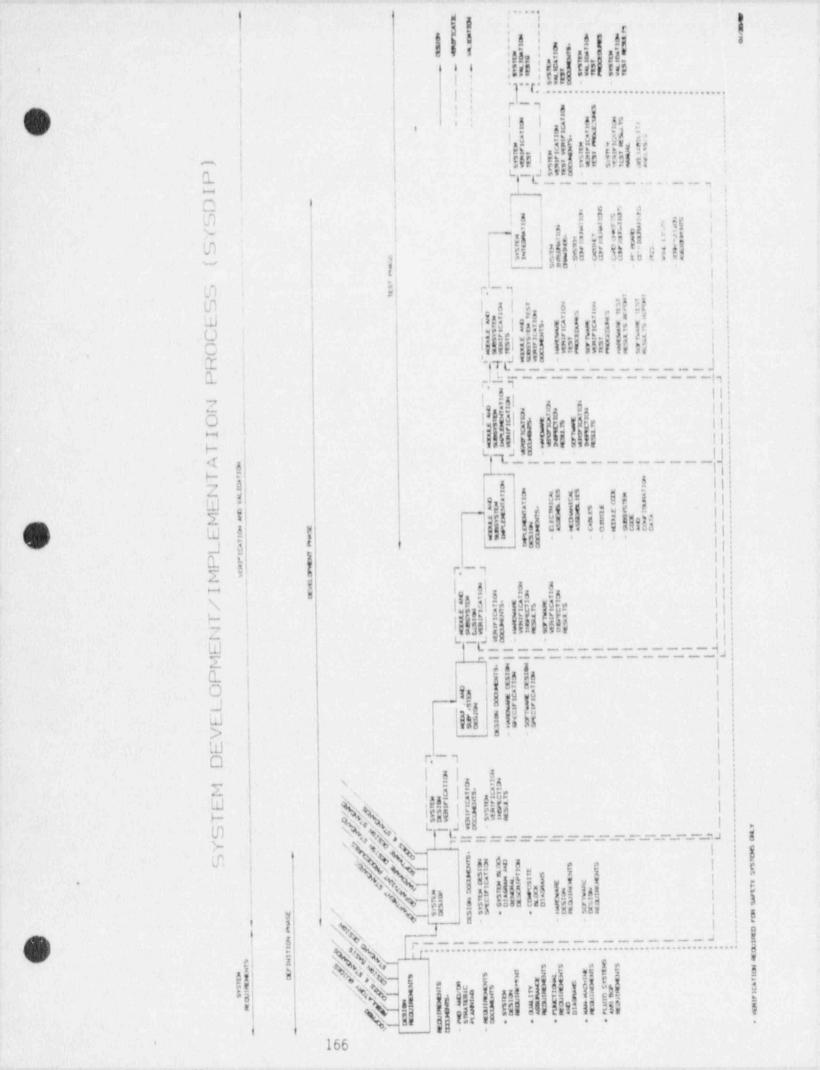

MR. ICHIYEN: What I thought I'd do is talk about 14 15 the high level standard and its features. As I said, this 16 will serve to highlight some of the principals that we feel 17 we are using in the future. The high level standard defines 18 the requirements on the software engineering process, 19 defines the outputs of that process. It defines the 20 requirements to be met by each output. What we try and do 23 is to specify this as measurable as possible, but, as I said 22 earlier, not necessarily to constrain the methodology to 23 produce the output.

[Slide.]

MR. ICHIYEN: In terms of fundamental principals

of this high level standard, I'm going to talk about five items. The first is the use of the documentation and the mathematical notation. We feel the documentation must describe the required behavior of the software using mathematical functions written in a notation that has clearly defined syntax and semantics.

7 We feel that using this kind of notation, you end up with more complete requirements. Since it's 8 9 mathematical, you can verify that the complete domain is covered and you can check it. Using mathematical notation, 10 11 as well, requirements can now be uniquely interpreted. Dr. Parnas uses this example of statements. One requirement 12 could be that you shut off the pumps if the water in the 13 14 tank is over the sctpoint for four seconds. In English, 15 that can be interpreted in any number of ways.

16 If you're the software developer, you have to say, 17 well, what does he mean; is that the roct mean square of the 18 level, the average level over the four second the median 19 of the level, when the minimum level is over for four 20 seconds. If you do it mathematically, there's do ambiguity. 21 You know what the requirement really is.

22 MR. WILKINS: Of course, you may not know that the 23 requirement is relevant.

24 MR. ICHIYEN: Yes. B t you could tell if it's 25 right or wrong.

MR. WILKINS: No. Whether it's been met.

2 MR. ICHIYEN: Other people can review it to see 3 whether it's also correct as stated. One of the problems in 4 the English language is that one person interprets it saying 5 that's right, that's what I understand it should be, but 6 that's not what the author meant and it may not be what the 7 software designer actually implemented.

Again, using mathematical notation facilitates use of mathematical verification techniques. That allows the design to be transformed into mathematical functions for comparison to the requirements directly. We've worked with this for quite a long time. Mainly Hydro we been doing a lot of this work.

We've got it to the point we think it's an actually doable task. We're at the point where we're about to start developing tools that will help us with this process.

18 MR. LEWIS: I hate to be a troublemaker, but I've 19 been counting pages. You have about ten minutes to go in 20 your allotted time.

21 MR. ICHIYEN: I may drop the Bruce fueling machine 22 thing. It's been published and talked about, I think, to 23 death and maybe you can ask me questions rather than my 24 talking about.

[Slide.]

25

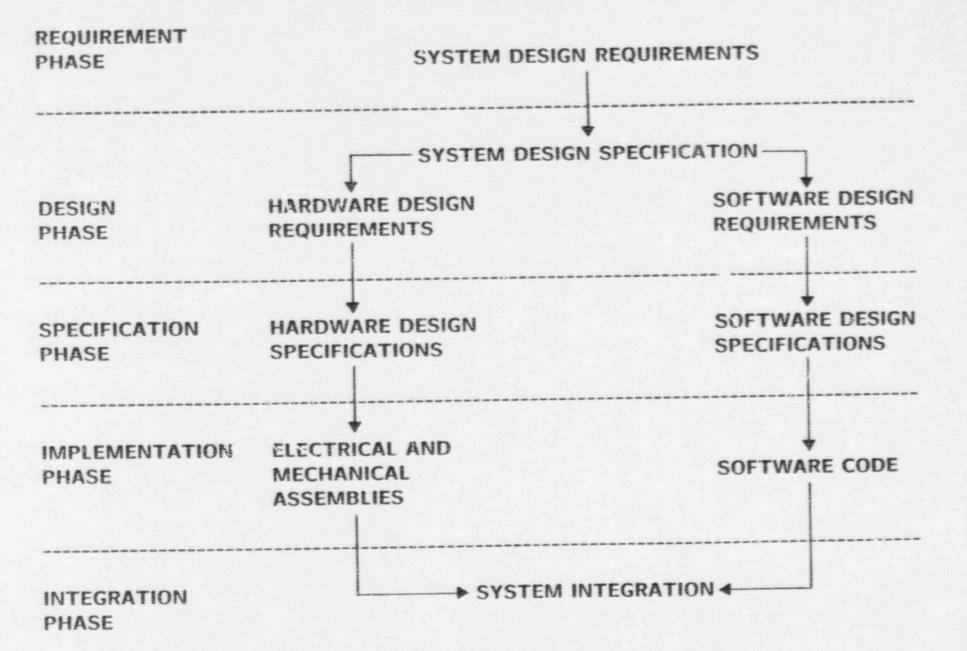

1 MR. ICHIYEN: The second fundamental principal is 2 that the outputs from each development process must be 3 reviewed to verify they comply with the requirements specified in the inputs to that process. What I mean by 4 5 that is if you think of the development process in three stages; the requirements specification, the software design, 6 and then the coding; the verification process is on each of 7 these outputs. 8

9 You verify that the outputs comply with the 10 requirements as specified on the inputs. Where you use 11 mathematical functions, you can verify these against the 12 inputs using mathematical verification techniques.

13

[Slide.]

14 MR. ICHIYEN: The third principal is on the use of information hiding. I won't go into that in a lot of 15 detail, other than to say that the -- really what it is, in 16 17 simple terms, is that we try and -- this is for the effort for maint inability. What you try and do is to assess what 18 19 areas in the code or things are likely to change over the history of operation and you use this as a guide to now you 20 do your software design into your modules and so on. 21

In addition, you try and design the interfaces to the modules, to reveal as little as possible about the modules' internal workings. This is, again, to help the maintenance aspect.

[Slide.]

1

2 MR. ICHIYEN: Along with the verification and the 3 specifications, we feel that in terms of testing you need to 4 do both systematic and random testing. By systematic 5 testing, the normal things that are done in the industry, 6 you characterize it as white box or black box testing. In 7 white box, you understand, you know what the int ... nal workings of the code are and you test based on that and try 8 and look at c scontinuities and so on. 9

Black box, you treat it as a black box where you don't know the workings of it. You check that the outputs match the requirements that are stated in the requirements. Thirdly, we want to add random testing. We call it statistically valid random testing, which is a contentious issue in the software area.

16 MR. CATTON: Is this a good place to ask the 17 hardware question again?

MR. ICHIYEN: Could you state that one again. MR. CATTON: There's a school of thought that says when you're dealing with embedded software systems, you have to test the system, which means software and hardware, if you want to come to some meaningful conclusion about its reliability.

24 I haven't seen you mention anything about hardware 25 yet.

MR. ICHIYEN: At least in the past for Darlington, we do the integration testing which is how you test the system as a whole. It isn't meant to be as exhaustive as the kinds of testing we do here. In the specifications, if you do the specification right, you're specifying what the computer system must do and then you break it into what the software must do.

8 If you do the verification right, then the 9 exhaustive testing is really on the software. That's where 10 we've been doing in the past.

MR. CATTON: I know that at NASA-Dreiden, they're very interested in taking one of the computers that's tied up with data evaluation and coupling the whole system together and putting -- trying to figure out what would be nice set signals to give it that are a little bit out of sync with what they should be to see how the whole system operates.

18 They actually have people trying to figure out 19 what would be a good set of inputs to really test the 20 system. This is not nearly as critical as your shutdown 21 system.

22 MR. ICHIYEN: When you say testirg the system, 23 meaning --

24 MR, CATTON: They have some hardware. Actually 25 it's from a pilot in the aircraft sending information to the

1 ground, processed by a computer, and there's a human being 2 in the middle. The information is sent back to the airplane 3 and the pilot has to take an action.

4 They're seriously trying to figure out how to test 5 that system in one piece.

6 MR. ICHIYEN: Maybe I need to describe the 7 configuration, because it's not a complicated configuration. 8 In fact, we are testing -- I hope I have a slide of it here.

9 MR. KERR: Ivan. could you restate your question? 10 I don't understand it.

MR. CATTON: I'm not sure I do either. The question half of do with esting the system, the software drive's hardware. Some people feel that if you're going to establish a reliability for this system that includes computer software, you have to look at the whole thing. They even have a name for it now. It's called embedded systems where the software --

18 MR. KERR: Given that that may be valid, is it 19 impossible c establish standards for software and establish 20 standards for the total system and test them separately?

21 MR. CATTON: Personally, I don't know, but some 22 people feel that you eventually have to do the test on the 23 whole system.

24 MR. KERR: I haven't heard him dispute that. But 25 he is not --

MR. CATTON: I don't know if he's going to dispute

it or not. I asked.

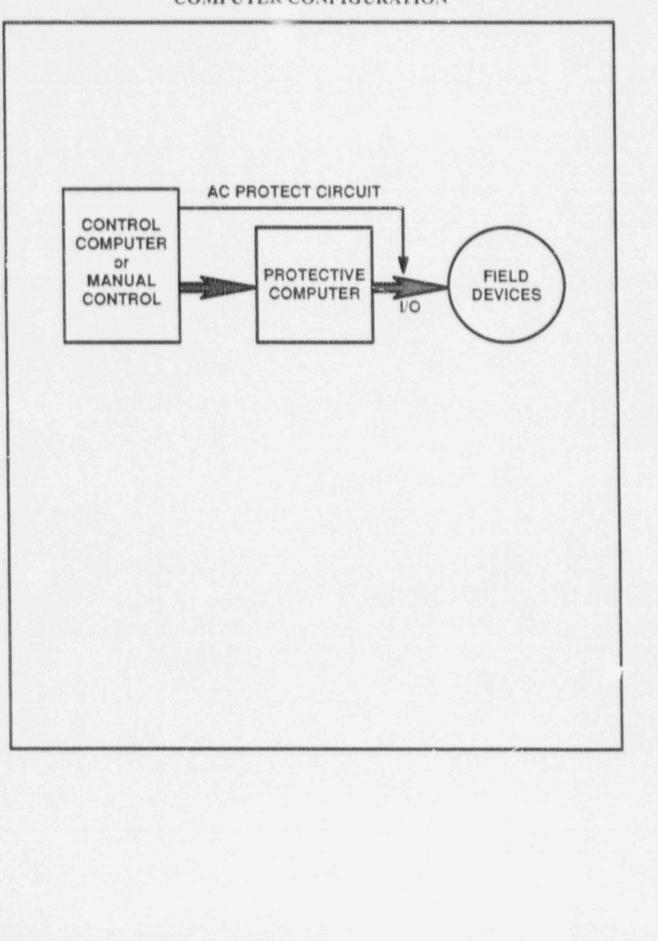

MR. ICHIYEN: I think you need to understand the configuration of it because it isn't a very complicated configuration. This is actually a fundamental principal we've tried to use on safety systems or safety critical systems. We make it as simple as possible.

[Slide.]

8

MR. ICHIYEN: These are what I call the safety 9 10 critical pieces of the boxes, which are the trip decision 11 functions. These are display computers which are used as the interface to the operator. What we do in testing is we 12 13 take this as a system. We know the inputs to it, we know 14 the outputs. We isolate that. We test that with varying degrees of testing. Software is done in smaller chunks than 15 16 unit testing, so on, building up to the random testing that I talked about, for example, would test this whole unit in a 17 18 random way.

Also, we do systematic tests. So I think, in essence, I am saying that we do test this aspect of it. We don't feel we need to test the whole system which is the operator interface, the displays on the monitor system, displays in the control room, to the same degree. We do test them, but to a lower level or higher level, depending on which way you're looking at it.

MR. CATTON: Thank you.

1

2

MR. ICHIYEN: I'll just move quickly to the last one. Another item that we feel is a fundamental principal in our safety critical software design is the use of huzard analysis. Again, I'm pointing this out because we feel that there's not just one technique that has to be used for safety critical software.

9 Hazard analysis is another tool in our tool chest 10 that we use to have a higher assurance of the quality of the 11 software. A simple definition of hazard analysis is that 12 you identify failure modes that lead to an unsafe action and 13 eliminate them or ensure the failure mode can be detected 14 and the system put into a safe state.

Dr. Nancy Levison, I guess, is the key proponent of this because she thinks she calls software fault tree analysis and I guess we've coined the term hazard analysis, and I think she probably uses the same term. She was hired by Ontario Hydro as a consultant during the Darlington licensing period. This is one of the extra features that she brought to the design process.

Basically what she's doing is using fault tree techniques that are used in hardware, applying them to software, looking for events, failure modes, and then seeing what things in the software have to happen in order that you

can mitigate that event.

In my mind, what it does is it gives you a more robustness to your software design as opposed to just meeting strict functional requirements.

MR. CATTON: I, today or actually last night on 45 the airplane, read the results of the workshop that I've 6 handed out here. They waintain that using the techniques 7 that you would for hardware, which usually means random 8 failure for software, is incorrect. Really what you ought 9 to do is go back and use the approach that there's a 10 possible design error, which is different, because if 11 there's something wrong with the software, it's a human 12 13 error somewhere, most likely. The answers you get out of it are different depending on the approach. 14

MR. ICHIYEN: It's identifying what are the others, and those are the key parts of any fault tree analysis. You don't have to identify how those failure modes can occur necessarily. What you try and do is to mitigate those occurrences.

20 MR. KERR: Ivan, under the theory of statistically 21 valid random testing slides that he has, there is a 22 distinction between at least a definition of reliability for 23 hardware and software.

24 MR. ICHIYEN: I skipped over those in the interest 25 of time. I don't know if you want me to go back.

MR. CATTON: I don't know if that statement I made was right. I just read it. I was looking for your response.

MR. LEWIS: We'll take a vote later about whether you're right, Ivan. But I am going to be brutal and try to wrap us up by 9:30 so we can keep on schedule.

[Slide.]

7

8 MR. ICHIYEN: In terms of overall status, as I 9 acid, the safety critical high level standard has just been 10 issued for use internally to AECL and Ontario Hydro. We 11 gian to have the sub-tier standards, procedures and 12 guidelines to be completed by the end of 1991.

13 The methodologies that we're using, safety 14 critical d configurations for systems, we're planning for 15 mid-1991 and that will probably be slipping till probably in 16 the fall. But it's in that order of magnitude in terms of 17 schedule. We're also working on other categories and 18 standards for those categories with really an undefined 19 closure date as yet.

20 MR. LEWIS: I'm going to thank you and assume that 21 we can skip talking about the Bruce incident in the interest 22 of staying on time. I know we would be very interested 'm 23 it and I know we would, therefore, spend at least a half-24 ...our on it. The best way to provent that is at the 25 beginning. Our purpose here today, I hope you understand

from our questioning, is not in any way to provide unwelcome

advice to our Canadian friends, but to learn from your

experience while we try to advise our American friends.

So I thank you very much for your presentation. It was very informative. I think we should just go on. I'm told that our next speaker is Ken Scarola, is that correct? MR. SCAROLA: That is correct.

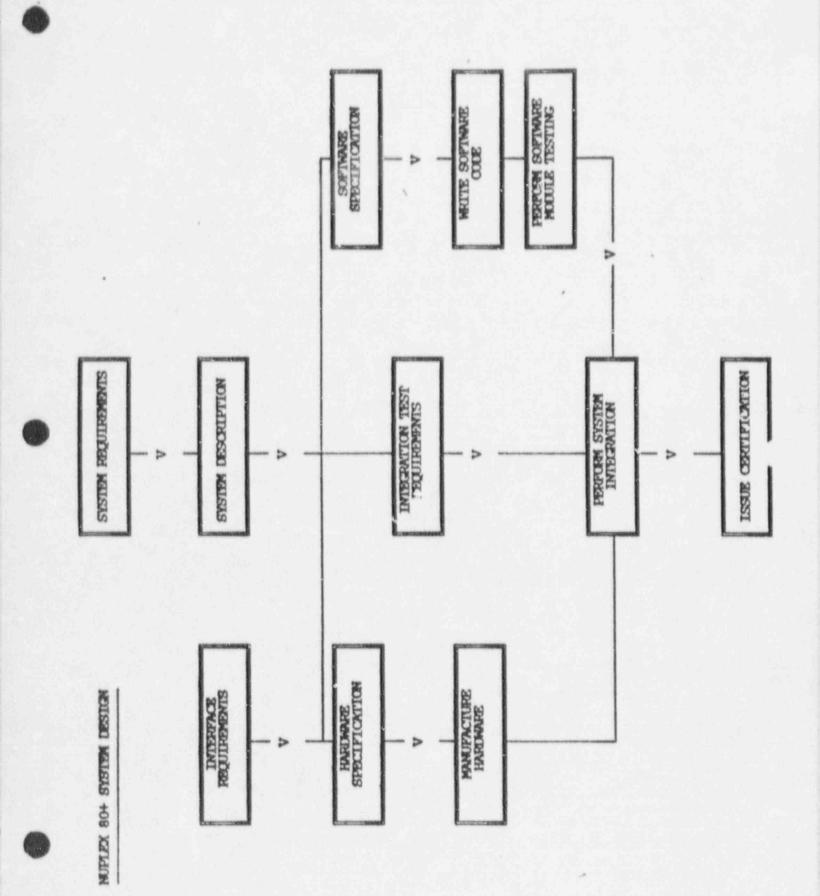

[Slide.]

8

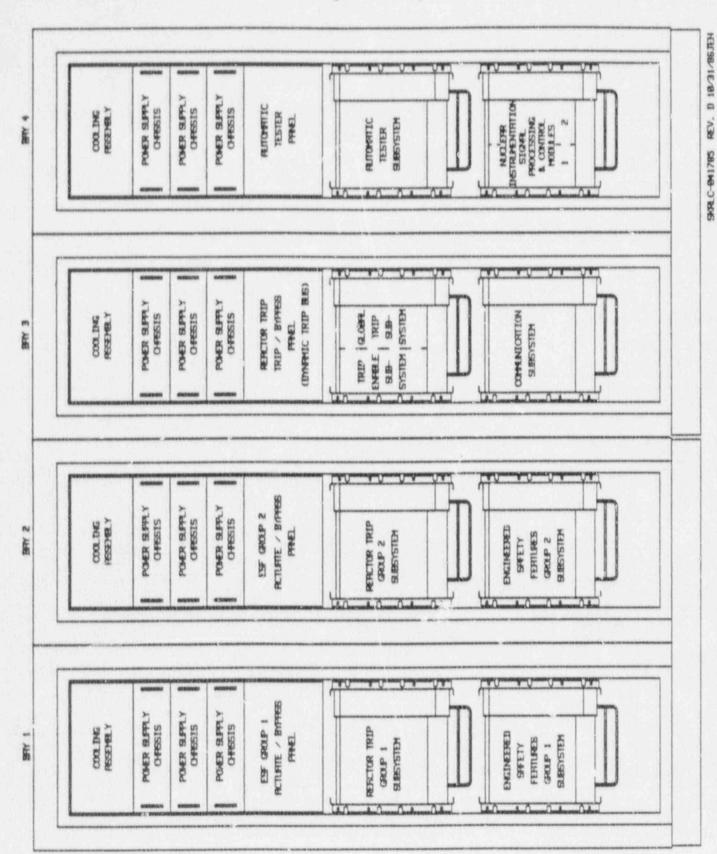

9 MR. SCAROLA: Good morning, gentlemen. My name is 10 Ken Scarola. I am the Manager of Advanced Control Complex 11 Engineering at ABB/Combustion Engineering. I'll be taiking 12 about software reliability issues for NUPLEX 80-Plus which 13 is the advanced control corplex being used by CE for the 14 System 80-Plus ALWR.

I might add that the NUPLEX 80-Plus advanced control complex is also being used for the heavy water reactor, NPR, at this point in time. To address very briefly what I heard about the relationship of hardware and software, I would say that CE would agree 100 percent that these are not separable issues. In fact, I think most of the industry does agree.

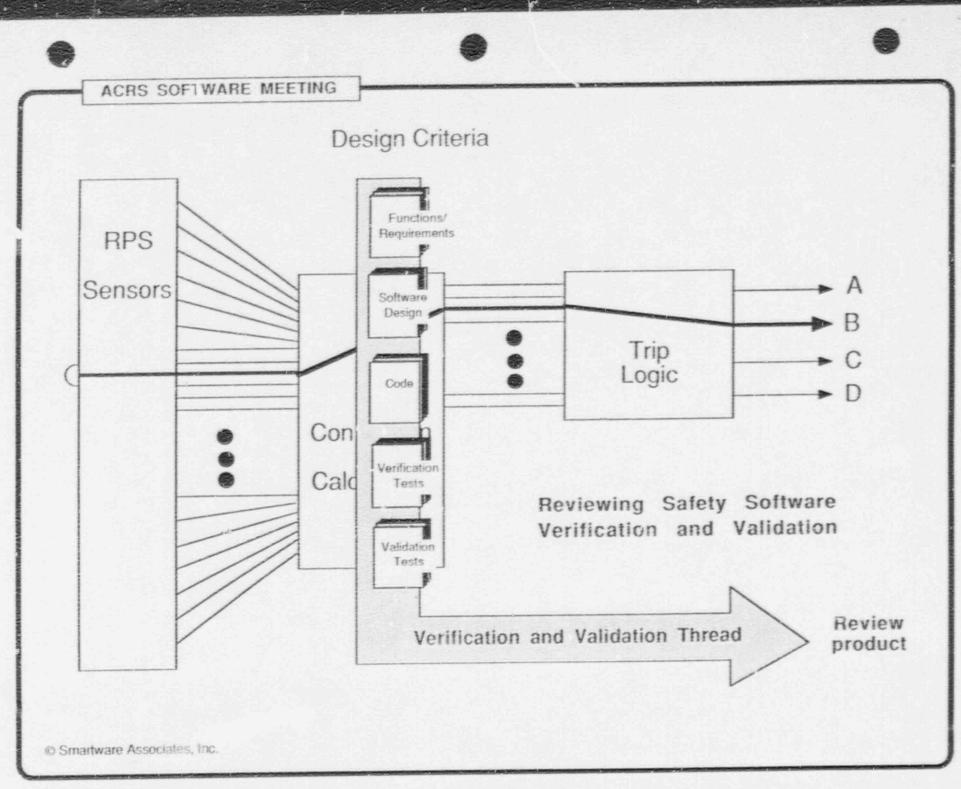

You will see, as I present our verification and validation approach, we definitely use V&V as an integrated process on a system basis and then an entire control complex basis. So these are definitely not separable issues.

MR. KERR: Does complex go with control or with engineering in that slide?

MR. SCAROLA: Good point. Probably both. What I'd like to do is address the issues that we believe are the main contributors to software reliability. There are numerous issues. Software reliability does not stand on any one particular issue. It's a building block defense-indepth approach and I think all things must be considered.

9 Certainly we talked about "tdware reliability 10 yesterday. What you're going to see in my slides is many of 11 those same points are now repeated here. In fact, I do have 12 some slides that I will throw in that may not be in your 13 handouts that I used yesterday and I will be at a to get you 14 copies of them.

15 Basically these are the software reliability issues that I will address. What I would like to do is 16 discuss CE's experience basically in between here before I 17 talk about the software design process. I'm going to 18 19 rearrange that from what's in your handout. That will help, 20 I think, set the framework for the software design process because it's based on our experience. Those slides are 21 22 misplaced.

[Slide.]

-3

24 MR. SCAROLA: The first subject that I would like 25 to talk about is what we call deterministic design. The

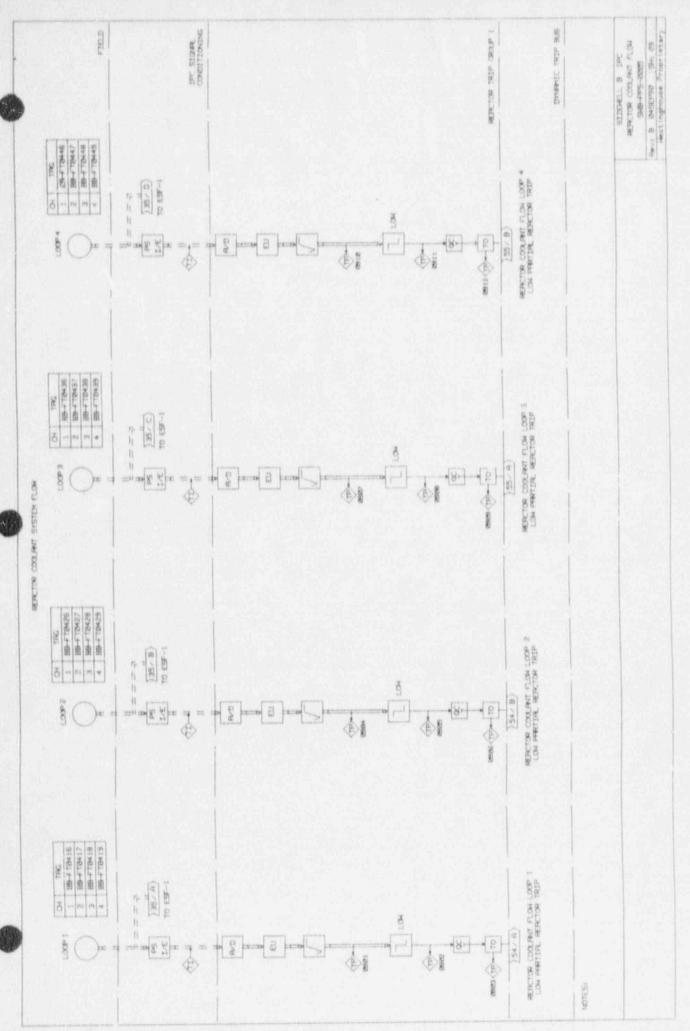

1 most important part of any software-based system is its 2 simplicity and your ability to prove that it works. When we 3 talk about computer-based systems, they range all over the 4 map. When we talk about systems for a 747 or something like 5 that, I would have to maintain that they are significantly 6 more complex than the types of software that we design for 7 nuclear power plant protection systems.

8 To give you an idea of what we mean by 9 deterministic designs, in our protection systems, the inputs 10 are scanned and processed continuously. There is nothing 11 like what you do in a complex system where you report data 12 changes by exception and then, when the particular data 13 changes, then you process it for that change. That's not 14 the case.

If. our protection systems, we look at the data with every cycle and, in our protection systems, we have less than a 50 millisecond cycle. That data is processed all the time. That's regardless of the state change of the data. Now, that can't be done in or it's difficult to do in very large complex computer systems because you cannot get the performance out of the system.

But if you look at a protection system for a nuclear power plant, and specifically CE's system, there are lo inputs. There is one output, reactor trip. That's not the case for things like DNBR and local power density, but

all of the other trips are, in fact, that simple. It's because of that simplicity that we can run the system on a continuous scan/continuous process basis. So there are no surprises when things change.

4

5 Similarly, the outputs are updated on a continuous 6 cycle. The outputs are not simply updated when the process 7 logic says they need to be. The outputs are always updated, 8 which means that in a protection system, 99.999 percent of 9 the time, the output is updated saying don't trip, don't 10 trip, don't trip.

11 On the one cycle when it doesn't get that update, 12 it trips. That's basically how the system works. Now, all 13 of the programs are run on a continuous basis, meaning there 14 is no multi-tasking as you would sea in most large computer 15 systems. The system does not run with interrupts. All the 16 data is processed on a continuous cycle basis.

Another important fact is where we use 17 18 programmable logic controllers, which is the fundamental 19 basic technology in our protection system, those machines run without branching, which means when they make a 20 decision, they don't go off and do something because of that 21 decision and then come back into the program. They make a 22 decision, they set a flag, the program continues on, and 23 some point later in the program on a continuous basis that 24 flag is recognized and something gets done because of that. 25

1 That's the inherent nature of programmable logic 2 controllers. That's not the inherent way most computers 3 run. Most computers run with branching, with sub-routines, 4 with calls, and you have to force them to run in a 5 deterministic nature. In our CPCs, we do that in CE's core 6 protection calculator because that is an inherently not 7 deterministic computer system.

8 So we have to write the code in a very structured 9 manner that forces it to run in a deterministic somewhat 10 non-branching type of approach. For the simple part of our 11 protection system where we look at analog variables, 12 pressurizer pressure, steam generator levels, we run non-13 branching.

14 MR. LEWIS: I'm really a little bit confused by 15 something here, a distinction you're making which appears to 16 be important, but which I don't understand. My computer at 17 home has a combination of software interrupts and hardware 18 interrupts. Hardware interrupts are branching interrupts, 19 in general, which simply tell the hardware to go off and do 20 something else, and to do something else may involve 21 returning to the original program or may not involve 22 returning to the original program, depending on the 23 character of the interrupt.

But it also has software interrupts which simply set a flag and the next scan time around to see if any

interrows have been activated. It notices whether they're there a switches off to another part of the program which may or may not involve a return to the main program, depending on what it is.

5 I don't see how that differs from what you're 6 describing.

7 MR. SCAROLA: It does in really two senses. First 8 of all, in your system, you're saying there are branches 9 where you may not return to the main program.

MR. LEWIS: Sure. That's dependent on how you write the program.

MR. SCAROLA: In our safety computer systems, that is not acceptable. Where we do branches, we always return to the same point in the program. It's what we call single entry/single exit of modules. That inherently makes the software more predictable that it's going to perform the required function when you want it to.

18 MR. LEWIS: I don't see that because it's 19 predictable either way. It depends on how you write the 20 software.

21 MR. SCAROLA: Not necessarily. When you branch 22 and the number of branches and the number of nests that may 23 occur in subsequent branches, these are the reasons why 24 software very often goes off and does unpredictable things. 25 It does things that you are not able to anticipate, like get

stuck in a loop somewhere.

1

MR. LEWIS: The Bruce event, which I didn't allow the previous speaker to describe, was a case in which, as I understand it, where what should have been a jump to a subroutine was instead written as an absolute jump, and that's what caused the problem. It would have been better if it had been written as a jump to a sub-routine and come back to the main program.

9 MR. SCAROLA: I think the point that I'm trying to 10 make here is that the structure of the code and the methods 11 that you use in coding are fundamental to the ability to 12 predict the performance of the system. I agree that you can 13 establish predictability in very complex systems. My point 14 is it's more difficult.

15 MR. LEWIS: In a sense, what you are saying is 16 you've made a decision that non-return branches are 17 inherently safer than return branches. Is that correct? 18 MR. SCAROLA: No. I'm saying that --19 MR. LEWIS: I'm trying to understand what you're 20 saying. 21 MR. SCAROLA: I'm saying the return branch is when 22 you branch and you return back to the same point in the

23 code.

24 MR. LEWIS: Yes.

2.5

MR. SCAROLA: That is inherently more predictable

4.8

performance than if you branch and subsequently branch again and subsequently branch again and may never return to the same point in the code.

MR. LEWIS: So I had it backwards. You've made a decision that only jumps to sub-routines which return to where they started are acceptable in your world.

7 MR. SCAROLA: Right. What I'm saying is that's 8 the approach that we take for complex calculations, such as 9 DNBR and local power density. For simple things, such as an 10 analog functional trip on low steam generator level, low 11 pressurizer pressure, the code works even more predictable 12 than that. What I have is a slide here that's not in your 13 package.

14

[S1\_de.]

MR. SCAROLA: This basically is a mapping of how 15 the software executes in our programmable logic controllers 16 17 independent of what the system inputs are doing, meaning the software follows this path every time. If you were to map 18 the software execution cycle of a conventional computer, you 19 would see that the mapping is all over the place. It zig-20 zags, it goes out, it comes back, it goes to many different 21 22 places.

A programmable logic controller inherently runs in

a deterministic cyclical manner. It never changes its

execution.

MR. LEWIS: Forgive me for being stupid, but I'm really trying to understand. It is your belief, then, that there is really no case in which it is preferable to leave the main program and never come back to it.

5 MR. SCAROLA: No. I can't say that, that is not 6 true.

MR. WILKINS: Let me try something.

MR. LEWIS: Go ahead. Try to explain.

MR. WILKINS: I don't operate quite at the level

of sophistication that these guys do, but on my computer

I've got a go-sub order, and that's okay. After the go-sub

order, you return. But go-to is not okay.

MR. LEWIS: I understand that.

25

14 MR. WILKINS: That's not what he's saying?

MR. LEWIS: I think that's what he's saying. In fact, that's nommon belief among computer scientists. In fact, when C was written, they originally didn't want to put the go-to into it. Now they've put it in, but they said it's strongly counter-productive.

I guess I'm asking -- there are, believe it or not, cases, using your analogy, in which go-to really is the right thing to do; that is, if you get a signal that tells you that the reactor has broken in half, you don't want to come back to the original program.

MR. SCAROLA: I'd like to move on and just point

out that the simplicity of the software execution is

important.

MR. LEWIS: That's certainly right. In fact --MR. SCAROLA: We can accept that and recognizing there are many ways to make the code simple, we have selected one that we think is the simplest approach. There are others. I'd like to leave it at that.

8 MR. LEWIS: I couldn't agree with you more. In 9 fact, what Ernest was saying, which was that the use of go-10 to is discouraged, is certainly gospel among modern computer 11 scientists. Good programming practice does not use go-to. 12 It uses modular systems, it uses predictable systems.

13 If what you're saying is that one should use good 14 software practices, then I have no problem at all.

MR. SCAROLA: Thank you.

16 [Slide.]

17 MR. SCAROLA: The second important contributor to software reliability is the use of field-proven executive 18 software. In NUPLEX 80-Plus, all of our software-based 19 20 systems are composed of off-the-shelf commercial products 21 with extensive field-proven industrial experience. Now, this includes programmable logic controllers, as I 22 23 mentioned. We do use PC ATs. There are minicomputers, CRT workstations, etcetera. 24

25

15

All of these systems are bought with executive

software, meaning software that has been in use in the field for handling things such as the input/output processing, the arithmetic functions, communication drivers, and failure detection inside the system itself.

5 This software is what you would call \_\_usable 6 code, a code that has extensive operating experience, 7 thousands of applications. So we attempt to use reusable 8 code as much as we possibly can because we believe that 9 field experience is the best validation source.

10

[Slide.]

MR. SCAROLA: Now I'd like to talk about CE's experience. CE has been designing software for safety systems since the mid-1970s, basically with the core protection calculator for ANO-2. That was our first experience. Since then we have put CPCs in all of our plants.

In addition to CPCs, we have done safety systems for monitoring, accident monitoring, safety parameter display and others. The thing I'd like to point out is that for the CPC ~ituation, we have had basically more than 800 software modifications, what we call software change requests, since the installation at ANO-2.

Ninety-nine percent of these software change

requests have been functional design changes, not software

errors, not software buys. These 99 percent are the types

of things that would show up in a hardware-based system as well as a software-based system because the root cause is the functional design process, not the implementation process.

5 We do a very good job of writing software to wrong 6 requirements. Software runs the way the wrong requirement 7 told it to run. The other point that I'd like to make is 8 that in all of the operational experience that we have with 9 the CPCs and where it did things that we didn't intend it to 10 do functionally, none of those have resulted in failure to 11 trip conditions. All of the software errors have been what 12 we would call spurious trip conditions.

13 The point that I'd like to make on this slide is -14 -

MR. KERR: Is that because you were clever in your design or was it just a fortuit to the circumstance?

MR. SCAROLA: No. I think it's inherent in the fail safe nature of the design. What we do is we force the system to go into a trip condition in any situation that you might call a system not knowing what it should do. So we force it to trip under any failure situation.

We have never had a situation where it would not trip.

24 MR. KERR: Thank you.

25 MR. LEWIS: When you say failure, you mean

software failure, is that right? When you said in any

failure situation.

MR. SCAROLA: Yes. I mean software failures in this slide. I would have to go back and research whether or not I could say that same thing about hardware failures, but I believe it's the same with hardware failures.

7 MR. LEWIS: Because the question of the Rancho 8 Seco event came up a little earlier and this was an example 9 of a place in which a failure in a power supply resulted in 10 not a software failure, but in incorrect inputs to the 11 software which then did what it was supposed to do, and 12 nearly brought on a really monumental accident.

13 MR. SCAROLA: I think that you're really 14 reemphasizing my point. We're looking at software as a 15 potential introduction of new failure modes into a system 16 when, in fact, the hardware relationship to software is 17 probably more dominant and the functional relationship is 18 more dominant.

MR. LEWIS: We don't disagree about that. Paul? MR. SHEWMON: With regard to the 99 percent functional design changes, not software, does that, again, reemphasize your point that it's the interaction of the hardware --

24 MR. SCAROLA: No. It's the interaction of the 25 functional designer to the system designer. In other words,

what I'm saying here is that 99 percent of these 826 changes

were functional design algorithm changes where we decided

that the algorithm was way too conservative and we had to

relax the requirements.

5 We were getting spurious trips in situations when 6 we should not be getting trips. So the root cause of these 7 changes are functional design changes, not software/hardware 8 coupling at all.

9 MR. SHEWMON: I guess that's too subtle for me to 10 see it.

MR. WILKINS: He's saying it's a setpoint.

MR. SCAROLA: Yes. Maybe spurious is the wrong word. What I'm saying is the algorithm executes, makes a decision that says you should scram. A functional designer went back, looked at that algorithm, did some analysis and said if we're really in that situation, we don't need to scram, so let's change the algorithm.

18 MR. CARROLL: Unnecessary scram.

11

MR. SCAROLA: Unnecessary would be a better word. Spurious is not the correct word, I'm sorry. That is the background. Let me say that in addition to safety system software, we have been designing software-based control systems. Our first installation was at SONGS. We have installations at LPNL and all subsequent plants beyond that. Some of them are extremely difficult installations

where we used software-based systems right next to the power supplies that run our mag jacks. So when we talk about harsh EMI environments and the effect of EMI on hardware and software-base systems, we have extensive experience there, as well.

1

3

4

5

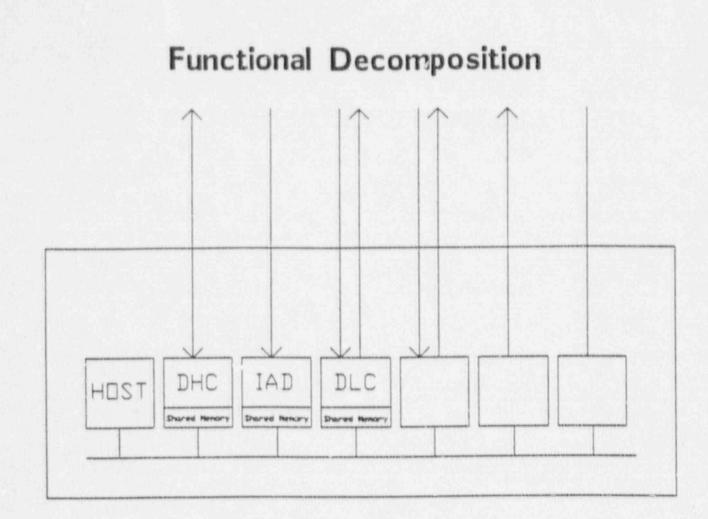

6 Now I'd like to talk for a minute about the 7 software design process and the software documentation 8 process that we use. First of all, as emphasized on the 9 slide before, we need an early focus on establishing what 10 would be really correct requirements and specifications. I 11 think this is a problem that's recognized by the industry as 12 the biggest contributor to the bad name that software has 13 gotten in the industry.

14 It's not that the people who write software do it 15 wrong, it's that the people who establish the requirements 16 don't do it correctly. So we put a lot of emphasis on the 17 requirements for the system both from a hardware and 18 software point of view and what we call functional 15 decomposition point of view. We decompose the functions 20 down into small units so they're very understandable and 21 manageable on a module basis.

We use standard coding and documentation techniques, things like deterministic coding. We have software standards, guides that tell the programmers what they can do when they program and what they are not allowed

1

2

3

4

5

to do, like going off in a branch and not returning.

MR. KERR: I guess I don't understand the relationship between the first bullet and those two things that follow it. The first bullet seems to say that correct requirements and specs weren't -- and then the second one --

6 MR. SCAROLA: What I'm trying to say is we 7 establish functional requirements for a system, and I'll 8 show it better on the next slide. Why don't I get through 9 this slide, and then I'll show it better on the next one. 10 Then we have a verification and validation program that I'll 11 spend more time on, and then, lastly, extensive 12 configuration control over the life of the product.

For example, I showed you on the CPCs, we track every CPC modification on every plant. That applies to both the purchased software -- when we buy an executive system, we know the rev of that executive system and we follow any modifications that the original designer of that software makes.

MR. KERR: That doesn't apply to your CPCsoftware, I presume.

21 MR. SCAROLA: It does apply for CPC software. I'm 22 sorry. Maybe you should ask your question again.

23 MR. KERR: I got the impression that you had 24 developed your CPC software and it wasn't off-the-shelf 25 purchased.

1 MR. SCAROLA: Yes. Excuse me. I answered the 2 wrong question. CPC is not purchased software. CPC is CE 3 custom software.

4

16

[Slide.]