SUMMARY OF THE WESTINGHOUSE INTEGRATED PROTECTION SYSTEM VERIFICATION AND VALIDATION PROGRAM

B. M. Cook

D. V. Gennaro

W. J. Smith, Jr.

M. S. Wojcik

September, 1980

Approved:

T. M. Anderson, Manager Nuclear Safety Division

Westinghouse Electric Corporation

P. O. Box 355

Pittsburgh, PA 15230

The Integrated Protection System (IPS) Prototype Verification and Validation Program was a coordinated program that demonstrated that the design objectives of the IPS as described in RESAR 414 were met. Definition of the design objectives and verification program were provided in WCAP-9153, "414 Integrated Protection System Prototype Verification Program," August 1977. WCAP-9153 was organized into two major parts: design principles and the verification program. These two major parts were further subdivided to cover design and verification of the hardware, software and the integrated system.

This document presents a summary of what the verification and validation program covered in terms of hardware, software and the integrated system. It also is representative of what the NRC/ORNL reviewed by the technical audit process.

#### ACKNOWLEDGEMENTS

Westinghouse Nuclear Technology Division and Industry Systems Division joined in meeting the Westinghouse commitments to the Integrated Protection System Design Verification Program. Successful completion of this verification and validation process resulted directly from the close cooperation and fire efforts extended by the engineers, technicians, and support personnel of both divisions.

# TABLE OF CONTENTS

|     |              |                                                  |                                             | Page |

|-----|--------------|--------------------------------------------------|---------------------------------------------|------|

|     | ABSTR        | ACT                                              |                                             |      |

| 1.0 | INTRODUCTION |                                                  |                                             | 1-1  |

|     | 1.1          | Program                                          | Management                                  |      |

|     | 1.2          | Sof twar                                         | e Design and Verification                   |      |

|     | 1.3          | Hardwar                                          | e Design and Verification                   |      |

|     | 1.4          | System                                           | Integration and Validation                  |      |

|     | 1.5          | NRC Rev                                          | iew by Audits                               |      |

|     | 1.6          | Ongoing                                          | Effort                                      |      |

| 2.0 | INTE         | GRATED SY                                        | STEM VERIFICATION SUMMARY                   | 2-1  |

|     | 2.1          | Methodo                                          | ology of Integrated System Verification     |      |

|     |              | 2.1.1                                            | Test Methodology                            |      |

|     |              | 2.1.2                                            | Test Cases                                  |      |

|     |              | 2.1.3                                            | Input Signals                               |      |

|     |              | 2.1.4                                            | Conclusion                                  |      |

|     | 2.2          | Prerequ                                          | uisite Integrated System Verification Tests |      |

|     |              | 2.2.1                                            | Preliminary Tests                           |      |

|     |              | 2.2.2                                            | Stage 1 Testing                             |      |

|     |              | 2.2.3                                            | Stage 2 Testing                             |      |

|     |              | 2.2.4                                            | System Verification Error Report Summary    |      |

|     | 2.3          | Integrated Protection System Simulated Transient |                                             |      |

|     |              | Test                                             |                                             |      |

|     |              | 2.3.1                                            | Introduction                                |      |

|     |              | 2.3.2                                            | Test Case Generation                        |      |

|     |              | 2.3.3                                            | Acceptance Criteria                         |      |

|     |              | 2.3.4                                            | Transient Test Execution                    |      |

|     |              | 2.3.5                                            | Test Results                                |      |

|     |              |                                                  |                                             |      |

|     |      |                                               | Page |  |

|-----|------|-----------------------------------------------|------|--|

| 3.0 | SYST | EM DESIGN SPECIFICATIONS SUMMARY              | 3-1  |  |

|     | 3.1  | Equipment Specification (E-Spec)              |      |  |

|     | 3.2  |                                               |      |  |

|     |      | Composite Block Diagrams                      |      |  |

|     |      | 3.3.1 Integrated Protection Cabinets (IPC)    |      |  |

|     |      | 3.3.2 Integrated Logic Cabinets (ILC)         |      |  |

|     |      | 3.3.3 ILC Interposing Logic & Power Interface |      |  |

|     | 3.4  | IPS Module List & Spec Sheets                 |      |  |

|     | 3.5  | IPS Software Standard                         |      |  |

|     | 3.6  | IPS Automatic Testing Requirements            |      |  |

|     | 3.7  | IPS System Test Guidelines                    |      |  |

|     | 3.8  | References                                    |      |  |

| 4.0 | HARD | WARE VERIFICATION SUMMARY                     |      |  |

|     | 4.1  | Hardware Verified                             |      |  |

|     | 4.2  | Hardware Test Results/Error Incident Reports  |      |  |

|     | 4.3  | QAC Analog Conditioning Card                  |      |  |

|     |      | 4.3.1 QAC Equipment Performance Specification |      |  |

|     |      | DS1177 (EPS) Summary Description              |      |  |

|     |      | 4.3.2 QAC Product Verification Test Procedure |      |  |

|     |      | 6821A68 (PVTP) Summary Description            |      |  |

|     | 4.4  | QAO Analog Output Card                        |      |  |

|     |      | 4.1.1 QAO EPS DS1165 Summary Description      |      |  |

|     |      | 4.4.2 QAO PVTP 6821A62 Summary Description    |      |  |

|     | 4.5  | QA1 Analog Input Point Card                   |      |  |

|     |      | 4.5.1 QAI EPS DS1122 Summary Description      |      |  |

|     |      | 4.5.2 QAI PVTP 6821A60 Summary Description    |      |  |

|     | 4.6  | QBI Digital Input Card                        |      |  |

|     |      | 4.6.1 QBI EPS DS1175 Summary Description      |      |  |

|     |      | 4.6.2 QBI PVTP 6821A60 Summary Description    |      |  |

- 4.7 QBO -- Digital Output Card

- 4.7.1 QBO EPS DS1174 Summary Description

- 4.7.2 QBO PVTP 6821A64 Summary Description

- 4.8 QCI -- Contact Input Card

- 4.8.1 OCI EPS DS1189 Summary Description

- 4.8.2 QCI PVTP 6921A69 Summary Description

- 4.9 QDI -- Digital Input Card

- 4.9.1 QDI EPS DS1141 Summary Description

- 4.9.2 QDI PVTP 6821A70 Summary Description

- 4.10 OMC -- Microcomputer Card

- 4.10.1 QMC EPS DS1139 Summary Description

- 4.10.2 QMC PVTP 6822A39 Summary Description

- 4.11 QMD -- Data Link Controller Card

- 4.11.1 QMD EPS DS1173 Summary Description

- 4.11.2 QMD PVTP 6822A41 Summary Description

- 4.12 QME -- Memory Extender Card

- 4.12.1 QME EPS DS1166 Summary Description

- 4.12.2 OME PVTP 6822A40 Summary Description

- 4.13 QMS -- Two Port Shared Memory Card

- 4.13.1 QMS EPS DS1179 Summary Description

- 4.13.2 QMS PVTP 6822A42 Summary Description

- 4.14 QPD, QPP -- Q-Line Crate Paddle Card

- 4.14.1 QPD, QPP EPS DS1218 Summary Description

- 4.14.2 QPD, QPP PVTP 7601A73 Summary Description

- 4.15 QTB -- Time Base Card

- 4.15.1 QTB EPS DS1248 Summary Description

- 4.15.2 QTB PVTP 6821A61 Summary Description

- 4.16 NAI -- Annunciator Interface Card

- 4.16.1 NAI EPS DS1073 Summary Description

- 4.16.2 NAI PVTP Summary Description

- 4.17 NAC -- Analog Comparator Card

- 4.17.1 NAC EPS DS1102 Summary Description

- 4.17.2 NAC PVTP VR-76 Summary Description

4.18 NCI -- Input Card 4.18.1 NCI EPS DS1071 Summary Description 4.18.2 NCI PVTP VR-71 Summary Description 4.19 NCP -- Reactor Coolant Pump Speed Card 4.19.1 NCP EPS DS1188 Summary Description 4.19.2 NCP PVTP 6822A37 Summary Description 4.20 NDC -- Contact Input Card 4.20.1 NDC EPS DS1196 Summary Description 4.20.2 NDC PVTP 6821A79 Summary Description 4.21 NIL -- Integrated Logic Card 4.21.1 NIL EPS DS1128 Summary Description 4.21.2 NIL PVTP 6822A38 Summary Description 4.22 NMA -- Analog Mixing Amplifier Card 4.22.1 NMA EPS DS1104 Summary Description 4.22.2 NMA PVTP VR-67 Summary Description 4.23 NMO -- Momentary Output Card 4.23.1 NMO EPS DS1194 Summary Description 4.23.2 NMO PVTP 6821A77 Summary Description 4.24 NQO -- Quad Output Card 4.24.1 NOO EPS DS1187 Summary Description 4.24.2 NOO PVTP Summary Description 4.25 NQP -- Quad Loop Power Supply Card NOP EPS DS11005 Summary Description 4.25.1 4.25.2 NOP PVTP VR-50 Summary Description 4.26 NQT -- Quad Output Card 4.26.1 NOT EPS DS1184 Summary Description 4.26.2 NQT PVTP 6821A78 Summary Description 4.27 NRA -- Resistance Temperature Detector (RTD) Amplifier Card 4.27.1 NRA EPS DS1017 Summary Description 4.27.2 NRA PVTP VR-60 Summary Description

4.28 NTB -- Breaker Trip Bypass Card

4.28.1 NTB EPS DS1207 Summary Description

4.28.2 NTB PVTP 6821A75 Summary Description

- 4.29 NTL -- Breaker Trip Logic Card

- 4.29.1 NTL EPS DS1202 Summary Description

- 4.29.2 NTL PVTP 6821A76 Summary Description

- 4.30 M-BUS

- 4.30.1 M-BUS EPS DS1243 Summary Description

- 4.30.2 M-BUS PVTP Summary Description

- 4.31 UIOB -- Universal Input/Output Bus

- 4.31.1 UIOB EPS DS1144 Summary Description

- 4.31.2 UIOB PVTP Summary Description

- 4.32 Q-Line/7300 Series Power Supply

- 4.32.1 EPS DS1203 Summary Description

- 4.32.2 PVTP Summary Description

- 4.33 Source Range Module (SRM)

- 4.33.1 SRM SKRMP80177 Equipment Summary Description

- 4.33.2 SRM T-925870 Test Summary Description

- 4.34 Intermediate Range Module (IRM)

- 4.34.1 IRM SKRMP80177 Equipment Summary Description

- 4.34.2 IRM 2383A66 Test Summary Description

- 4.35 Power Range Module (PRM)

- 4.35.1 PRM SKRMP80177 Equipment Summary Description

- 4.35.2 PRM 2383A67 Test Summary Description

- 4.36 N-16 Power Monitor Module

- 4.36.1 N-16 SKRMP80177 Equipment Summary

Description

- 4.36.2 N-16 T-925871 Test Summary Description

- 4.37 Source Range Preamplifier (SRP)

- 4.37.1 SRP SKRMP80177 Equipment Summary Description

- 4.37.2 SRP T-925870 Test Summary Description

- 4.38 High Voltage Power Supply Module (HVPSM)

- 4.38.1 HVPSM SKRMP80177 Equipment Summary Description

- 4.38.2 HVPSM 2383A47 Test Summary Description

- 4.39 Safety Grade Digital Rod Position Indicator (SGRPI)

- 4.39.1 SGRPI ES-953230 Equipment Summary Description

- 4.39.2 SGRPI T-925873 Test Summary Description

Page

| .0 | SOFT                                                                    | WARE VER                                                                     | IFICATION SUMMARY                      |     |  |  |  |  |

|----|-------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------|-----|--|--|--|--|

|    | 5.1                                                                     | Software                                                                     | e Verified                             | 5-1 |  |  |  |  |

|    |                                                                         | 100000                                                                       | Test Results/Error Incident Reports    |     |  |  |  |  |

|    |                                                                         |                                                                              | Support Modules                        |     |  |  |  |  |

|    |                                                                         | 5.3.1                                                                        | Software Performance Specifications    |     |  |  |  |  |

|    |                                                                         |                                                                              | (SPS)-0001-0063 Summary Description    |     |  |  |  |  |

|    |                                                                         | 5.3.2                                                                        | 이 사이를 하게 하시네요 생각하게 되었습니다.              |     |  |  |  |  |

|    |                                                                         |                                                                              | (STS)-0001-0063 Summary Description    |     |  |  |  |  |

|    | 5.4                                                                     | Nuclear                                                                      | Instrumentation Partrial Trips Process |     |  |  |  |  |

|    |                                                                         |                                                                              | SPS-0100 Summary Description           |     |  |  |  |  |

|    |                                                                         | 5.4.2                                                                        |                                        |     |  |  |  |  |

|    | 5.5                                                                     | Departure From Nucleate Boiling (DNB) and<br>Kilowatt Per Foot (KW/FT) Trips |                                        |     |  |  |  |  |

|    |                                                                         | 5.5.1                                                                        | SPS-0200 Summary Description           |     |  |  |  |  |

|    |                                                                         | 5.5.2                                                                        | STS-0200 Summary Description           |     |  |  |  |  |

|    | 5.6                                                                     | 5.6 Engineered Safety Features (ESF) Partial Trips                           |                                        |     |  |  |  |  |

|    |                                                                         | 5.6.1                                                                        | SPS-0300 Summary Description           |     |  |  |  |  |

|    |                                                                         |                                                                              | STS-0300 Summary Description           |     |  |  |  |  |

|    | 5.7 Trip Logic Computer, Global Trip and Trip Enable Process            |                                                                              |                                        |     |  |  |  |  |

|    |                                                                         | 5.7.1                                                                        | SPS-0400-0402 Summary Description      |     |  |  |  |  |

|    |                                                                         | 5.7.2                                                                        | STS-0401, 0402 Summary Description     |     |  |  |  |  |

|    | 5.8                                                                     | Data Li                                                                      | Data Link Controller Process           |     |  |  |  |  |

|    |                                                                         | 5.8.1                                                                        | SPS-0500 Summary Description           |     |  |  |  |  |

|    |                                                                         | 5.8.2                                                                        | STS-0500 Summary Description           |     |  |  |  |  |

|    | 5.9 Integrated Protection Cabinet Communications Bus Controller Process |                                                                              |                                        |     |  |  |  |  |

|    |                                                                         | 5.9.1                                                                        | SPS-0600 Summary Description           |     |  |  |  |  |

|    |                                                                         | 502                                                                          | STS_0600 Summary Description           |     |  |  |  |  |

|      |                                                       |             |               |                |     | Pag |

|------|-------------------------------------------------------|-------------|---------------|----------------|-----|-----|

| 5.10 | Integrati                                             |             | ion Cabinet   | Automatic      |     |     |

|      |                                                       |             | Summary Desc  | ription        |     |     |

|      |                                                       |             | Summary Desc  |                |     |     |

| E 11 |                                                       |             |               |                |     |     |

| 2.11 | 11 Integrated Logic Cabinet 2/4 Bypass Voting Process |             |               |                |     |     |

|      |                                                       | SPS-0800 S  | Summary Desc  | ription        |     |     |

|      | 5.11.2                                                | STS-0800 S  | Summary Desc  | ription        |     |     |

| 5.12 | Integrat                                              | ed Logic Ca | abinet Autom  | atic Tester    |     |     |

|      | Process                                               |             |               |                |     |     |

|      | 5.12.1                                                | SPS-0900 S  | Summary Desc  | ription        |     |     |

|      | 5.12.2                                                | STS-0900 S  | Summary Desc  | ription        |     |     |

| 5.13 | Main Con                                              | trol Board  | /Integrated   | Logic Cabinet  |     |     |

|      | Multiple                                              |             |               |                |     |     |

|      |                                                       |             |               | Description    |     |     |

|      |                                                       |             |               | Description    |     |     |

| 5.14 |                                                       |             | nal Selection |                |     |     |

|      | 5.15.1                                                | SPS-1100-   | 1102 Summary  | Description    |     |     |

|      | 5.14.2                                                | STS-1100-   | 1102 Summary  | y Description  |     |     |

| 4005 | NDIV                                                  |             |               |                |     | 6-  |

|      | NDIX                                                  |             |               | (NDC) (Oak D4) | dan |     |

|      |                                                       |             |               | (NRC)/Oak Ric  |     |     |

|      | onal Laboratories (ORNL) Technical audit reports      |             |               |                |     |     |

|      |                                                       |             | line Design   |                |     |     |

| 6.3  | Definiti                                              | on of Acro  | onyms and Abb | breviations    |     |     |

|      |                                                       |             |               |                |     |     |

6.0

#### 1.0 INTRODUCTION

Westinghouse has designed an Integrated Protection System (IPS) which is based on distributed digital processing technology. This design effort was conducted in compliance with accepted industry and regulatory standards and practices. The design bases for the IPS have been presented to the NRC in RESAR-414, which received a Preliminary Design Approval (PDA) in November of 1978.

As a condition of the PDA, the NRC required that Westinghouse prove the design of the IPS by submitting it to a verification and validation program. Westinghouse's response to this condition is contained in report WCAP-9513, "414 Integrated Protection System Prototype Verification Program". This report, issued in August of 1977, was organized into two major parts which established the design principles and the verification program that was used during the development, test and operation phases of the prototype model. Design principles sections were included for the prototype system, as well as its software and hardware. Items such as program administration, documentation, design and development, and verification principles were addressed in these sections. The discussions of the verification program were also similarly arranged for the prototype system, and its software and hardware. Items included within these sections were the program administration, verification methods, documentation, and acceptance criteria.

In order to conduct this verification and validation program, Westinghouse built a prototype of the IPS which consists of one complete channel set of equipment. All inputs from the field, control board and other channel sets are simulated as are the output loads of the system. The verification and validation program consisted of a series of inspections and tests, performed first on the individual hardware and software modules, then on subsystems. Finally, system level tests were performed on the entire IPS prototype, to verify the correctness of its design. This report describes the results of that verification and validation program. An audit program, by which the NRC reviewed this verification and validation program is also described.

### 1.1 PROGRAM MANAGEMENT

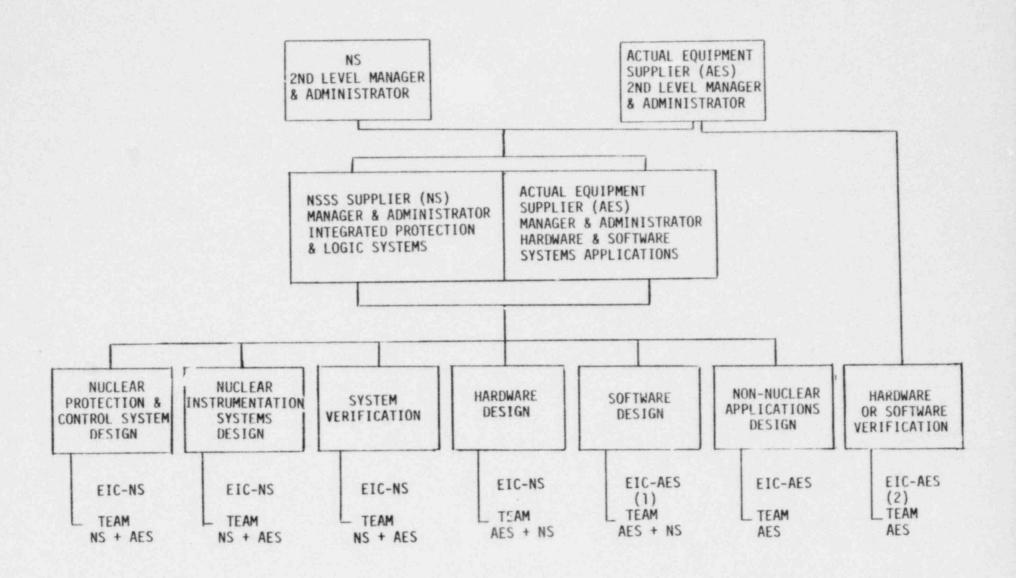

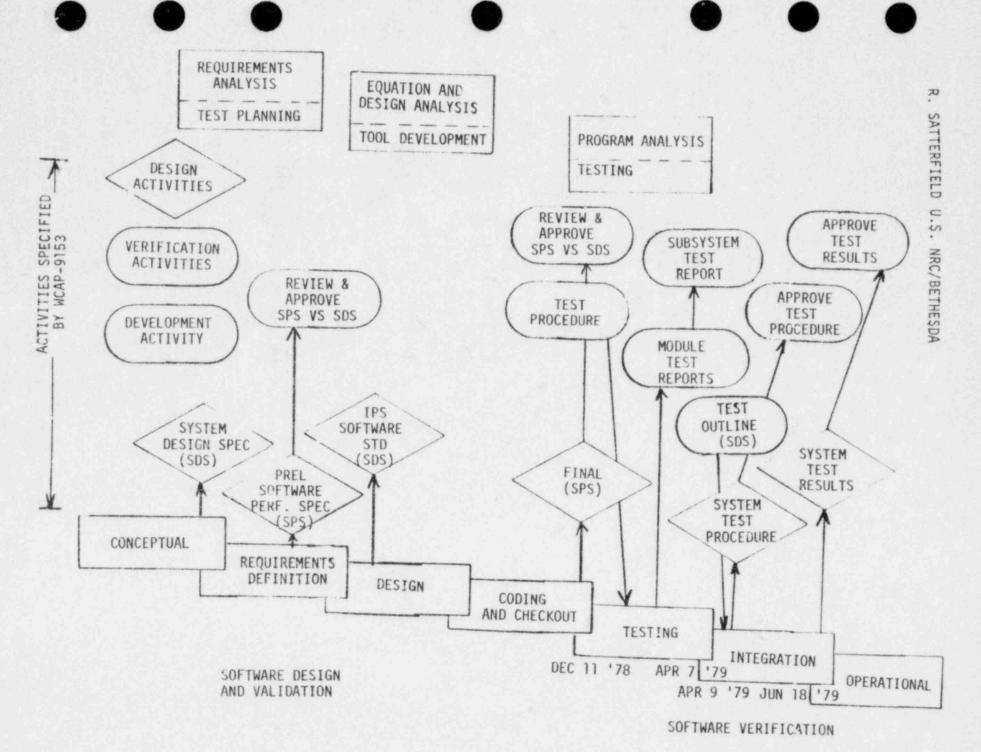

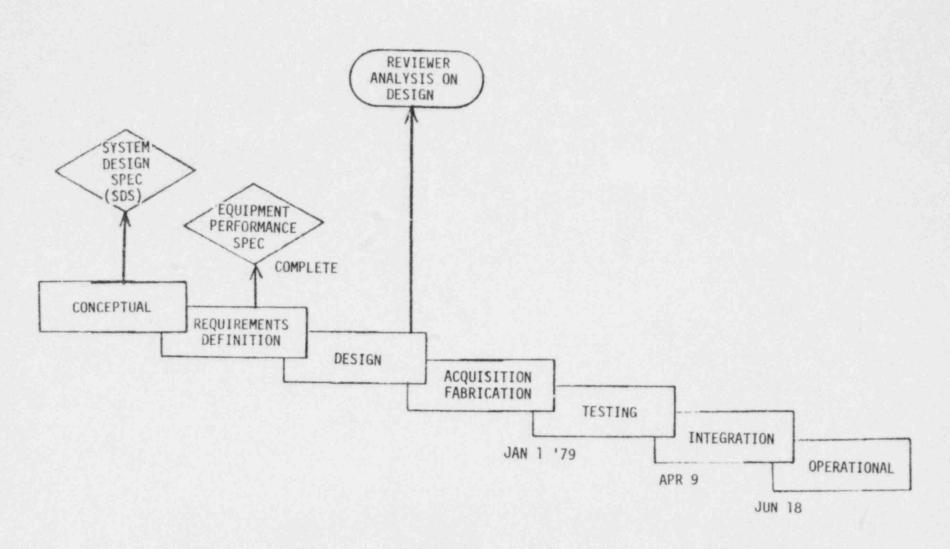

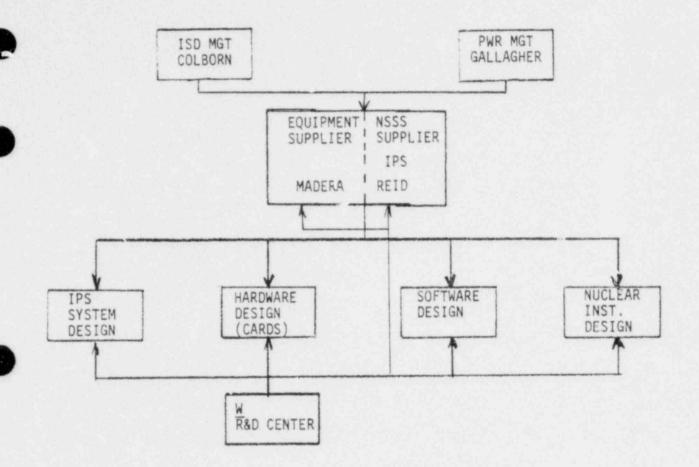

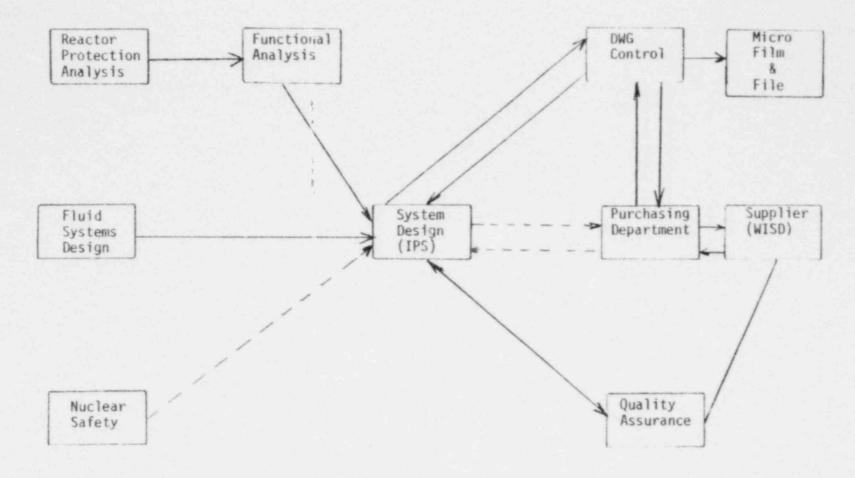

The verification of the IPS prototype was conducted in such a manner to assure independence of the design and verification processes. The management organization of the program is shown in Figure 1-1 which shows that two Westinghouse divisions were involved, Nuclear Steam Supply System supplier (NS) and the Actual Equipment Supplier (AES).

The NS provided the System Design Specification to the AES who produced the detailed system design documentation. These detailed documents, which consisted of schematic diagrams, Equipment Performance Specifications and Software Performance Specifications, were developed from the System Design Specifications and were reviewed and approved by the NS to verify consistent of the system design.

At the AES facility, the design and verification effort was divided among distinct teams -- hardware and software design teams and hardware and software verification teams. After the hardware and software were designed and verified, they were integrated into the system where the overall system design was validated by testing. This testing was performed according to procedures written by the AES and approved by the NS, the responsibility for final approval of the system test results being the NS division.

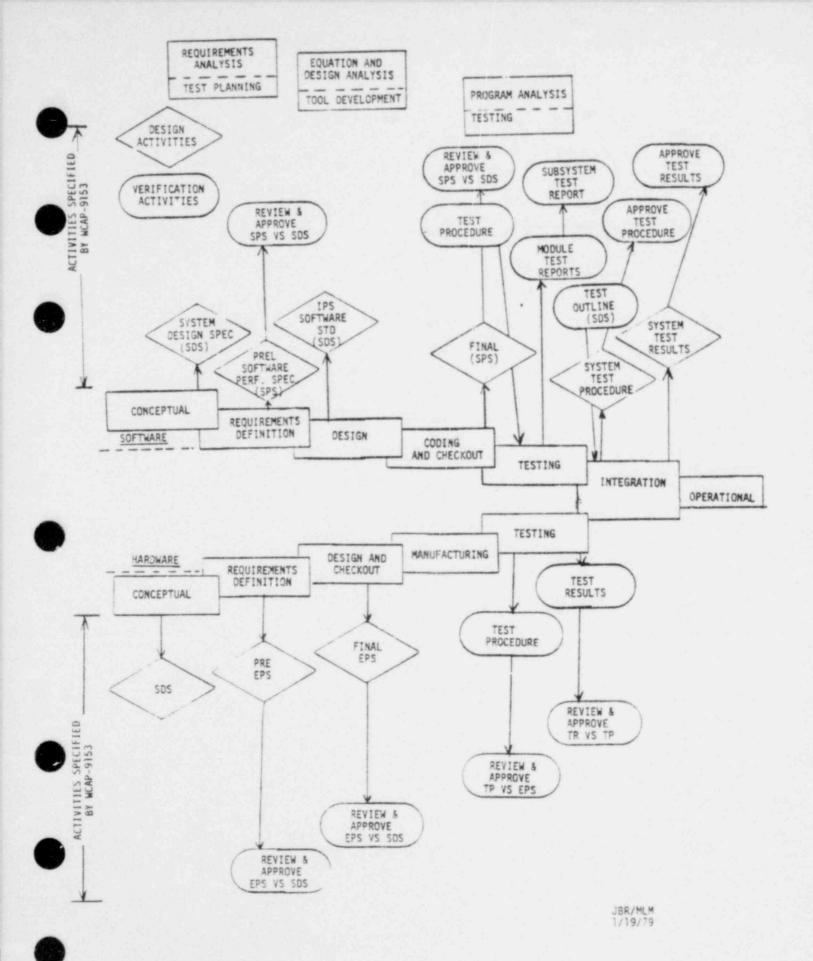

# 1.2 SOFTWARE DESIGN & VERIFICATION

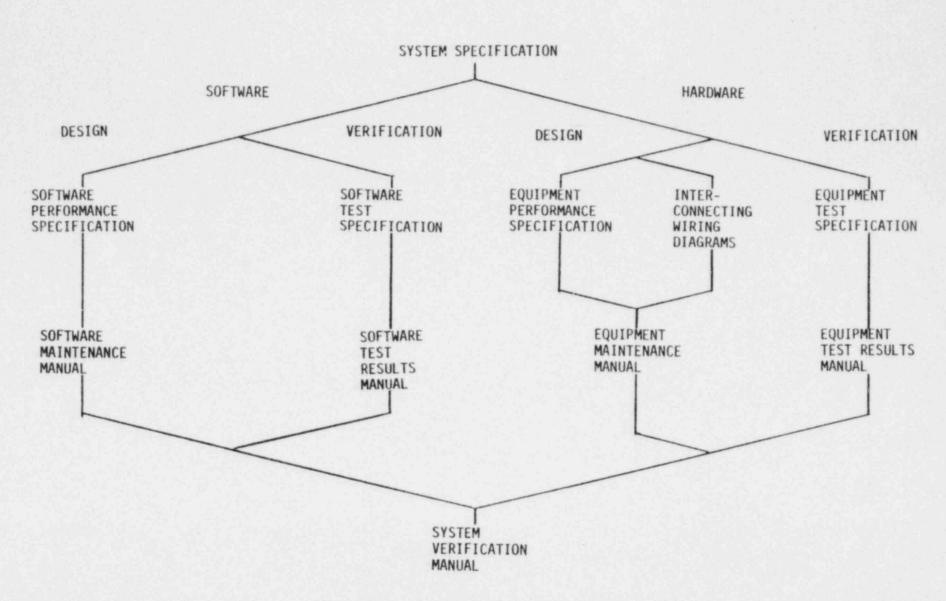

The documentation produced during the design and verification of the IPS software is shown on the left half of Figure 1-2. The software design team led by the chief programmer, produced the Software Performance Specifications based on the System Design Specification. These documents were reviewed and approved by the NS division. The software design team then produced the actual software and documented it by the Software Maintenance Manual, which contains the source code listings, relocatable object code and link loader output listings. The Software Performance Specifications and the Software Maintenance Manual were submitted to the verification team for design verification.

Upon receipt of the Software Performance Specifications the software verification team, under the leadership of the chief verifier, produced the Software Test Specification for each software subsystem and each software module. This dor nent defined the inspections and tests that would be used to verify the software subsystems and modules. The inspections performed for the purpose of verification were generally done at the source code level, which was usually a high level, structured syntax language (some assembly language was used where close interface to the hardware or strict timing concerns required it). Testing of the software was done in a micorprocessor development system (MDS). For this verification, the software module under test was loaded together with a code which simulated the module inputs and recorded the module outputs. In thest tests the inputs were exercised over their entire ranges and all paths in the software module were executed. Software verification was performed on a "bottom-up" approach where the lowest modules were verified by themselves before being assembled into a larger software subsystem for further verification. At the subsystem level, module interfaces and the flow of data through the modules were verified.

Any errors in the software which were discovered by the verification team were reported to the design team, along formalized channels, where they were resolved. Other communications between the teams, such as for clarification of the Software Performance Specifications, were also conducted procedurally using prepared question and response types of forms. A record of all of these error reports and communications is maintained by the chief programmer. A final record of the verification of each software module is provided in the Software Test Results Manual which is prepared by the verification team. This manual contains, in addition to the error reports discussed above, a complete detail of the test results.

# 1.3 HARDWARE DESIGN & VERIFICATION

The hardware was designed and verified by independent teams in a manner analagous to the software development. As indicated in the right half

of Figure 1-2, the hardware design is documented by Equipment Performance Specifications, which contain the specific functional requirements for each printed card design, and the Equipment Maintenance Manual which includes detailed printed card schematics as well as the overall system schematic wiring diagrams. These documents are reviewed against the System Design Specification by the NS division to verify adequacy of the design.

When the hardware design team was satisfied that the design of each printed circuit card design was correct, they submitted samples of the card, along with the design documentation, to the hardware verification team. This verification team prepared test procedures as documented in the Equipment Test Specification, and then executed those tests on various sample cards to verify that the design met the requirements of the Equipment Performance Specification. The results of these tests were documented in the Equipment Test Results Manual, which was transmitted to the NS division for approval. Again any design errors discovered by the verification team were reported and resolved through formal, traceable channels.

# 1.4 SYSTEM INTEGRATION AND VALIDATION

Upon the completion of the software verification and hardware verification, the two design branches were merged to form the overall system in the design verification process called system integration. This task was accomplished by the combined hardware and software design teams. Checkouts were performed to determine that the system was functioning prior to subjecting the system to validation testing. While these checkouts were not conducted using predefined test procedures, any errors found, either in software or hardware, were reported through the formal channels set up for the verification of the individual modules.

When the design team was satisfied that the prototype was completely integrated and debugged, the formal system design validation testing was performed by a team which consisted of personnel from both the AES and

NS divisions. The test procedures for the integrated system were written by the AES from a test specification which was prepared by the NS division. Responsibility for the approval of the test procedures and acceptance of the test results was held by the NS division. The documentation of the final system validation test is shown in Figure 1-2 as the System Verification Manual. The integrated system testing included the functional verification of the individual subsystems and the overall system response. This latter testing was performed by injecting computer generated, multivariate transients into the system inputs and recording its response.

# 1.5 NRC REVIEW BY AUDITS

At the completion of their review of RESAR-414, members of the NRC Instrumentation and Control Branch came to realization that a complete detailed review of a complex safety system, such as the IPS, would require too much effort to be handled by their normal review process. The NRC, therefore, proposed an audit process whereby Westinghouse was required to perform a complete formal design verification of the IPS while the NRC conducted audits of the results of the design verification. By the nature of this type of audit process, the auditors may probe as deeply as they wish into any area of the design verification, as a result the supplier must perform the entire verification with absolute rigor.

The NRC applied the audit technique to the IPS verification in order to test this new approach to the regulatory review of the safety systems. The NRC contracted personnel from Oak Ridge National Laboratories for the audit reviews, and after the second audit the NRC staff did not participate directly in the process. Reports were transmitted by ORNL to the NRC after each audit to keep the staff abreast of the verification program. Copies of these reports are included in the Appendix of this document.

The results of this trial audit review process were favorable. From the standpoint of the NRC, an indepth review of the IPS, part by direct inspection the remainder by induction, was obtained with only a small

expenditure of resources, a total of eight audits being held each lasting approximately two days. From the viewpoint of a vendor the audit process is successful because it removes a large amount of the uncertainty involved with the regulatory review process. Westinghouse hopes to see continued use of this review technique in the future.

In another trial review process, the NRC requested that a representative software sample be subjected to Software Sneak Analysis by the Boeing Company. This was done on the Data Link Controller software with the result that no errors were found in the executable code and only a few documentation discrepancies were noted. A more detailed evaluation of this analysis was sent to the NRC.

# 1.6 ONGOING EFFORT

The experience gained by Westinghouse in the IPS design verification program has been valuable. It has reaffirmed the principle that adequate design verification can be performed, with sufficient independence, within the design or anization. In fact, internal verification is superior to that which could be performed by an outside organization due to the intimate knowledge of the system provided by the verification team.

During the course of the IPS verification program, an interaction problem between microcomputer busses was noted. This problem only occurred at elevated temperatures, therefore, it did not interfere with the system verification testing, which was conducted at room temperature. However, it did necessitate a redesign of the system hardware. The design changes will be reverified in a program that will be adapted from the principles learned by Westinghouse in the IPS design verification program.

#### LEGEND:

EIC - ENGINEER IN CHARGE

AES - ACTUAL EQUIPMENT SUPPLIER

NS - NSSS SUPPLIER

(1) - CHIEF PROGRAMMER

(2) - CHIEF VERIFIER

Figure 1-1. Interdivisional 414 IPS Organization

Figure 1-2. System Documentation Structure

### 2.0 INTEGRATED SYSTEM VERIFICATION SUMMARY

# 2.1 METHODOLOGY OF INTEGRATED SYSTEM VERIFICATION

#### 2.1.1 TEST METHODOLOGY

It is the Westinghouse Nuclear Technology Division (NTD) practice that new equipment designs be verified to ensure that the equipment meets the requirements of the System Design Specification.

In order to minimize the number of test cases required for a total integrated system test, it is necessary that a sufficient number and type of prerequisite tests be conducted. These discrete tests are just as important as the integrated tests since, it is then possible to justify the scope and depth of the integrated test.

The system is designed from the top down, the system verification testing proceeds from the bottom up. This permits the proper operation of each sub unit of the system to be established prior to introducing into more complex interconnections within the system thus localizing problems to the lowest rung on the hierarchial ladder of the system. Additionally, the bottom up verification approach allows for the concentration of the interfaces within the system rather than the content of each sub unit at the later stages of the system verification testing.

For the series of tests described by the test outline referenced in the System Design Specification, it is assumed that the following activities have taken place and thus credit has been taken for them when designing the tests.

- All hardware modules have been verified to operate in accordance with their Equipment Performance Specifications (EPS).

- All software modules and processes have been verified to operate in accordance with their Software Performance Specifications (SPS).

The system has been functionally checked to ensure that signal paths are in accordance with design documentation.

The test methodology defined by the referenced test outline begins with a series of overlapping tests in which each successive test pick, up new portions of the system, while including portions previously tested to ensure that both the new portion and the interfaces function correctly. In general, at each step in the test process, the test cases will be defined in such a way as to exercise the new portion to be tested and to ensure that interfaces between the new portion of the system under test and the preceeding portions are adequately verified. No attempt is made to retest portions previously tested.

The scope of the hardware to be included in the system verification test is defined in WCAP-9153 and includes one Channel Set, a Digital Rod Position Indicating Cabinet, an Integrated Protection Cabinet, three Integrated Logic Cabinets and the Signal Selector. The remaining portions of the system will be simulated using appropriate equipment.

The final set of tests is called the integrated system test and is conducted with all prototype system elements connected together. These tests are designed to verify two aspects of the total system. That the correct outputs change state as required in response to particular test cases, and secondly, that other outputs do not change state when they should not. This will be accomplished by monitoring key system ouputs for the appropriate status.

#### 2.1.2 TEST CASES

It is the Westinghouse NTD practice that test cases be defined for each step of the system verification testing which will ensure that the equipment being tested is exercised over its normal and abnormal range of inputs in a way that assures its proper operation in an actual plant situations.

The test cases specified are appropriate to the intent of the test and may be selected with the knowledge of prior test runs. In particular, it is intended that where a series of overlapping tests is defined, that the test cases selected for the latter test make use of the knowledge gained from the earlier tests.

Test cases are defined with cognizance being given to the internal and external architectural features of the system. For instance, if a circuit board or software module is used in several applications, a rigorous test of only one board or module is required while for the others, only a limited test, primarily to check interfaces, is made. This approach will also be used where multivariable inputs to a portion of the system occur. In general, the test cases are chosen so that one variable is exercised while others are held at a nominal value related to normal operating conditions.

For complex circuits, specifically the DNBR and KW/FT, and the Trip Logic Modules, additional test cases are selected to ensure that the complex interactions within the circuits function properly.

The test cases for the final integrated system verification test are selected to demonstrate that the system performs properly when subjected to inputs reflecting the plant conditions associated with selected accidents studied in Chapter 15 of the RESAR 414. The driving variables involved in each accident are manipulated while the others are held constant.

#### 2.1.3 INPUT SIGNALS

The input signals used for the system verification test are simulated. The simulations are such as to reproduce the type of signal produced by the actual sensor in a plant. Process noise or any other noise is not be simulated as this will obscure the information that is being collected, more specifically that the overall transfer function is in accordance with the system design specification.

The two types of inputs used to exercise the system are steady state, and dynamic. Both types will be used depending on the nature of the information to be collected. For instance, channels with not time dependent elements are adequately checked using slowly varying or incremented signals to establish gain and bistable accuracies whereas channels containing lead lag units, etc. are verified through the use of time varying signals whose dynamic characteristics are precisely known. Dynamic input signals consists of ramps and steps (the latter being a special case of the former). The rate of change and magnitude of these signals is chosen to be consistent with the response of the channels being tested. Steps are typically used to establish the time response of a channel and its transient response generally while ramps are used to demonstrate the correct system operation and signal polarity.

Tests are run that demonstrate the proper operation of the system in response to out of range conditions. These tests are designed to drive the channels into saturation to ensure that the system responds in an orderly and timely manner when the out of range condition is removed.

#### 2.1.4 CONCLUSION

The overall approach to the system verification testing is based on a systematic series of overlapping tests which progress from detailed checks of small elements of the system to more limited checks of the total system. Test cases are selected to deal with the particular aspects of the system under consideration and test inputs are chosen to establish proper system operation for static and dynamic, normal an out-of-range signals.

# 2.2 PREREQUISITE INTEGRATED SYSTEM VERIFICATION TESTS

This section defines the objectives of each of the system tests and indicates the order required to perform each test to insure proper overlap testing. To show this overlap testing, it is necessary to define the various stages in which the tests were categorized.

Preliminary testing is a series of tests on the Integrated Protection and Logic Cabinets, that tests the system on a component and subsystem basis. In Stage 1, the verification of the interelation of the components and subsystems is performed by testing the non-logic portion of the IPS consisting of the process transmitter inputs, transmitter power supplies, analog signal conditioning circuits, speed pickup input, Nuclear Instrumentation System (NIS) input, A/D converters, Safety Grade Digital Rod Position Indicator (SDRPI) data link input, time dependent functions, bistables and calculations.

In Stage 2 all of the devices tested in Stage 1 are activated again and continues through the interposing logic of the system up to and including partial trips and ESF actuations. The Integrated System Tests Cases operate in the integrated system by simulating a series of plant accident conditions and comparing system results against precalculated results for such conditions. A more detailed description of Integrated System testing is described in Section 2.4, a list of prerequisite and other various tests with a brief description follows:

#### 2.2.1 PRELIMINARY TESTS

# 2.2.1.1 IPC Preliminary Tests

#### 1. General Tests

The objective of this section is to perform tests on cables and cabinet wiring, calibrate cards and burn-in the system prior to starting the subsystem tests. These tests are:

a. Cables

(1)

a,c,e

(5)

a,c,e

d. Burn-In

(1)

7 a,c,e

# 2. IPC Subsystem Tests

The objective of this section is to verify each identifiable subsystem made up of verified software loaded into verified hardware prior to starting system verification tests.

The subsystem tests consists of the following:

a,c,e

The subsystems involved are:

(a) (b) (c) (d) (e) (f) (g) (h) (i)

# 2.2.1.2 ILC Preliminary Tests

#### 1. General Tests

The objective of this section is to test cables and cabinet wiring, calibrate cards and burn-in the system prior to starting the subsystem tests. These objectives are similar to IPC General Test and are outlined below.

a,c,e

a,c,e

(1) (2)

2-8

b. Cabinet Wiring

Cards

(3)

(4)

(5)

Burn-In

(6)

a,c,e

a,c,e

2. ILC Subsystem Tests

The objective of this section is to verify each identifiable subsystem made up of verified software loaded into verified hardware prior to starting system verification tests.

The subsystem tests consists of the following:

The specific subsystems involved are as follows:

a. Communications dus Controller

# Objective

The purpose of the Communications Bus Controller subsystem test is:

a,c,e

a,c,e

2-10

]a,c,e b. ESF 2/4 Voting Logic Objective The purpose of the ESF 2/4 Voting Logic subsystem test is: a,c,e

7 a,c,e (3) (4) c. ESF System Level Logic Objective The purpose of the ESF System Level Logic subsystem test is: a,c,e (1) (2) (3) (4) (5) 5356A 2-12

d. ILC Demux/Mux

Objective

The purpose of the ILC Demux/Mux subsystem test is:

(1)

(2)

(3)

(4)

(5)

(6)

e. Interposing Logic

Objective

The purpose of the Interposing Logic subsystem test is:

a,c,e

a,c,e

(1)

(2)

(3)

(4)

f. Power Interface

Objective

The purpose of the "Power Interface" subsystem test is:

(1)

(2)

5356A

2-14

g. Maintenance Arming

Objective

The purpose of the "Maintenance Arming" subsystem test is:

a,c,e

(1)

(2)

h. Auto Tester Arming

Objective

The purpose of the "Auto Tester Arming" subsystem test is:

(1)

(2)

(3) \[ \]

(4)

i. Auto l'ester

# Objective

The purpose of the Auto Tester subsystem test is:

#### 2.2.2 STAGE 1 TESTING

The objective of this section is to verify the operation of the nonlogic portion of the IPS consisting of the process transmitter inputs, transmitter power supplies, analog signal conditioning circuits, speed pickup input, NIS input, A/D converters, SDRPI data link input, time dependent functions, bistables and calculations.

Operation of the Control Signal Selector is also verified during this stage.

All outputs are monitored continuously.

Stage 1 tests overlap with pre-requisite tests.

1. Static Test

### Objective

The purpose of the Static Test is:

- a. To verify that process input accuracies under static conditions meet the established requirements.

- b. To verify that system scaling can be accomplished.

- c. To verify system wiring up to A/D converter input, lead lag input, rate lag input or bistable input; termination assignments; A/D converter address assignments and signal polarities. This establishes that the input/output relationship confirms with the system drawings and that the software is functioning correctly.

- d. To determine the output loading effects (both internal and external).

- e. To ensure that there are no excessive hysteresis effects between 0 and 100% full range.

- f. To verify all input and output data links are functioning properly.

2. Dynamic Tests for Analog Channels

## Objective

The purpose of the Dynamic Tests for the Analog Channels is:

- a. To verify the operation of all lead/lag functions and bistables implemented in hardware.

- b. To verify that lead/lag and bistable outputs are input correctly to other sub-systems.

- c. To verify that the IPC Automatic Tester is receiving the feedback signals correctly.

- d. To verify that the Control Signal Selector, Plant Computer, ILC A and ILC B are receiving the status and trip signals correctly over data links.

- 3. Dynamic Tests For ESF Channels

# Objective

The purpose of the Dynamic Tests for ESF Channels is:

- a. To verify the <u>trip</u> and <u>reset</u> accuracy of all bistables implemented in software.

- b. To verify that lead/lag, rate/lag, and bistable outputs are input correctly to other sub-systems.

- c. To verify that the IPC Automatic Tester is receiving the feedback signals correctly.

- d. To verify that the Control Signal Selector, Plant Computer, ILC A and ILC B are receiving the status and trip signals correctly over data links.

4. Dynamic Tests For NIS Channels

#### Objective

The purpose of the Dynamic Tests for NIS Channels is:

- a. To verify that the software summators are calibrated properly.

- b. To verify that software track/store is operating correctly.

- c. To verify the <u>trip</u> and <u>reset</u> accuracy of all bistables implemented in software.

- d. To verify that summator, track/store, rate/lag, and bistable outputs are input correctly to other subsystems.

- e. To verify that the IPC Automatic Tester is receiving the feedback signals correctly.

- f. To verify that the Control Signal Selector, Plant Computer, ILC A and ILC B are receiving the status and trip signals correctly over data links.

- 5. DNBR and KW/FT Subsystem Test Cases

# Objective

The purpose of the DNB-KW/FT partial trips subsystem test is:

- a. To verify that the DNB-KW/FT subsystem is calibrated correctly.

- b. To verify that the DNB and KW/FT partial trip calculations perform correctly given numerous static and dynamic test cases.

- c. To verify the data flow from the DNB-KW/FT subsystem to the 1) IPC Automatic Tester, 2) Signal Selector, and 3) Plant Computer.

POOR ORIGINAL

6. Signal Selector Subsystem Test Cases

#### Objective

The purpose of the Signal Selector subsystem test is:

- To verify that the Signal Selector subsystem is calibrated correctly.

- t. To verify that the Signal Selector performs correctly given numerous test cases.

### 2.2.3 STAGE 2 TESTING

The objective of this section is to verify the operation of the logic portion of the IPS.

The verification is conducted by exercising the sensor inputs and monitoring the logic outputs for Reactor Trip and Engineered Safeguards Features. System and component manual actuations are also verified.

Operation of Automatic testers in IPC, ILC and ICC is verified during this stage.

Stage 2 tests overlap with Stage 1 tests.

1. Logic Tests for Analog Channels

# Objectives

The purpose of the Logic Tests for Analog Channels is:

a. To verify that the logic from bistable outputs and from manual pushbuttons up to the inputs of 2/4 Reactor Trip Logic or 2/4 ESF Voting Logic is functioning properly.

- b. To verify that the IPC Automatic Tester is receiving the feedback signals correctly.

- c. To verify that Plant Computer, IPC II, IPC III, IPC IV, ILC A and ILC B are receiving the status and trip signals correctly over the data links.

- 2. Logic Tests for ESF Channels

The purpose of the Logic Tests for ESF Channels is:

- a. To verify that the logic from bistable outputs, reactor breaker status contacts and manual pushbuttons up to the inputs of 2/4 Reactor Trip Logic or 2/4 ESF Voting Logic is functioning properly.

- b. To verify that the IPC Automatic Tester is receiving the feedback signals correctly.

- c. To verify that Plant Computer, IPC II, IPC III, IPC IV, ILC A and ILC B are receiving the status and trip signals correctly over the data links.

- 3. Logic Tests for NIS Channels

### Objective

The purpose of the Logic Tests for NIS Channels is:

a. To verify that the logic from bistable outputs, turbine status contacts and manual pushbuttons up to the inputs of NIS High Voltage Power Supply Cutoff Logic, 2/c Reactor Trip Logic or 2/4 ESF Voting Logic is functioning properly.

- b. To verify that the IPC Automatic Tester is receiving the feedback signals correctly.

- c. To verify that Plant Computer, IPC II, IPC III, IPC IV, ILC A and ILC B are receiving the status and trip signals correctly over the data links.

- D. Logic Tests for DNBR and KW/FT Trips

The partial reactor trips have been tested during the DNBR and KW/FT subsystem static and dynamic tests.

The purpose of the "Logic Tests for DNBR and KW/FT" partial trips is to verify that the automatic bypasses of the DNBR and KW/FT partial trips operate under the following circumstances:

- a. Low reactor coolant flow in the loop associated with the channel set.

- b. Failure of analog inputs to the DNB-KW/FT subsystem.

- c. Failure of serial digital inputs to the DNB-KW/FT subsystem.

- 4. Reactor Trip 2/4 Bypass Logic

### Objective

The purpose of the Reactor Trip 2/4 Bypass Logic is:

- a. To verify the logic of the NTL and NTB cards directly.

- b. To verify the operation of one 2/4 BYPASS gate within the Trip Logic Computer with an exhaustive test (all 256 input combinations).

- c. To verify the operation of all 2/4 BYPASS gates for four test cases. And in conjunction verify the proper transmission of partial trips and bypasses to Channel Sets II, III, and IV.

- 5. IPC Automatic Tester

The purpose of the IPC Automatic Tester verification is:

- a. To check that the local and MCB located IPC Automatic Tester Panels are functioning correctly.

- b. To check that the IPC Automatic Tester results are being printed correctly on the local terminal and at the plant computer.

- c. To check that the IPC Automatic Tester is testing the IPC under normal conditions with no errors.

- d. To check that the IPC Automatic Tester can detect properly the following types of errors:

Channel Inaccuracy

Dynamic unit Time Constant Inaccuracy

Bistable Setpoint Inaccuracy

Logic Fault

Reactor Trip Fault

Reactor Trip Response Time

Abnormal Operation

6. ILC Train A Automatic Tester

#### Objective

The purpose of the ILC Automatic Tester Test is:

- a. To verify that with the ILC System set up for normal operation, the tester functions properly transmitting the appropriate (idle-mode) information to the plant computer and for local displays.

- b. To verify that the ILC Automatic Tester and the ILC System are functional in the auto test mode and the appropriate test results and other pertinent information are transmitted to the plant computer and local displays.

- c. To verify that the ILC Automatic Tester detects errors pertinent to idle mode and test mode operations.

- 7. Control Signal Selector Automatic Tester

The purpose of the Control Signal Selector Automatic Tester subsystem test is:

- a. To verify that the Control Signal Selector Automatic Tester is functional in the self test mode.

- b. To verify that the Control Signal Selector Automatic Tester and the Signal Selector(s) are functional in the auto test mode.

- c. To verify that the Control Signal Selector Automatic Tester detects errors.

2.2.4 SYSTEM VERIFICATION ERROR REPORT SUMMARY

- a,c,e

It will not be attempted to detail every problem and solution in this section, however, a list describing the problems is provided in this document and several random problems are listed in detail as examples of problem resolution.

Ta,c,e

The following section contains more detailed descriptions of several randomly chosen problems from each of the categories discussed, as well as the solution to these problems:

\_a,c,e

ERROR REPORT NO .:

PROBLEM:

ACTION TAKEN:

ERROR REPORT NO .:

PROBLEM:

ACTION TAKEN:

ERROR REPORT NO .:

PROBLEM:

ACTION TAKEN:

ERROR REPORT NO.: PROBLEM:

ACTION TAKEN:

ERROR REPORT NO.: PROBLEM:

ACTION TAKEN:

ERROR REPORT NO .:

PROBLEM:

ACTION TAKEN:

ERROR REPORT NO.: PROBLEM:

ACTION TAKEN:

-a,c,e ERROR REPORT NO .: PROBLEM: ACTION TAKEN FRROR REPORT NO .: PROBLEM: ACTION TAKEN: ERROR REPORT NO .: PROBLEM: ACTION TAKEN: ERROR REPORT NO .: PROBLEM:

ACTION TAKEN:

ERROR REPORT NO .:

PROBLEM:

ACTION TAKEN:

ERROR REPORT NO.: PROBLEM:

ACTION TAKEN:

ERROR REPORT NO.: PROBLEM:

ACTION TAKEN:

ERROR REPORT NO .:

PROBLEM:

ACTION TAKEN:

ERROR REPORT NO .:

PROBLEM:

ACTION TAKEN

ERROR REPORT NO .:

PROBLEM:

ACTION TAKEN:

2-32

a,c,e

# 2.3 INTEGRATED PROTECTION SYSTEM SIMULATED TRANSIENT TEST RESULTS

#### 2.3.1 TEST OBJECTIVE

The final phase of the integrated system testing was the Simulated Transient Testing. The objective of these tests was to demonstrate that the system is capable of responding to multivariate transients such as those the system would experience while performing its mission in the plant. This was accomplished by simulating plant transients on a digital computer, using safety analysis codes, recording those transients on an analog tape recorder and injecting them into the system prototype through its normal inputs.

In order to coordinate this validation of the system to its design bases, the transients that were simulated were selected from the RESAR-414 Chapter 15 accident analysis. In general, the conservative assumptions and analysis, typical of reactor safety analyses, were not adhered to for these simulated transients, rather, "best estimate" analysis was used in that a single set of nominal plant parameters was used for all of the transients and the initial conditions were nominal plant values. This is consistent with the objective of this testing, ie, to show that the system responds to realistic transients. However, because the assumptions for the generation of these transients are different than those of the safety analyses, the results are not directly comparable. The results of these transient tests will be correlated to the system design bases by comparison to the Limiting Safety System Settings and accuracy requirements specified for the system. It should be noted that due to the broad scope of this type of testing, it is not practical to test all functions of the Integrated Protection System. The completeness required for total system validation is provided by the individual channel function tests which were performed in the remainder of the integrated systems tests.

5356A

#### 2.3.3 DESCRIPTION OF TRANSIENTS

The following paragraphs briefly describe the transient test cases performed including assumptions made and initial conditions. In each case, the last digits of the paragraph number is the test case number.

#### 2.3.3.1 Uncontrolled Rod Withdrawal From Low Power .

This transient is an uncontrolled power excursion caused by the continuous withdrawal of the control rods. Although it is usually analyzed with a subcritical initial condition, LOFTRAN is not capable of modelling a subcritical reactor core so the initial condition is taken as 1.0% nominal power. The transient is generated by ramping the reactivity insertion at 144 pcm/second. The expected actuations are the startup NIS reactor trips.

### 2.3.3.2 Uncontrolled Rod Withdrawal From Full Power

This transient is similar to the previous one except that the initial plant condition is full power and the reactivity insertion rate is 60 pcm/second. The primary protective functions are reactor trips on high nuclear flux or a low DNB ratio.

# 2.3.3.3 Uncontrolled Rod Withdrawal, N-1 Loop Operation

This transient is like the previous except for the speed at which it progresses and the fact that a reactor coolant is taken out-of-service (pump shut off) as an initial condition, thus causing the DNB-KW/Ft. module to be automatically bypassed. The initial power is 70% and the reactivity insertion rate is 3.3 pcm/second.

# 2.3.3.4 Dropped Rod Group

This transient is initiated by the dropping of a control rod group into the core (negative reactivity step of 1000 pcm) causing an immediate decrease in reactor power after which the control system attempts to

recover to the initial conditions. Due to the primary/secondary system power mismatch, the primary system temperature and pressure drop initially. The primary protective action is the dropped rod reactor trip which is armed by a sudden decrease in power and trips the reactor if the power rises above the minimum value following the event by more than 7%.

### 2.3.3.5 Partial Loss of Forced Reactor Coolant Flow

This transient is generated by tripping one of the reactor coolant pumps and allowing it to coast down. The initial power level of the plant is 100%. The protective action is the low reactor coolant flow reactor trip.

### 2.3.3.6 Inadvertent Startup of a Reactor Coolant Loop

This transient is the startup of a reactor coolant loop from the N-1 loop initial condition (70% power). The consequent surge of cold water leads to a power excursion in the reactor.

### 2.3.3.7 Loss of External Electrical Load

This transient is simulated by stepping the steam flow out of the steam generators from its initial nominal value to zero as would be the case with rapidly closing turbine throttle valves. The steam dump system is assumed to be inoperative, thus, the primary and secondary system pressure rise rapidly. The principal protective action is the high pressurizer pressure trip.

### 2.3.3.8 Loss of Normal Feedwater

This transient is simulated by stepping the feedwater flow to all four steam generators to zero. The immediate effect is a falling steam generator water level and an increase in the reactor coolant temperature due to the loss of heat sink.

#### 2.3.3.9 Excessive Feedwater at Full Power

Excessive feedwater, three times nominal to one steam generator, could possibly be caused by a failed control system or valve. It in turn causes a rising steam generator water level, which leads to a reactor trip, and a cooling of the primary system, which causes an increase i reactor power level due to the negative moderator coefficient of reactivity.

#### 2.3.3.10 Excessive Load Increase

An excessive load increase, simulated by a 10% increase in steam flow, causes the cooling of the primary system and, hence, the increase of the reactor power. Protection is provided by the overpower reactor trip functions.

#### 2.3.3.11 Accidental Depressurization of the Primary System

Although LOFTRAN is not specifically designed to handle this type of transient, it can be approximated by reducing the actuation setpoint for the pressurizer relief valves so that they effectively stick open. The principal protective actions are the low pressurizer pressure reactor trip and safety injection, and the low DNB ratio reactor trip.

# 2.3.3.12 Accidental Depressurization of the Secondary System

Although it was in the original plans to perform this transient, it was realized that it is, from the viewpoint of the integrated protection system response, identical to either Test Case #10 or Test Case #15, depending on the initial condition. It was therefore judged to be redundant and was deleted from the test plan.

# 2.3.3.13 Complete Loss of Forced Reactor Coolant Flow

This transient is generated in an identical manner to Test Case #5 except that all four of the reactor coolant pumps are tripped and allowed to coast down. For the injection of this transient into the

prototype, the flow signals from the independent coolant loops will all be simulated by a single recorded channel. The primary protective functions are the low coolant flow and low pump speed reactor trips.

#### 2.3.3.14 Small Primary System Break (LOCA)

The small LOCA is simulated or the purpose of these tests as a steam generator tube rupture. The combination of this transient, the stuck pressurizer relief valve (Case #11) and the steam break (Case #15) span the gamut of fluid loss accidents and exercise the safety injection actuation functions as well as related functions.

#### 2.3.3.15 Small Secondary System Break

This transient is simulated as an eight inch diameter hole in the steam piping which discharges to the containment atmosphere. The initial condition of the plant is low power level (1.0% nominal) to maximize the effects of the cooldown. Again, safety injection actuation and its related functions provide the principal protection.

### 2.3.3.16 Rod Ejection

The scenario of the rod ejection accident is that the housing of the control rod drive mechanism on a high worth rod ruptures and the consequent hydraulic forces thrust the rod out of the core. For this simulation, the rod ejection is simulated by a 200 pcm reactivity step, however, LOFTRAN is not capable of modeling the concurrent loss of coolant through the ruptured mechanism. This shortcoming was not considered to be significant, though, because of the other coverage of LOCA type transients. The principal protective actions for this transient are the reactor trips on high neutron flux and high rate of change of flux.

#### 2.3.4 ACCEPTANCE CRITERIA

As the simulated transients are injected into the integrated protection system prototype, the response of the system is measured by recording various actuation logic signals on strip chart recorders. These signals

include system level actuation output, such as the reactor trip breaker actuation signal and the system level safety injection actuation, and certain internal signals, such as the individual partial trip signals that are the inputs to the Trip Logic Module. The acceptance of the test results is based on a comparison of the actual measured first occurance of the logic signal transitions to the predicted response of the system.

It was determined in the development of the simulated transient test plan that, due to the limited availability of test equipment, it would not be practical to record the entire set of actuation signals identified for every transient case. Therefore, the subset of signals to be recorded for each test case was selected based on Table 031.31-1 of RESAR 414. This table indicates which of the protective functions of the integrated protection system may be expected to occur in the course of a given transient. This basis for the limitation of the recorded responses is justified by the concept that the purpose of this portion of the system validation testing is to demonstrate that the performance of the system is consistent with its design bases.

The acceptance review of the transient test results is a two step process with the preliminary evaluation being based on the time of the first transition of the recorded logic actuations relative to the start of the transient. The observed elapsed times will be compared to expected values which are derived from the simulated transient data. These expected values are expressed as minimum and maximum evaluation times, whose derivation is discussed below.

a,c,e

2-41

5356A

The resulting acceptance criteria are listed for the recorded signals for each test case in Table 2.3.1 along with the observed values of the event times.

As was noted in the Test Objective section, the measured responses of the integrated system during the transient tests are not directly comparable to the design basis transients analyzed in Chapter 15 of RESAR-414. However, the purpose of system validation testing is to demonstrate that the system design meets its functional requirements. Therefore, the final acceptance criteria for the integrated system transient tests are based on the design bases documents for the Integrated Protection System. The fundamental requirement of the system is that it initiate certain actions when its inputs exceed prescribed limits. This requirement forms the basis for the transient test acceptance criteria. The ACCEPT code, which calculated the preliminary evaluation range, was run again after the transient test results were known and the bistables input values were printed at the actual trip times noted during the tests. These inputs are then compared to limits derived from the system design basis documents to validate the system's functions. These acceptance limits are derived in the following manner. The Allowable Setpoint for each of the bistables is taken from the Limiting Safety System Settings section of the Technical Specifications (RESAR-414, Chapter 16). Then the specified channel accuracy is added to (subtracted from) each of the Allowable Setpoints yielding the "Safety Limit."

These channel accuracies, which are taken from the 414 Standard Functional Requirements, contain allowance for sensor error as well as the inaccuracies of the cabinet located electronics. Since the sensors are not a part of the integrated system prototype, no additional error allowance is taken for the test setup. This acceptance analysis is conservative in that it does not take credit for the response time allowed for each function. By the time the actuations of the system are recorded, the inputs to the system have moved closer to the safety limit. The actual response time of the system is not verified as a part of these tests, rather it is measured by the IPC Automatic Test Subsystem and verified during the verification of that subsystem. The acceptance criteria generated in this way are listed in Table 2.3-1 for each transient and bistable.

a,c,e

2.3.5 TEST RESULTS ANALYSIS

Notes &,c,e Acceptance Value at Trip Acting Signal lime. Measured Evaluation Range (secs) Imin Imax lest Case Monitored Signals

TABLE 2.3-1

TRANSIENI TEST RESULTS SUMMARY

POOR ORIGINAL

#### TABLE 2.3-1 (cont.)

#### Notes:

- Measured trip or actuation occurred outside of calculated evaluation range.

- 2. No trip or actuation was predicted for this variable.

- Lack of maximum evaluation criterion indicates that trip or actuation may not occur.

TABLE 2.3-2

# KEY TO ACTING SIGNAL CODES

| current |

|---------|

|         |

|         |

|         |

|         |

|         |

| minal   |

| minal   |

| minal   |

| power   |

|         |

|         |

|         |

| ond     |

|         |

|         |

| minal   |

|         |

TABLE 2.3-2

# KEY TO ACTING SIGNAL CODES

| Mnemonic | Signal                                    | Units                 |

|----------|-------------------------------------------|-----------------------|

| CONTP    | Containment Pressure                      | psig                  |

| IRNIS    | Intermediate Range Neutron Flux           | amps detector current |

| PPLL     | Pressurizer Pressure, Lead/Lag            | psig                  |

|          | Compensated                               |                       |

| PRZRL    | Pressurizer Water Level                   | % of span             |

| PRZRP    | Pressurizer Pressure                      | psig                  |

| OKWFT    | Maximum Kilowatts per Foot                | kw/ft                 |

| QN16     | N-16 Reactor Power                        | Fraction of nominal   |

| RCFLOW   | Reactor Coolant Flow                      | Fraction of nominal   |

| RCPSPD   | Reactor Coolant Pump Speed                | Fraction of nominal   |

| RLNIS    | Neutron Flux, Rate/Lag Compensa-<br>tion  | Frac. of nom. power   |

| RX Trip  | Reactor Trip                              |                       |

| SGLVL    | Steam Generator Water Level               | % of span             |

| SRNIS    | Source Range Neutron Flux                 | Counts per second     |

| TCLD     | Cold Leg Temperature                      | °F                    |

| TCLC     | Cold Leg Temp., Lead/Lag Compen-<br>sated | °F                    |

| TOTNIS   | Total Neutron Flux, Power Range           | Fraction of nominal   |

|          |                                           |                       |

# 3.0 SYSTEM DESIGN SPECIFICATION SUMMARY

In order to provide an overall definition of the System Design Specification (SDS), Westinghouse Nuclear Technology Division (NTD) provides a top level "Master Reference Document," to the Actual Equipment Supplier (AES) and other interested groups. This "Master Reference Document," together with its listed documentation references, is the Westinghouse NTD System Design Specification for the IPS Prototype. It includes specifications, system drawings, standards and procedure guidelines for manufacture and testing for both the hardware and software aspects of the system.

The SDS is under revision control and the drawings and documents for the base line design are listed in the Appendix of this document.

The AES receives the SDS when the purchase order is placed and any changes to the SDS are documented by the purchase order documentation.

The drawings and documents submitted by the Supplier (AES) are controlled at Westinghouse NTD by the purchase order policies and procedures and all records are kept in an auditable file.

The SDS (as referenced by the "System Specification Master Reference Document," SD-IPLS-593, Revision 2) for the IPS Prototype, consists of the following documents and drawings:

# 3.1 EQUIPMENT SPECIFICATION (E-SPEC):

Westinghouse E-Spec 953230:

This E-Spec together with its listed references in Section 3.0 establishes technical and administrative requirements covering system related hardware phases of design, manufacture and testing of the IPS. The E-Spec contains specific requirements for:

a,c,e 3.2 SYSTEM BLOCK DIAGRAM:

Westinghouse Drawing 1218E17:

This drawing represents the overall IPS architecture and its inter-connections. Specifically shown on this drawing are:

a,c,e

# 3.3 COMPOSITE BLOCK DIAGRAMS

3.3.1 INTEGRATED PROTECTION CABINETS (IPC)

Westinghouse Drawing 8761096:

These drawings represent the implementation of the system functional requirements, functional diagrams, flow diagrams, channel lists and other key documents for the IPC in both hardware and software. The protection functions contained in the Integrated Protection Cabinets and defined by these drawings are: la,c,e

#### 3.3.2 INTEGRATED LOGIC CABINETS (ILC)

Westinghouse Drawing 8761D98:

These drawings represent the hardware and software implementation of the functional requirements, functional diagrams and key document for the ILC. The Train A Engineered Safeguard Features contained in the Integrated Logic Cabinets and defined by these drawings are:

#### 3.3.3 ILC INTERPOSING LOGIC AND POWER INTERFACE

Westinghouse Drawing 8763D47

These drawings represent the implementation of functional requirements, diagrams, system interlocks and electrical loads that the ILC control. Complete definition of all Train A load controls and position indication are defined.

# 3.4 IPS MODULE LIST AND SPECIFICATION SHEETS

Westinghouse SD-IPLS-462

The Module Equipment List is a reference document. It provides listings of all IPS hardware and software modules by process function and physical location. All entries have unique tag numbers that match the

Composite Block Diagrams. From this unique tag number, the following additional reference information is provided in the Module Equipment List:

Process Protection Function

Module Description

Module Spec Sheet No.

Module Location

Purchase Order No.

Supplier

Drawing References

The Module Specification Sheets define the IPS nardware and software modules. Specifications for the various type modules typically contain the following:

Module range

Engineering Units

Module Accuracy

Temperature/resistance conversion tables

Transfer functions

Timing

Alarm setpoints

Algorithms

Definitions of variables

Applicable Standards

Documentation references

# 3.5 IPS SOFTWARE STANDARD:

Westinghouse SD-IPLS-590:

This Standard defines the Westinghouse NTD requirements for the IPS Software. The areas defined by this Standard area:

Standard Scope

Administration Requirements

Design and Implementation

Verification

Documentation

Installation and Maintenance

#### 3.6 IPS AUTOMATIC TESTING REQUIREMENTS

Westinghouse SD-IPLS-553:

This document provides the design basis for the automatic testing of the IPS. The Protection System testing is divided into four classifications; automatic periodic test, continuous error checks, manual tests and special tests. The contents of this document are:

Purpose

Design Criteria

Automatic Periodic Tests

Continuous Error Checks

Manual Testing

Time Response Testing

Special Tests

# 3.7 IPS SYSTEM TEST GUIDELINES

Westinghouse SD-IPL3-582:

This document describes the integrated system verification test guidelines which are used as a basis for the System Test Procedure. It provides guidelines to verify that the IPS meets the Westinghouse NTD requirements of the System Design Specification. The contents of this document are: Purpose & Objective

References

Prerequisites

Test Methods & Practices

Test Procedures

Acceptance Criteria

Functional Test Guidelines

Setup Data for Verification Tests

#### 3.8 REFERENCES

- WCAP-9153; "414 Integrated Protection System Prototype Verification Program."

- WCAP-8899; "Westinghouse Model 414 Control System Signal Selector Device."

- WCAP-8897; "Bypass Logic for the Westinghouse Integrated Protection System" -- Addendum 1.

- 4. Sketch -- Trip Logic System for 414 IPS SKJS-092977-I.

- WCAP-8587; "Methodology for Qualifying Westinghouse WRD Supplied NSSS Safety Related Electrical Equipment."

#### 4.0 HARDWART VERIFICATION SUMMARY

The purpose of the hardware verification program is to ensure that the equipment meets the performance requirements specified in the Equipment Performance Specifications (EPS). The Actual Equipment Supplier's (AES) hardware development group composes the EPS given design inputs from the AES's System Engineering group and Westinghouse NTD. The Westinghouse NTD inputs are provided in, and taken from, the System Design Specification (SDS) and participation by Westinghouse NTD in the AES product definition meetings.

A standard format has been established for all EPS's and the performance requirements for the hardware are contained in Sections 7 and 12 of each EPS.

In this report, sections of each EPS have been provided to give definition of why the piece of hardware was developed and how it operates.

To obtain test results, Product Verification Test Procedures (PVTP) have been established by the AES to test the performance requirements for each piece of equipment covered in the EPS's, Sections 7 and 12. The test results from the PVTP are then compared to the EPS. Any errors found, discrepancies between the EPS performance requirements and actual test results, are recorded by a Request for Engineering Action (REA). Standard formats have been established for the PVTP's and the REA's.