| Rev No. | Date              | Description                | Approved                  | Reviewed<br>by             | Prepared<br>by              |

|---------|-------------------|----------------------------|---------------------------|----------------------------|-----------------------------|

| 0       | See Cover<br>Page | Initial Issue              | See Cover<br>Page         | See Cover<br>Page          | See Cover<br>Page           |

| 1       | Feb.21 ,2012      | See DECN-FA32-3709-1000-01 | S.Totsuka<br>Feb.21 ,2012 | H.Kitazono<br>Feb.21 ,2012 | M.Shirasaki<br>Feb.21 ,2012 |

| 2       | Mar.8 ,2012       | See DECN-FA32-3709-1000-02 | S.Totsuka<br>Mar 8,2012   | H.Kitazono<br>Mar.8 ,2012  | M.Shirasaki<br>Mar.7,2012   |

| 3       | Jun.26 ,2012      | See DECN-FA32-3709-1000-03 | S Totsuka<br>Jun 26 ,2012 | H.Kitazono<br>Jun.26 ,2012 | K. Kasai<br>Jun:26 ,2012    |

| 4       | Sep.24 ,2012      | See DECN-FA32-3709-1000-04 | S.Totsuka<br>Sep.24 ,2012 | H Kitazono<br>Sep.21 ,2012 | K. Kasai<br>Sep.21-,2012    |

| 5       | Jan.11,2013       | See DECN-FA32-3709-1000-05 | A:Nakai<br>Jan:11 ,2013   | H-Kitazono<br>Jan 9 ,2013  | K. Kasai<br>Jan 9 ,2013     |

| 6       | Feb.26 ,2014      | See DECN-FA32-3709-1000-06 | A.Nakai<br>Feb.26 ,2014   | H.Kitazono<br>Feb.19 ,2014 | K. Kasai<br>Feb.19.,2014    |

| 7       | Apr.28 ,2014      | See DECN-FA32-3709-1000-07 | A.Nakai<br>Apr.28 ,2014   | H.Kitazono<br>Apr.24 ,2014 | K. Kasai<br>Apr.23 ,2014    |

| 8       | See Cover<br>Page | See Cover Page             | See Cover<br>Page         | See Cover<br>Page          | See Cover<br>Page           |

|         |                   |                            |                           |                            |                             |

|         |                   |                            |                           |                            |                             |

|         |                   |                            |                           |                            |                             |

|         |                   |                            |                           |                            |                             |

|         |                   |                            |                           |                            |                             |

# **Record of Revisions**

.

# Table of contents

| 1 | Inte | roduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |  |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|   | 1.1  | Purpose ····· 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |

|   | 1.2  | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5        |  |

| 2 | Def  | finitions and Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |  |

|   | 2.1  | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -        |  |

|   | 2.2  | Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6        |  |

| 3 | Ref  | Ference Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9        |  |

|   | 3.1  | Code of Federal Regulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9        |  |

|   | 3.2  | Regulatory Guides and NRC Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>9</u> |  |

|   | 3.3  | Industry Standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |  |

|   | 3.4  | Toshiba Internal Standards (NED, NICSD) States and the states of the sta | 9        |  |

| 2 | 3.5  | Toshiba Internal Standards (PPDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1        |  |

| - | 3.6  | Project Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Í        |  |

|   | 3.7  | Toshiba Internal Guide (NICSD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2        |  |

| 4 | Ver  | ification and Validation Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3        |  |

| 4 | 4.1  | Organization ······                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |  |

| 4 | 4.2  | Master Schedule 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4        |  |

| 4 | 4.3  | Software Integrity Level Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |

| 2 | 1.4  | Resource Summary 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |  |

| 4 | 4.5  | Responsibilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |  |

| 4 | 4.6  | Tools, Techniques, and Methodologies ·····1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |  |

| 2 | 4.7  | Security 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8        |  |

| 5 | Ver  | ification and Validation Activities19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9        |  |

| 4 | 5.1  | Management ······                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9        |  |

| 4 | 5.2  | Project Planning and Concept Definition Phase 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1        |  |

| 5 | 5.3  | Requirements Definition Phase 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3        |  |

| 4 | 5.4  | Design Phase24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4        |  |

| 4 | 5.5  | Implementation and Integration Phase ······2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7        |  |

| 4 | 5.6  | Module Validation Testing Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2        |  |

| 5 | 5.7  | System Validation Testing Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4        |  |

| 5.8     | Functional Element V&V ··································   |

|---------|-------------------------------------------------------------|

| 5.9     | Hardware V&V······39                                        |

| 6 V&    | V Reporting 40                                              |

| 6.1     | V&V Report ······40                                         |

| 6.2     | Anomaly Reporting                                           |

| 7 V&    | V Administrative Requirements 42                            |

| 7.1     | Anomaly Reporting and Resolution                            |

| 7.2     | Activity Iteration Policy                                   |

| 7.3     | Deviation Policy 43                                         |

| 7.4     | Control Procedures                                          |

| 7.5     | Standards, Practices and Conventions 43                     |

| 8 V&    | V Documentation Requirements                                |

| 8.1     | RTM                                                         |

| 8.2     | Test Documents                                              |

| 9 VV    | P Maintenance                                               |

| Table A | , Compliance to SPP45                                       |

| Table B | , V&V Activities Assigned to Each Software Life Cycle Phase |

.

# 1 Introduction

# 1.1 Purpose

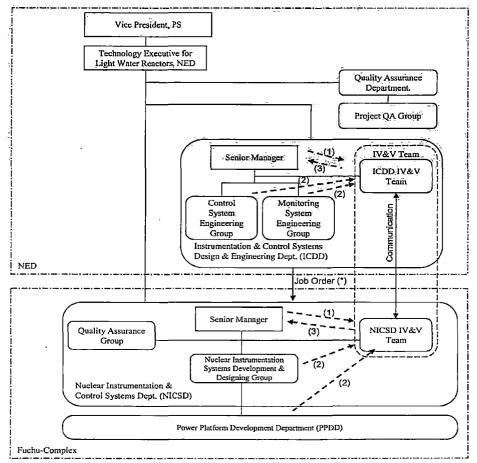

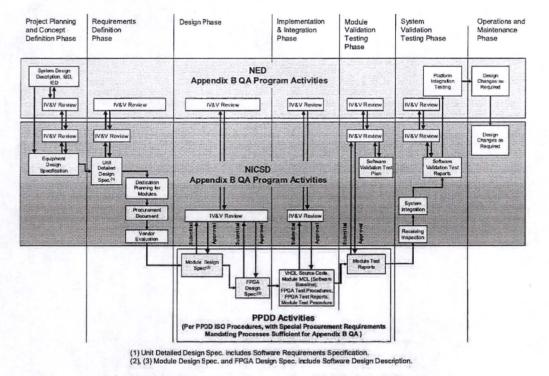

The Nuclear Instrumentation & Control Systems Department (NICSD) Verification and Validation (V&V) plan (NICSD VVP) is prepared for Non-Rewritable (NRW) Field Programmable Gate Array (FPGA)-based safety-related Instrumentation and Control (I&C) systems based on the Nuclear Energy Systems and Services Division (NED) V&V plan (NED VVP) (Reference (47)) to define the NICSD V&V activities.

The system design is determined by the Instrumentation & Control Systems Design and Engineering Department (ICDD) of Nuclear Energy Systems and Services Division (NED), and ICDD procures the FPGA-based equipment from Toshiba Fuchu Complex Power Systems Segment (Fuchu-PS) NICSD. NICSD procures major FPGA-based components, including modules with FPGA logic from the Toshiba Fuchu-PS Power Platform Development Department (PPDD) using a commercial grade dedication process.

For V&V of the FPGA-based safety-related I&C systems, ICDD and NICSD organize independent V&V (IV&V) Teams. The ICDD and NICSD IV&V Teams work together.

The software lifecycle process, including V&V, is defined in the project document "NICSD Software Management Plan for FPGA-based Safety-Related Systems" (NICSD SMP) (Reference (48)). This NICSD VVP covers the Section 4 "Software Verification and | Validation Program Plan" of the project document "Software Program Plan" (SPP) (Reference (45)). This NICSD VVP is prepared by the NICSD IV&V Team in accordance | with the following reference documents:

- NED, FA10-3709-0001 "Nuclear Energy Systems and Services Division FPGA-based Safety-Related Systems Verification and Validation Plan" (Reference (47))

- NED AS-200A130 "Digital System Verification & Validation Procedure" (Reference (12)), and

- NICSD NQ-2013 "Preparation Guide for V&V Plan" (Reference (17))

# 1.2 Scope

This NICSD VVP applies to the V&V activities for the FPGA-based safety-related I&C systems, which Toshiba will supply to US Nuclear Power Plants.

Section 4 of the project document "Software Program Plan," (SPP) (Reference (45)) establishes requirements and provides guidance and expectations for the V&V activities. This NICSD VVP complies with Section 4 of the SPP for the NICSD portions of the V&V activities. Table A shows compliance to Section 4 of the SPP.

TOSHIBA CORPORATION Nuclear Instrumentation & Control Systems Department

# 2 Definitions and Abbreviations

#### 2.1 Definitions

**Functional Element (FE):** A Functional Element is a component of digital logic that is completely verified and validated through full pattern testing, i.e. tests that are performed for all possible input combinations. An FE is written in Very High Speed Integrated Circuit Hardware Description Language (VHDL). All VHDL source codes for the NRW-FPGA-based System solely consist of FEs and interconnect between FEs.

Module: A part of a unit. Each module consists of one or more printed circuit boards, on which the FPGAs and other circuitry are mounted, and a front panel.

Netlist: Description of logics created by the logic synthesis tool. A design engineer describes FPGA logic in the form of VHDL source codes and FEs. The logic synthesis tool converts the VHDL source code into forms of digital circuits and outputs the resulting circuit in the form of a netlist. The layout tool transforms the netlist into physical placement of interconnects on the FPGA, which are represented as an FPGA fuse-map.

Unit: A major component of FPGA-based equipment. A unit is a chassis that has front slots and back slots to mount modules. Each unit consists of several modules. There is a vertical middle plane between the front and back slots in each unit. This plane consists of two circuit boards. These circuit boards provide backplanes for the front and rear modules. Modules plug into the backplanes using connectors. Once a module is plugged into the appropriate connector, it exchanges data with other modules in the unit, connects to other units and any external field equipment, and is powered.

**Validation:** Validation is used to ensure that the final product satisfies the user requirements. Validation shall be performed on the final product, although validation may be necessary or performed prior to the final code being produced. See Section 4.2 of the SPP (Reference (45)).

**Verification:** Verification consists of reviews performed on the results of each development phase to ensure the phase was completed appropriately and correctly. See Section 4.2 of the SPP (Reference (45)).

#### 2.2 Abbreviations

| BRR  | Baseline Review Report               |

|------|--------------------------------------|

| CAR  | Corrective Action Request            |

| CDR  | Critical Digital Review              |

| CFR  | Code of Federal Regulation           |

| СМ   | Configuration Management             |

| CG   | Commercial Grade                     |

| COTS | Commercial-Off-The-Shelf             |

| DCN  | Design Change Notice                 |

| DVR  | Design Verification Report           |

| ECWD | Elementary Control Wiring Diagram    |

| EDIF | Electronic Design Interchange Format |

TOSHIBA CORPORATION

Nuclear Instrumentation & Control Systems Department

| EDS      | Equipment Design Specification                                        |   |

|----------|-----------------------------------------------------------------------|---|

| ES       | Engineering Schedule                                                  |   |

| FE       | Functional Element                                                    |   |

| FPGA     | Field Programmable Gate Array (a programmable logic device)           |   |

| Fuchu-PS | Toshiba Fuchu Complex Power Systems Segment                           |   |

| I&C      | Instrumentation and Control                                           |   |

| IBD      | Interlock Block Diagram                                               |   |

| ICDD     | Instrumentation & Control Systems Design and Engineering Department   |   |

| IDE      | Integrated Development Environment                                    |   |

| IED      | Instrumentation Electrical Diagram                                    |   |

| IEEE     | Institute of Electrical and Electronics Engineers                     |   |

| IR       | Independent Reviewer                                                  |   |

| IV&V     | Independent Verification and Validation                               |   |

| MCL      | Master Configuration List                                             |   |

| NED      | Nuclear Energy Systems and Services Division                          |   |

| NICSD    | Nuclear Instrumentation & Control Systems Department                  |   |

| NISD     | Nuclear Instrumentation Systems Development & Designing Group         |   |

| NICS-QA  | Quality Assurance Group for Nuclear Instrumentation & Control Systems |   |

| NNR      | Nonconformance Notice Report                                          |   |

| NQ       | Nuclear Quality (standards for NICSD)                                 |   |

| PC       | Personal Computer                                                     |   |

| PCD      | Project Control Document                                              |   |

| PCDL     | Project Control Document List                                         | 1 |

| PDS      | Previously Developed Software                                         |   |

| PM       | Project Manager                                                       |   |

| PPDD     | Power Platform Development Department                                 |   |

| PRM      | Process Review Meeting                                                |   |

| PRS      | Problem Reporting Sheet                                               |   |

| PSNE     | Toshiba Corporation, Power Systems & Services Company, Nuclear Energy |   |

| QA       | Quality Assurance                                                     |   |

| QAD      | Quality Assurance Department                                          |   |

| QC       | Quality Control                                                       |   |

| RG       | Regulatory Guide                                                      |   |

| RTIS     | Reactor Trip and Isolation System                                     |   |

| RTM      | Requirements Traceability Matrix                                      |   |

|          |                                                                       |   |

| SBPR | Software Build Procedure and Report                                                                                             |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

|      | -                                                                                                                               |  |  |

| SSAR | Software Safety Analysis Report                                                                                                 |  |  |

| SCAR | Fuchu Site Corrective Action Request                                                                                            |  |  |

| SCMP | Software Quality Configuration Management Plan                                                                                  |  |  |

| SCSI | Small Computer System Interface                                                                                                 |  |  |

| SD   | Software Development                                                                                                            |  |  |

| SDD  | Software Design Description                                                                                                     |  |  |

| SDL  | Software Development Lead                                                                                                       |  |  |

| SDOE | Secure Development and Operational Environment                                                                                  |  |  |

| SIL  | Software Integrity Level                                                                                                        |  |  |

| SM   | Senior Manager                                                                                                                  |  |  |

| SMP  | Software Management Plan                                                                                                        |  |  |

| SQA  | Software Quality Assurance                                                                                                      |  |  |

| SQAP | Software Quality Assurance Management Plan                                                                                      |  |  |

| SRS  | Software: Requirements Specification                                                                                            |  |  |

| SPP  | Software Program Plan                                                                                                           |  |  |

| SVTP | Software Validation Test Plan                                                                                                   |  |  |

| SVTR | Software Validation Test Report                                                                                                 |  |  |

| V&V  | Verification and Validation                                                                                                     |  |  |

| VDCL | Vendor generated Document Check List                                                                                            |  |  |

| VFS  | Verification Follow Sheet                                                                                                       |  |  |

| VHDL | Very High Speed Integrated Circuit Hardware Definition Language (A hardware description language that defines the FPGA circuit) |  |  |

| VNNR | Vendor Nonconformance Notice Report                                                                                             |  |  |

| VVP  | Verification and Validation Plan                                                                                                |  |  |

| VVR  | Verification and Validation Report                                                                                              |  |  |

|      |                                                                                                                                 |  |  |

Table 3-1 of the NICSD SMP is provided for a better understanding of terminological difference between the SPP and NICSD SMP. This NICSD VVP also uses Table 3-1 of the NICSD SMP.

TOSHIBA CORPORATION Nuclear Instrumentation & Control Systems Department

# 3 Reference Documents

# 3.1 Code of Federal Regulations