# Safety System Digital Platform -MELTAC-

**Non Proprietary Version**

April 2011

©2011 Mitsubishi Heavy Industries, Ltd. All Rights Reserved

| Revision | Date              | Page<br>(Section) | Description                                       |

|----------|-------------------|-------------------|---------------------------------------------------|

| 0        | March 2007        | All               | Original issued                                   |

| 1        | July 2007         |                   | Refer to Revision History of JEXU-1012-1002-P(R1) |

| 2        | August 2008       |                   | Refer to Revision History of JEXU-1012-1002-P(R2) |

| 3        | December<br>2008  |                   | Refer to Revision History of JEXU-1012-1002-P(R3) |

| 4        | September<br>2009 |                   | Refer to Revision History of JEXU-1012-1002-P(R4) |

| 5        | April 2010        |                   | Refer to Revision History of JEXU-1012-1002-P(R5) |

| 6        | October<br>2010   |                   | Refer to Revision History of JEXU-1012-1002-P(R6) |

| 7        | April<br>2011     |                   | Refer to Revision History of JEXU-1012-1002-P(R7) |

### © 2011 MITSUBISHI HEAVY INDUSTRIES, LTD. All Rights Reserved

This document has been prepared by Mitsubishi Heavy Industries, Ltd. ("MHI") in connection with its request to the U.S. Nuclear Regulatory Commission ("NRC") for a pre-application review of the US-APWR nuclear power plant design. No right to disclose, use or copy any of the information in this document, other than by the NRC and its contractors in support of MHI's pre-application review of the US-APWR, is authorized without the express written permission of MHI.

This document contains technology information and intellectual property relating to the US-APWR and it is delivered to the NRC on the express condition that it not be disclosed, copied or reproduced in whole or in part, or used for the benefit of anyone other than MHI without the express written permission of MHI, except as set forth in the previous paragraph.

This document is protected by the laws of Japan, U.S. copyright law, international treaties and conventions, and the applicable laws of any country where it is being used.

Mitsubishi Heavy Industries, Ltd. 16-5, Konan 2-chome, Minato-ku Tokyo 108-8215 Japan

### <u>Abstract</u>

This topical report which is attached JEXU-1012-1002-P describes the MELTAC digital platform. MHI seeks NRC approval of this platform for application to the safety systems of the US-APWR and for replacement of current safety systems in operating plants. The MELTAC digital platform was developed by MHI and MELCO for nuclear power plants in Japan. For applications in the US, this report demonstrates conformance of the MELTAC digital platform to all applicable US Codes and Standards. These include:

- Code of Federal Regulations

- Regulatory Guides

- Branch Technical Positions

- NUREG-Series Publications

- IEEE-Standards

- Other Industry Standards

# Safety System Digital Platform - MELTAC -

Non-Proprietary Version

**April 2011**

© 2011 MITSUBISHI ELECTRIC CORPORATION All Rights Reserved

JEXU-1012-1002-NP(R7)

Prepared:

**Reviewed:**

Yukiko Hirano, Engineer

Control & Protection Systems Section

Control & Protection Systems Section

Yasuo Uranaka, Manage

'zo// Yasunobu Koga, Manage

2011 Date

**DCS Development Section**

25/2011

Makoto Ito, Manager

Date

DCS Development Section

Approved:

25/2011 MA v//

Hozumi Kadohara, Section Manager Control & Protection Systems Section

Masahiko Nambu, Section Manager **DCS Development Section**

Date

Approved:

Kadohara 4/25/2011

Hozumi Kadohara, Project Manager Nuclear Power Department

Date

Date

Approved:

Satoshi Nagao, Department Manager **Development Department**

26/2011 Date

Approved:

m26,2011

Hiroyuki Fukumitsu, Department Manager Nuclear Power Department

Approved:

pr. 26, 2011 Date

Masanori Sugita, Department Manager Nuclear Power Plant Quality Assurance Department

| <u>Signature</u> | <b>History</b> |

|------------------|----------------|

| -                |                |

|          | Rev.0             | Rev.1                   | Rev.2                   | Rev.3                   |

|----------|-------------------|-------------------------|-------------------------|-------------------------|

| Propored | Shigeru Sugitani  | Shigeru Sugitani        | Shigeru Sugitani        | Shigeru Sugitani        |

| Prepared | Tomonori Yamane   | Tomonori Yamane         | Tomonori Yamane         | Tomonori Yamane         |

| Reviewed | Tokihiro Fukuhara | Hidetoshi<br>Matsushita | Hidetoshi<br>Matsushita | Hidetoshi<br>Matsushita |

| Reviewed | Makoto Ito        | Makoto Ito              | Makoto Ito              | Makoto Ito              |

|          | Katsumi Akagi     | Tokihiro Fukuhara       | Tokihiro Fukuhara       | Tokihiro Fukuhara       |

|          | Hiroaki Ohno      | Hiroaki Ohno            | Hiroaki Ohno            | Hiroaki Ohno            |

| Approved | Kunio Yugami      | Toru Ito                | Toru Ito                | Toru Ito                |

| Approved | Keisuke Ichieda   | Keisuke Ichieda         | Keisuke Ichieda         | Keisuke Ichieda         |

|          | Masahiko Yamawaki | Shuichi Kobashi         | Shuichi Kobashi         | Shuichi Kobashi         |

|          | Yasuo Shiraishi   | Yasuo Shiraishi         | Tatsuaki Kawabata       | Tatsuaki Kawabata       |

|          | Rev.4                   | Rev.5                   | Rev.6                   |  |

|----------|-------------------------|-------------------------|-------------------------|--|

| Propored | Shigeru Sugitani        | Yukiko Hirano           | Yukiko Hirano           |  |

| Prepared | Yasunobu Koga           | Yasunobu Koga           | Yasunobu Koga           |  |

| Reviewed | Hidetoshi<br>Matsushita | Yasuo Uranaka           | Yasuo Uranaka           |  |

| Reviewed | Makoto Ito              | Makoto Ito              | Makoto Ito              |  |

|          | Tokihiro Fukuhara       | Hozumi Kadohara         | Hozumi Kadohara         |  |

|          | Masahiko Nambu          | Masahiko Nambu          | Masahiko Nambu          |  |

| Approved | Toru Ito                | Hidetoshi<br>Matsushita | Hidetoshi<br>Matsushita |  |

| Approved | Keisuke Ichieda         | Satoshi Nagao           | Satoshi Nagao           |  |

|          | Hiroyuki Fukumitsu      | Hiroyuki Fukumitsu      | Hiroyuki Fukumitsu      |  |

|          | Tatsuaki Kawabata       | Tatsuaki Kawabata       | Tatsuaki Kawabata       |  |

## **Revision History**

| Revision | Date       | Page<br>(section)       | Description                                                                                                                                                                             |

|----------|------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | March 2007 | All                     | Original issued                                                                                                                                                                         |

| 1        | July 2007  |                         | The following items are revised based on NRC comments or correction of simple spelling errors.                                                                                          |

|          |            | 47<br>(Sec.4.1.3.1)     | <ul><li>Figure 4.1-10 is modified.</li><li>Tool Communication is added.</li></ul>                                                                                                       |

|          |            | 51<br>(Sec.4.1.4)       | J<br>Description of the MELTAC engineering tool is modified.                                                                                                                            |

|          |            | 51,52<br>(Sec.4.1.4.1)  | Description of download is modified.<br>"Controller failure diagnosis display" is added.<br>"Adjustment of field changeable constants and<br>setpoints" is added.                       |

|          |            | 53<br>(Sec.4.1.4.2)     | Description of network for the MELTAC engineering<br>tool is modified.<br>Description of the communication interface between<br>Controller and the MELTAC engineering tool is<br>added. |

|          |            | 85,86,87<br>(Sec.4.3.4) | Description of Maintenance Network configuration and isolation are added.                                                                                                               |

|          |            |                         |                                                                                                                                                                                         |

|          |            | ſ                       | J                                                                                                                                                                                       |

|          |            |                         |                                                                                                                                                                                         |

|          |            | 125<br>(Sec.6.1.5)      | Spelling errors are corrected (They -> The)                                                                                                                                             |

| Revision | Date        | Page<br>(section)                | Description                                                                                         |

|----------|-------------|----------------------------------|-----------------------------------------------------------------------------------------------------|

| 1        | July 2007   |                                  |                                                                                                     |

|          |             | 141<br>(Sec.6.1.12)              | Spelling error is corrected (Plant -> Plan)                                                         |

| 2        | August 2008 | 34<br>(Sec.4.1.1.4)              | Table 4.1-2 is modified.<br>CE101 in EMC specifications is deleted.                                 |

|          |             | 96<br>(Sec.5.0)                  | The name of the EMC test report is changed.                                                         |

|          |             | 105<br>(Sec.5.3)                 | CE101 is deleted.<br>The acceptance criteria are modified.                                          |

|          |             | 106<br>(Sec.5.3)                 | The name of the EMC test report is changed.<br>CE101 is deleted.                                    |

|          |             | 108 -113<br>(Sec.5.3.2.1-<br>12) | Sec.5.3.2.1 CE101 Test is deleted.                                                                  |

|          |             | 108 - 110<br>(Sec.5.3.2.1-<br>9) | Spelling errors are corrected (envelop -> envelope)                                                 |

|          |             | 114, 115<br>(Sec.5.4)            | The acceptance criteria in the ESD test are modified.                                               |

|          |             | 116, 117<br>(Sec.6.1.1)          | ر<br>Reflecting the reorganization of the reference<br>internal quality assurance program documents |

|          |             |                                  |                                                                                                     |

|          |             |                                  |                                                                                                     |

|          |             |                                  |                                                                                                     |

| Revision | Data              | Page                                      | Description                                                                                                                                       |

|----------|-------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Date              | (section)                                 |                                                                                                                                                   |

| 3        | December<br>2008  | i                                         | Spelling error is corrected (that -> than).                                                                                                       |

|          |                   | 6,9,13<br>(Sec.3.0)                       | Descriptions in Paragraphs 6, 16, and 44 are revised in accordance with the response to RAI.                                                      |

|          |                   | 15,16,17,19<br>(Sec.3.0)                  | Paragraphs of the sections and procedures that include descriptions related to each standard are indicated. (Number 54, 55 – 57, 59, 61, 64 – 74) |

|          |                   | 18 – 20<br>(Sec.3.0)                      | Two standards (IEEE802.3 and IEEE802.17) are deleted and the paragraph numbers thereafter are reassigned.(Paragraphs 76 – 87)                     |

|          |                   | 84<br>(Sec.4.3.3.1)                       | Omission in writing in Figure 4.3-5 is corrected in accordance with the response to RAI.                                                          |

|          |                   | 97<br>(Sec.5.0)                           | Descriptions of environmental, seismic, and EMC test reports are added in accordance with the response to RAI.                                    |

|          |                   |                                           |                                                                                                                                                   |

|          |                   | 164<br>(Appendix<br>A.5)                  | Description of the accuracy of analog input is added<br>in accordance with the response to RAI on Safety<br>I&C System. (**)                      |

|          |                   | 168<br>(Appendix<br>A.8)                  | Error in writing is modified $(1.6A_{0-P} \rightarrow 16A_{0-P})$ .                                                                               |

| 4        | September<br>2009 | iii<br>(Abstract)                         | Abstract is modified.                                                                                                                             |

|          |                   | ix<br>(List of<br>Acronym)                | HICB is deleted.<br>DAAC and EEPROM are added.                                                                                                    |

|          |                   | 2<br>(Code of<br>Federal                  | Description of 10 CFR 50 Appendix A, GDC 1 is modified.                                                                                           |

|          |                   | Regulation 1)<br>6<br>(Code of<br>Federal | Description of 10 CFR 50.55a is modified.                                                                                                         |

|          |                   | Regulation 5)                             |                                                                                                                                                   |

| Revision | Date              | Page<br>(section)                                          | Description                                                                         |

|----------|-------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------|

| 4        | September<br>2009 | 7<br>(Code of<br>Federal                                   | Spelling error is corrected (Commision's -> Commission's).                          |

|          |                   | Regulation 8)<br>9<br>(NRC<br>Regulation                   | Description of RG1.75 is modified.                                                  |

|          |                   | Guides 15)<br>9<br>(NRC<br>Regulation                      | Description of RG1.105 is modified.                                                 |

|          |                   | Guides 19)<br>10 – 11<br>(NRC<br>Regulation<br>Guides 24 - | Description of RG1.168, 1.169, 1.170, 1.171, 1.172, 1.173 is modified.              |

|          |                   | 29)<br>12<br>(NRC<br>Regulation<br>Guides 30a)             | RG 1.206 is added.                                                                  |

|          |                   | 12-14<br>(NRC Branch<br>Technical                          | All items of "HICB" is changed to "7"<br>Item 44 is deleted.                        |

|          |                   | Positions)<br>17<br>(IEEE<br>Standards<br>60)              | Descriptions of 37, 38 and 48 are modified.<br>Description of IEEE 420 is modified. |

|          |                   | 25<br>(4.1.1.1)                                            | Description of Figure 4.1-2 is added.                                               |

|          |                   | 31<br>(4.1.1.2)                                            | Explanation for Failure Mode is added.                                              |

|          |                   | 34<br>(4.1.1.3)                                            | Explanation of Cycle time is added in Table 4.1-1.                                  |

|          |                   | 39<br>(4.1.2.1.1)                                          | Explanation of Futurebus+ is added.                                                 |

|          |                   | 40<br>(4.1.2.1.6)                                          | Description of PPNJ-12 is modified.                                                 |

|          |                   | 43<br>(4.1.2.3)                                            | Figure 4.1-8, Figure 4.1-9 and description are added.                               |

|          |                   |                                                            |                                                                                     |

| Revision | Date      | Page<br>(section)                  | Description                                                                       |

|----------|-----------|------------------------------------|-----------------------------------------------------------------------------------|

| 4        | September | 45                                 | Description of E/O converter is modified.                                         |

|          | 2009      | (4.1.2.5)<br>46<br>(4.1.2.7.2)     | Description of Power supply fan units is added.                                   |

|          |           | (4.1.2.7.3)<br>46, 47<br>(4.1.2.8) | Description of Power supply module is added.                                      |

|          |           | (4.1.2.0)                          | ١                                                                                 |

|          |           |                                    |                                                                                   |

|          |           |                                    | ر<br>ار                                                                           |

|          |           | 55                                 | J<br>Description is added.                                                        |

|          |           | (4.1.3.2)                          | J                                                                                 |

|          |           | 65                                 | J<br>Section 4.1.5.6 is added.                                                    |

|          |           | (4.1.5.6)<br>65, 66                | Section 4.1.6 is added.                                                           |

|          |           | (4.1.6)<br>66 - 68                 | Section 4.1.7 is added.                                                           |

|          |           | (4.1.7)<br>70<br>(4.2.1.2.1),      | Description is added.                                                             |

|          |           | (4.2.1.2.1),<br>74<br>(4.2.2.1)    | Additional explanation for interruption is added.                                 |

|          |           | (4.2.4)                            | Section 4.2.4 is added.                                                           |

|          |           | 83<br>(4.3.2)                      | Example of inter divisional communication between safety and non-safety is added. |

|          |           | (4.0.2)                            |                                                                                   |

|          |           | L<br>85, 86                        |                                                                                   |

|          |           | (4.3.2.1)                          | Wording is modified in Figure 4.3-1, 4.3-2.                                       |

|          |           | 86<br>(4.3.2.1)                    | Explanation for bypass function of optical switch about Figure4.3-2 is added.     |

|          |           | 87, 88<br>(4.3.2.1)                | Figure4.3-3 and explanation of optical switch failure mode are added.             |

|          |           | 89<br>(4.3.2.2)                    | Optical cable specification is added in Table4.3-2.                               |

|          |           | Í                                  |                                                                                   |

|          |           |                                    |                                                                                   |

|          |           |                                    |                                                                                   |

| Revision | Date              | Page<br>(section) | Description                                                                                                          |

|----------|-------------------|-------------------|----------------------------------------------------------------------------------------------------------------------|

| 4        | September<br>2009 |                   |                                                                                                                      |

|          |                   |                   |                                                                                                                      |

|          |                   |                   |                                                                                                                      |

|          |                   | 102<br>(4.4)      | Additional explanation of self-diagnosis is added.                                                                   |

|          |                   |                   | Wording is modified.<br>(BTP HICB-21 -> BTP 7-21)                                                                    |

|          |                   | 110<br>(5.0)      | Isolation qualification is added.                                                                                    |

|          |                   | 115<br>(5.2.2.1)  | Description of the configuration of the Cabinet Seismic Resistance Test specimen is added.                           |

|          |                   | 119<br>(5.2.2.2)  | Descriptions of the Module Seismic Resistance<br>Test are modified.<br>Optical Switch and Ethernet Optical Isolation |

|          |                   | 123<br>(5.3.1)    | Device are added.<br>The model name of safety VDU panel is changed.                                                  |

|          |                   |                   |                                                                                                                      |

| Revision | Dete              | Page              | Description |

|----------|-------------------|-------------------|-------------|

|          | Date              | Page<br>(section) |             |

| 4        | September<br>2009 |                   |             |

|          |                   |                   |             |

|          |                   |                   |             |

|          |                   |                   |             |

|          |                   |                   | )<br>)      |

|          |                   |                   |             |

|          |                   |                   |             |

|          |                   |                   |             |

|          |                   |                   |             |

| Revision | Date              | Page<br>(section) | Description                |

|----------|-------------------|-------------------|----------------------------|

| 4        | September<br>2009 | 156<br>(6.1.6.4)  | Section title is modified. |

|          |                   |                   |                            |

|          |                   |                   |                            |

|          |                   |                   |                            |

|          |                   |                   |                            |

|          |                   |                   |                            |

|          |                   |                   |                            |

|          |                   |                   |                            |

|          |                   |                   | <br>                       |

|          |                   | Ì                 |                            |

| Revision | Date              | Page                               | Description                                                                                                                                |

|----------|-------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | September<br>2009 | (section)                          |                                                                                                                                            |

|          |                   | (<br>176, 177<br>(7.1)             | Description of "History of Operation" is modified.<br>Table 7.1-1, the summary for history of changes of<br>the MELTAC platform, is added. |

|          |                   | 189<br>(7.5)                       | Description for replacement cycle of Periodic replacement Parts is added.                                                                  |

|          |                   | 190<br>(Appendix                   | Explanation about the modules is added.                                                                                                    |

|          |                   | A)<br>190<br>(Appendix<br>A.2)     | Description of firmware is added.                                                                                                          |

|          |                   | 191<br>(Appendix<br>A.4)           | Description of firmware is added.                                                                                                          |

|          |                   | 192, 194, 196<br>(Appendix<br>A.5) | Descriptions of firmware and current consumption are added.                                                                                |

|          |                   | 197<br>(Appendix<br>A.6)           | Description of current consumption is added.                                                                                               |

|          |                   | 197<br>(Appendix<br>A.7)           | Description of current consumption is added.<br>Specification of MEOJ-11 is added.                                                         |

|          |                   | 198<br>(Appendix<br>A.8)           | Description of current consumption is added.                                                                                               |

|          |                   | 199<br>(Appendix<br>A.10)          | Description of current consumption is added.                                                                                               |

|          |                   | 200<br>(Appendix<br>B)             | Explanation of the list is added.                                                                                                          |

|          |                   |                                    |                                                                                                                                            |

| Revision |            | Page                                                                                                                       | Description                                                                                                                                  |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|          | Date       | (section)                                                                                                                  |                                                                                                                                              |

| 5        | April 2010 | ii, 3, 4, 5, 6,<br>7, 8, 10, 11,<br>12, 13, 15,<br>16, 19, 20,<br>22, 118, 146,<br>154, 164,<br>168, 169,<br>170, 186, 193 | Document names are modified.<br>(Design Process Topical Report, Safety System<br>Topical Report -> Technical Report for the US-<br>APWR DCD) |

|          |            | 14<br>(NRC Branch<br>Technical<br>Positions 46)<br>31,32                                                                   | Description of conformance to BTP 7-18 is modified.<br>Explanation of Mode Management is added.                                              |

|          |            | (4.1.1.2.1)                                                                                                                | Description of Figure 4.1-5 is modified.                                                                                                     |

|          |            | 33,34<br>(4.1.1.2.2)                                                                                                       | Explanation of Mode Management is added.<br>Description of Figure 4.1-6 is modified.                                                         |

|          |            | 59<br>(4.1.4.2)                                                                                                            | Description of Network for the MELTAC engineering tool is modified.                                                                          |

|          |            |                                                                                                                            |                                                                                                                                              |

|          |            | 67<br>(4.1.6)                                                                                                              | Error in writing is modified.<br>(64 -> 96)                                                                                                  |

|          |            | ſ                                                                                                                          |                                                                                                                                              |

|          |            | 101<br>(4.3.4.2)                                                                                                           | Section 4.3.4.2, Isolation, is modified.                                                                                                     |

|          |            |                                                                                                                            |                                                                                                                                              |

|          |            | 142<br>(6.1.1)                                                                                                             | Wording is modified.                                                                                                                         |

|          |            |                                                                                                                            | Add description about hardware procured or manufactured prior to the App. B-based QAP.                                                       |

|          |            | 150<br>(6.1.4)                                                                                                             | Wording is modified.<br>(V&V -> independent review and test)                                                                                 |

|          |            |                                                                                                                            |                                                                                                                                              |

|          |            | Ç                                                                                                                          | Ĵ                                                                                                                                            |

|          |            |                                                                                                                            |                                                                                                                                              |

| Revision | Date            | Page                     | Description                                                                                                             |

|----------|-----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 5        | April 2010      | (section)                | ٦                                                                                                                       |

|          |                 |                          | J                                                                                                                       |

|          |                 |                          |                                                                                                                         |

|          |                 |                          |                                                                                                                         |

|          |                 | 181<br>(6.5)             | Section 6.5, MELTAC Engineering Tool Life Cycle, is added.                                                              |

|          |                 |                          |                                                                                                                         |

|          |                 | 205<br>(Appendix<br>A.7) | Description of Ethernet Optical Isolation Module is added.                                                              |

| 6        | October<br>2010 | 14<br>(3.0)              | "App. B- Based" is changed to "App.B-based".                                                                            |

|          | 2010            | (3.0)<br>22<br>(4.0)     | "Engineering Tool" and "Maintenance Network" are deleted from the items of qualified building blocks.                   |

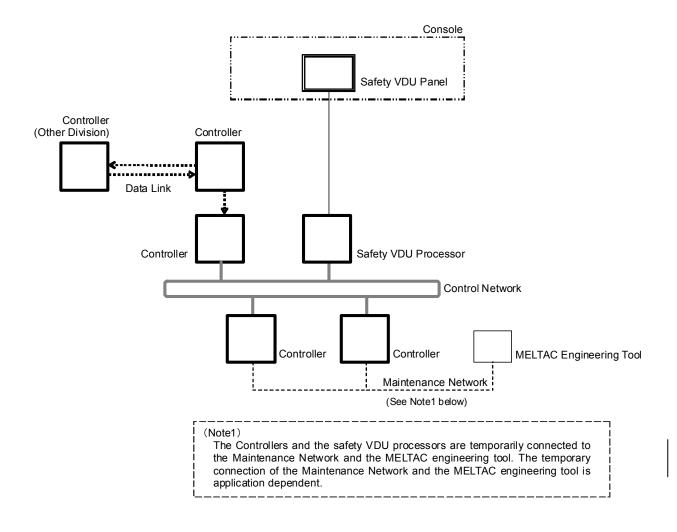

|          |                 | 22<br>(4.0)              | The note of the Maintenance Network is added in Fig4.0-1.                                                               |

|          |                 | 35<br>(4.1.1.3)          | Description of Input/Output in Table 4.1-1 is modified.                                                                 |

|          |                 | ſ                        | ٦                                                                                                                       |

|          |                 | 57,58<br>(4.1.4.1)       | ر<br>Descriptions of "b)Download" and "e)Adjustment of<br>field changeable constants and setpoints" are<br>modified.    |

|          |                 | 59<br>(4.1.4.2)          | Descriptions of the permanent or temporary connection of the MELTAC engineering tool and Maintenance Network are added. |

|          |                 |                          |                                                                                                                         |

|          |                 | L                        | ر                                                                                                                       |

|          |                 | 86,88<br>(4.3.2.1)       | The arrows for "Optical Cable" in Fig4.3-1 and Fig4.3-2 are corrected.                                                  |

|          |                 | 87<br>(4.3.2.1)          | Description of the key technical aspects of the Control Network is added.                                               |

|          |                 | 101<br>(4.3.4.1)         | Descriptions of the MELTAC engineering tool connected to the Maintenance Network are modified and added.                |

|          |                 | 101<br>(4.3.4.1)         | The note of the Maintenance Network is added in Fig4.3-8.                                                               |

|          |                 |                          |                                                                                                                         |

|          |                 | 103<br>(4.3.4.2)         | Figure 4.3-9 is modified.                                                                                               |

| Revision |                 | Page                | Description                                                                                                                                       |

|----------|-----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Date            | (section)           |                                                                                                                                                   |

| 6        | October<br>2010 | 104<br>(4.3.4.2)    | Figure 4.1-10 "Dedicated Re-programming Chassis for Writing F-ROM" is added.                                                                      |

|          |                 | 105<br>(4.3.4.2)    | Descriptions of the controller connected to the Maintenance Network are modified.                                                                 |

|          |                 | 106<br>(4.3.4.3)    | The title of Section 4.3.4.3 is changed from "Design<br>Basis of Permanent Connection" to "Design Basis of<br>Permanent or Temporary Connection". |

|          |                 |                     | ر<br>ا                                                                                                                                            |

|          |                 |                     |                                                                                                                                                   |

|          |                 |                     |                                                                                                                                                   |

|          |                 |                     | J                                                                                                                                                 |

|          |                 |                     | Í                                                                                                                                                 |

|          |                 |                     | j                                                                                                                                                 |

|          |                 | ĺ                   |                                                                                                                                                   |

|          |                 | 180<br>(6.3, 6.3.1) | "B Based" in the titles of Section 6.3 and Section 6.3.1 are changed to "B-based".                                                                |

|          |                 |                     |                                                                                                                                                   |

|          |                 |                     |                                                                                                                                                   |

| 7        | April 2011      | general             | All sections are revised to unify the terminology.                                                                                                |

|          |                 | general             | Descriptions of this report are modified.<br>Topical Report -> Technical Report                                                                   |

|          |                 |                     |                                                                                                                                                   |

|          |                 |                     |                                                                                                                                                   |

|          |                 |                     |                                                                                                                                                   |

|          |                 | 58<br>(4.1.4.1)     | Explanation of Download is added.                                                                                                                 |

| Revision           | Date               | Page<br>(section)                               | Description                                                                |

|--------------------|--------------------|-------------------------------------------------|----------------------------------------------------------------------------|

| Revision         7 | Date<br>April 2011 | (section) ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( | Section 4.3.2.5 is added.                                                  |

|                    |                    |                                                 |                                                                            |

|                    |                    |                                                 |                                                                            |

|                    |                    |                                                 |                                                                            |

|                    |                    | 189, 194<br>(6.1.6)                             | The term "cyber security" is changed to "secure development environment ". |

| Revision | Date       | Page<br>(section)                          | Description                                                                                                                                                               |

|----------|------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7        | April 2011 | 207<br>(6.1.12)                            | The terms "software safety plan/analysis" are changed to "software critical function analysis ".                                                                          |

|          |            | 216<br>(6.4)<br>220<br>(6.5)               | The title of Section 6.4 is changed from "BTP 7-14<br>Assessment" to "Basic Software Program Manual".<br>Description of MELTAC Engineering Tool life cycle<br>is revised. |

|          |            | 257<br>(Appendix D)<br>260<br>(Appendix E) | Appendix D is added.<br>Appendix E is added.                                                                                                                              |

|          |            | 298<br>(Appendix F)                        | Appendix F is added.                                                                                                                                                      |

### © 2011 MITSUBISHI ELECTRIC CORPORATION All Rights Reserved

This document has been prepared by Mitsubishi Electric Corporation ("MELCO") in connection with Mitsubishi Heavy Industries, LTD. ("MHI")'s request to the U.S. Nuclear Regulatory Commission ("NRC") for a pre-application review of the US-APWR nuclear power plant design. No right to disclose, use or copy any of the information in this document, other than by the NRC and its contractors in support of MHI's pre-application review of the US-APWR, is authorized without the express written permission of MELCO.

This document contains technology information and intellectual property relating to the MELCO's Safety System Digital Platform (MELTAC) and it is delivered to the NRC on the express condition that it not be disclosed, copied or reproduced in whole or in part, or used for the benefit of anyone other than MELCO without the express written permission of MELCO, except as set forth in the previous paragraph.

This document is protected by the laws of Japan, U.S. copyright law, international treaties and conventions, and the applicable laws of any country where it is being used.

Mitsubishi Electric Corporation 7-3, Marunouchi 2-chome, Chiyoda-ku Tokyo 100-8310 Japan

### Abstract

This Technical Report describes the design of the Mitsubishi Electric Total Advanced Controller (MELTAC) Platform and its conformance to the U.S. Nuclear Regulatory requirements for nuclear safety systems. The MELTAC platform is the basis of the Mitsubishi Heavy Industries (MHI) safety and non-safety digital I&C systems.

The MELTAC platform was developed specifically for nuclear applications. The modular structure, deterministic response time and testability can be applied to solve plant-wide needs for safety and non-safety applications. Moreover the MELTAC platform has been developed using a rigorous safety-related design process that ensures suitable hardware and software quality and reliability for critical applications such as the reactor protection system or engineered safety features actuation system.

The MELTAC platform has accumulated many years of positive performance records in various non-safety system applications such as the Plant Control and Monitoring System in nuclear plants operating in Japan. Based on its excellent performance in numerous non-safety applications, the MELTAC platform has now been applied to almost all systems throughout Japanese PWR nuclear plants under construction. These systems were shipped to the site recently.

The goal of this report is to seek approval from the U.S. Nuclear Regulatory Commission (NRC) for the use of the MELTAC platform for nuclear safety systems in new reactors (US-APWR).

For applications in the US, this report demonstrates conformance of the Design and Design Process to all applicable US Codes and Standards. These include:

- Code of Federal Regulations

- Regulatory Guides

- Branch Technical Positions

- NUREG-Series Publications

- IEEE-Standards

- Other Industry Standards

The information provided in this report covers the following topics to fully understand the MELTAC platform:

- The design of the hardware, software, communication network and application development tools of the MELTAC platform

- The equipment qualification of the MELTAC platform and its conformance to the corresponding U.S. standards

- The life cycle and the Quality Assurance Program of the MELTAC platform conformed to U.S. regulations

- The history of operation and the equipment reliabilities of the MELTAC platform

The complete MHI digital I&C design is described in Topical Reports and a Technical Report for the US-APWR DCD:

- Safety I&C System Description and Design Process (Technical Report for the US-APWR DCD)

- Safety System Digital Platform MELTAC (this report)

- HSI System Description and HFE (Human Factor Engineering) Process

- Defense in Depth and Diversity

The information in this Digital Platform Technical Reports is expected to be sufficient to allow the NRC to make a final safety determination regarding the suitability of the MELTAC platform for safety-related nuclear applications, on the condition of completing specific application engineering as identified in the other topical reports. Other documentation which has been generated during the MELTAC design process is available for NRC audit, as may be needed to allow the NRC to confirm the MELCO design and design process, as documented in this Technical Report.

# Table of Contents

| List of Tables                                                          |      |

|-------------------------------------------------------------------------|------|

| List of Figures                                                         | xxii |

| List of Acronyms                                                        | xxiv |

|                                                                         |      |

| 1.0 PURPOSE                                                             |      |

| 2.0 SCOPE                                                               |      |

| 3.0 APPLICABLE CODE, STANDARDS AND REGULATORY GUIDANCE                  |      |

| 4.0 MELTAC PLATFORM DESCRIPTION                                         |      |

| 4.1 Controller                                                          |      |

| 4.1.1 Hardware Configuration                                            |      |

| 4.1.2 Hardware Descriptions                                             |      |

| 4.1.3 Software                                                          |      |

| 4.1.4 MELTAC Engineering Tool                                           |      |

| 4.1.5 Self-Diagnosis                                                    | 61   |

| 4.1.6 Bus inside the controller                                         |      |

| 4.1.7 Manual test                                                       |      |

| 4.2 Safety VDU Panel and Processor                                      |      |

| 4.2.1 Hardware                                                          |      |

| 4.2.2 Software                                                          |      |

| 4.2.3 Self-Diagnosis                                                    |      |

| 4.2.4 Manual test                                                       |      |

| 4.3 Communication System                                                |      |

| 4.3.1 General Description                                               |      |

| 4.3.2 Control Network                                                   |      |

| 4.3.3 Data Link                                                         |      |

| 4.3.4 Maintenance Network                                               |      |

| 4.4 Response Time                                                       |      |

| 4.4.1 Processing Time of MELTAC Fundamental Cycle                       |      |

| 4.4.2 Processing Time of MELTAC Application                             | 139  |

| 4.4.3 Examples of Response Time Calculations                            | 143  |

| 4.5 Control of Access                                                   |      |

| 4.5.1 Control of Access for Hardware                                    |      |

| 4.5.2 Control of Access for Software                                    |      |

| 4.6 Elimination or Relaxation of Surveillance                           | 146  |

| 5.0 ENVIRONMENTAL, SEISMIC, ELECTROMAGNETIC AND ISOLATION QUALIFICATION | 147  |

| 5.1 Environmental Test                                                  | 147  |

| 5.1.1 Environmental Specification and Outline of Test                   | 147  |

| 5.1.2 Contents of Environmental Test                                    |      |

| 5.2 Seismic Test                                                        |      |

| 5.2.1 Overview                                                          |      |

| 5.2.2 Seismic Resistance Test                                           |      |

| 5.3 Electromagnetic Compatibility and Radio Frequency Interference      |      |

| 5.3.1 Test Configuration                                                |      |

| 5.3.2 Description of Tests                                              |      |

| 5.4 Electrostatic Discharge Test                                        |      |

|                                                                         |      |

| 5.5 Isolation Test                                                                                                                          | 169 |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.0 LIFE CYCLE                                                                                                                              | 173 |

| 6.1 Life Cycle Process                                                                                                                      |     |

| 6.1.1 Overview of the MELTAC Quality Assurance Program                                                                                      | 175 |

| 6.1.2 Quality Assurance Program Rev 2                                                                                                       |     |

| 6.1.3 Management                                                                                                                            | 180 |

| 6.1.4 Development                                                                                                                           | 181 |

| 6.1.5 Configuration Management                                                                                                              | 186 |

| 6.1.6 Secure Development Environment Management                                                                                             |     |

| 6.1.7 US Conformance Program for Previously Developed Components                                                                            |     |

| 6.1.8 Software Installation                                                                                                                 | 199 |

| 6.1.9 Maintenance                                                                                                                           |     |

| 6.1.10 Training                                                                                                                             |     |

| 6.1.11 Operations                                                                                                                           |     |

| 6.1.12 Software Critical Function Analysis                                                                                                  |     |

| 6.2 Life Cycle Management                                                                                                                   |     |

| 6.2.1 Quality Records Management                                                                                                            |     |

| 6.2.2 Failure and Error Reporting and Corrective Action                                                                                     |     |

| 6.2.3 Obsolescence Management                                                                                                               |     |

| 6.2.4 Identification                                                                                                                        |     |

| 6.2.5 Reliability Database                                                                                                                  |     |

| 6.3 Establishment of 10 CFR Part 50 Appendix B-based QA Program, and MELTAC Re-                                                             |     |

| evaluation Program                                                                                                                          |     |

| 6.3.1 Establishment of 10 CFR Part 50 Appendix B-based QA Program                                                                           |     |

| 6.3.2 MELTAC Re-evaluation Program.                                                                                                         |     |

| 6.4 Basic Software Program Manual                                                                                                           |     |

| 6.5 MELTAC Engineering Tool Life Cycle                                                                                                      |     |

| 7.0 EQUIPMENT RELIABILITY                                                                                                                   | 217 |

| 7.1 History of Operation                                                                                                                    |     |

| 7.2 Mean Time between Failures (MTBF) Analysis                                                                                              |     |

| 7.3 Controller Reliability Analysis                                                                                                         |     |

| 7.3.1 Reliability Model                                                                                                                     |     |

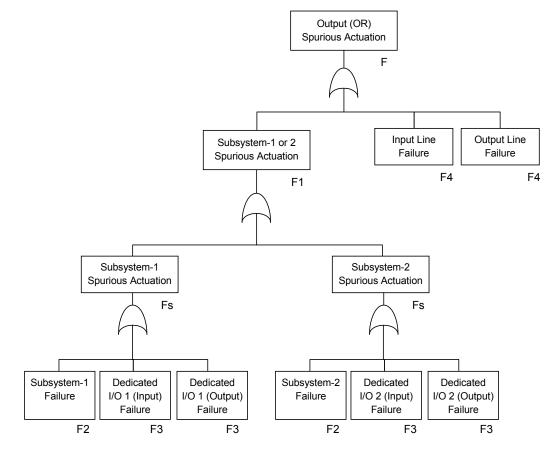

| 7.3.2 FTA for Spurious Actuation of the Safety Function                                                                                     |     |

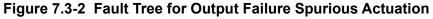

| 7.3.3 FTA of Failure to Actuate the Safety Function                                                                                         |     |

| 7.3.4 Detailed Controller Reliability Analysis                                                                                              |     |

| 7.4 Failure Mode and Effects Analysis (FMEA)                                                                                                |     |

|                                                                                                                                             |     |

| <ul><li>7.5 Periodic Replacement Equipment (Parts) to Keep Reliability</li><li>7.6 Performance history of self-diagnosis function</li></ul> |     |

| APPENDIX A HARDWARE SPECIFICATIONS                                                                                                          |     |

| Appendix A.1 CPU Module PCPJ-11 Specification                                                                                               |     |

|                                                                                                                                             |     |

| Appendix A.2 System Management Module Specification<br>Appendix A.3 Bus Master Module Specification                                         | 200 |

|                                                                                                                                             |     |

| Appendix A.4 Control Network I/F Module Specification                                                                                       |     |

| Appendix A.5 I/O Module Specification                                                                                                       |     |

| Appendix A.6 Isolation Module Specifications                                                                                                |     |

| Appendix A.7 E/O Converter Modules Specifications.                                                                                          |     |

| Appendix A.8 Power Interface Modules Specifications                                                                                         |     |

| Appendix A.9 Power Supply Modules Specifications                                                                                            |     |

| Appendix A.10 Safety VDU Panel Specification                                                                                                |     |

| Appendix A.11 FMU Module Specification                                                                                                      |     |

| Appendix A.12 Touch Panel Interface Module Specification                                                                                    | 243 |

| APPENDIX B FUNCTIONAL SYMBOL SOFTWARE SPECIFICATIONS | 244 |

|------------------------------------------------------|-----|

| APPENDIX C CONFORMANCE TO BTP 7-14                   | 252 |

| APPENDIX D CONFORMANCE MAP OF ISG-04 CHAPTER 1       | 257 |

| APPENDIX E SOFTWARE CRITICAL FUNCTION ANALYSIS       | 260 |

| APPENDIX F DEFINITION                                | 298 |

## List of Tables

| Table 4.0-1 Typical Configuration of MELTAC Platform                             | 22  |

|----------------------------------------------------------------------------------|-----|

| Table 4.1-1 Scale and Capacity                                                   | 35  |

| Table 4.1-2 Environmental Specifications                                         | 36  |

| Table 4.1-3 Module in the CPU Chassis                                            | 38  |

| Table 4.1-4 CPU Chassis                                                          | 39  |

| Table 4.1-5 Cabinet of MELTAC Platform Specifications                            | 49  |

| Table 4.1-6 Bus inside the controller                                            | 68  |

| Table 4.1-7 I/O bus specification                                                |     |

| Table 4.2-1 Explanation of the Screen                                            | 79  |

| Table 4.2-2 Data Details                                                         |     |

| Table 4.3-1 Configuration of Control Network                                     |     |

| Table 4.3-2 The Specification of Control Network                                 |     |

| Table 4.3-3 Self-Diagnosis Functions of Control Network                          |     |

| Table 4.3-4 The Specification of Data Link Communication                         |     |

| Table 4.4-1 Description of Processing in Each Component (maximum/minimum values) |     |

| Table 5.3-1 MELTAC Modules for the EMC Test                                      |     |

| Table 6.1-1 QA Procedures                                                        |     |

| Table 6.1-2 Contents of Activity in Each Phase                                   |     |

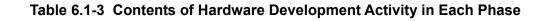

| Table 6.1-3 Contents of Hardware Development Activity in Each Phase              |     |

| Table 6.1-4 Security Measures of the Software Development/Storage Environment    |     |

| Table 6.1-5 Security Measures in the Software Development Process                |     |

| Table 6.1-6 Information Provided in the MELTAC Maintenance Manual                |     |

| Table 6.1-7 Hardware Measurement                                                 |     |

| Table 6.1-8 Software Upgrades Relation                                           |     |

| Table 6.1-9 Possible Hazards                                                     |     |

| Table 6.3-1 Relationship Between App.B-based QAP and Previous QAP                |     |

| Table 7.1-1 The summary for history of changes of the MELTAC platform            |     |

| Table 7.2-1 Failure rate of modules                                              |     |

| Table 7.5-1 List of Periodic Replacement Parts                                   |     |

| Table 7.6-1 Number of failures                                                   | 232 |

## List of Figures

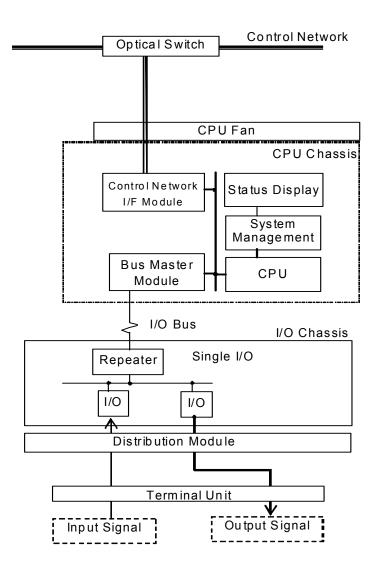

| Figure 4.1-1 Single Controller Configuration                                        | . 24 |

|-------------------------------------------------------------------------------------|------|

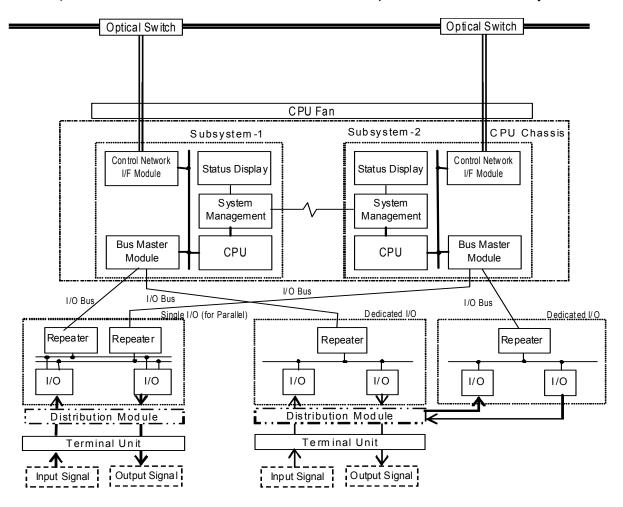

| Figure 4.1-2 Redundant Parallel Controller Configuration                            | . 26 |

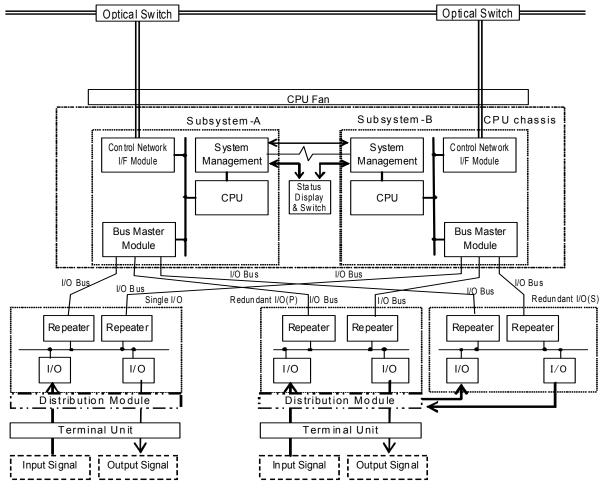

| Figure 4.1-3 Redundant Standby Controller Configuration                             | . 28 |

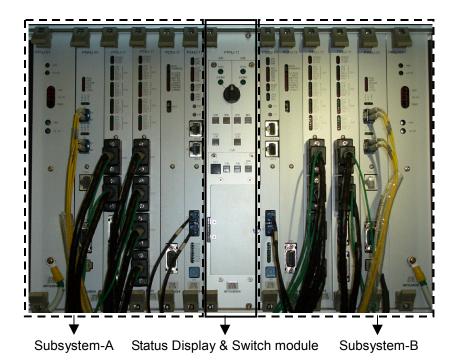

| Figure 4.1-4 Picture of Modules in a CPU Chassis for a Redundant Standby Controller |      |

| Configuration                                                                       | . 29 |

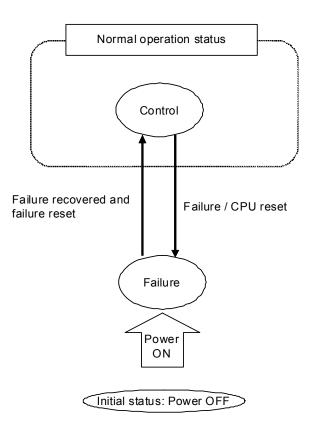

| Figure 4.1-5 Mode Management of Single Controller and Redundant Parallel            | . 31 |

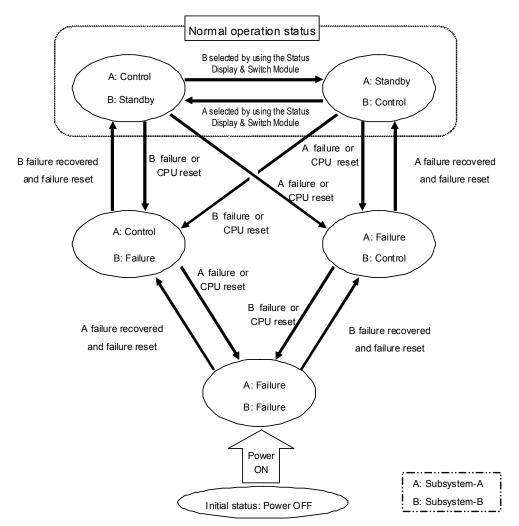

| Figure 4.1-6 Mode Management of Redundant Standby Controller                        | . 33 |

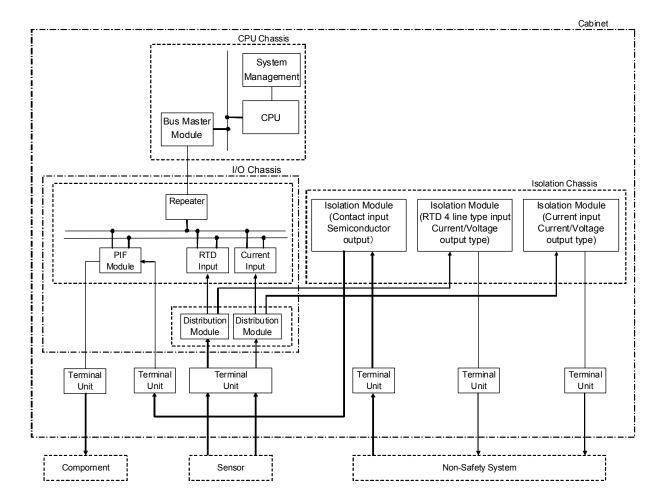

| Figure 4.1-7 Location of Isolation Module                                           |      |

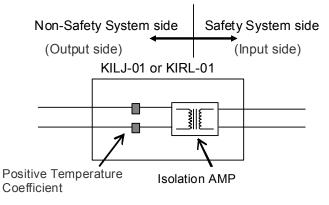

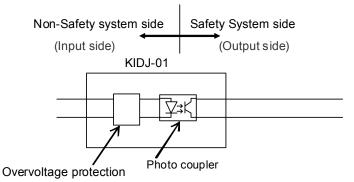

| Figure 4.1-8 The Internal Configuration Diagram of The Analog Isolation Modules     | . 44 |

| Figure 4.1-9 The Internal Configuration Diagram of The Digital Isolation Module     | . 44 |

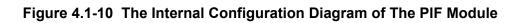

| Figure 4.1-10 The Internal Configuration Diagram of The PIF Module                  |      |

| Figure 4.1-11 Cabinet External Dimensions and Rack Up, Typical Sample A             | . 50 |

| Figure 4.1-12 Cabinet External Dimensions and Rack Up, Typical Sample B             | . 51 |

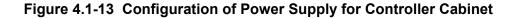

| Figure 4.1-13 Configuration of Power Supply for Controller Cabinet                  | . 52 |

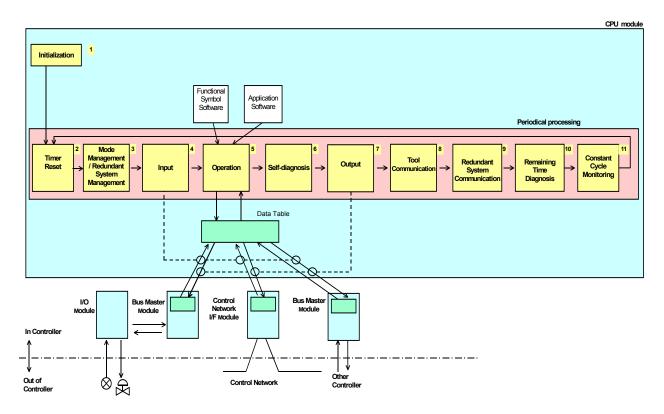

| Figure 4.1-14 Basic Software Processes and Execution Order                          | . 53 |

| Figure 4.1-15 Remaining Time Diagnosis                                              |      |

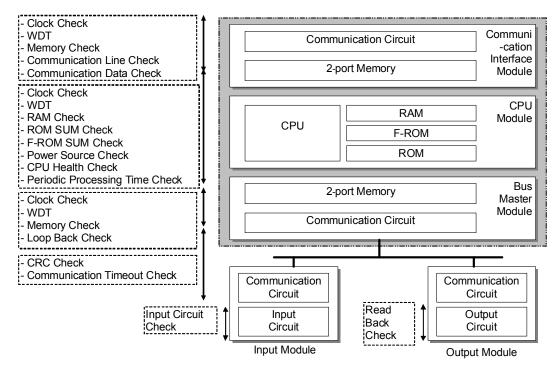

| Figure 4.1-16 Coverage of Self-diagnosis function of the controller                 |      |

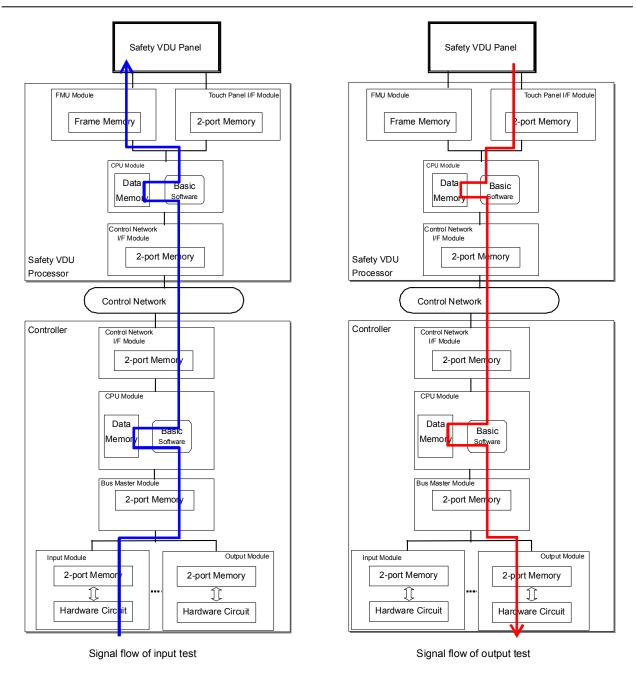

| Figure 4.1-17 Manual test for process input and output                              |      |

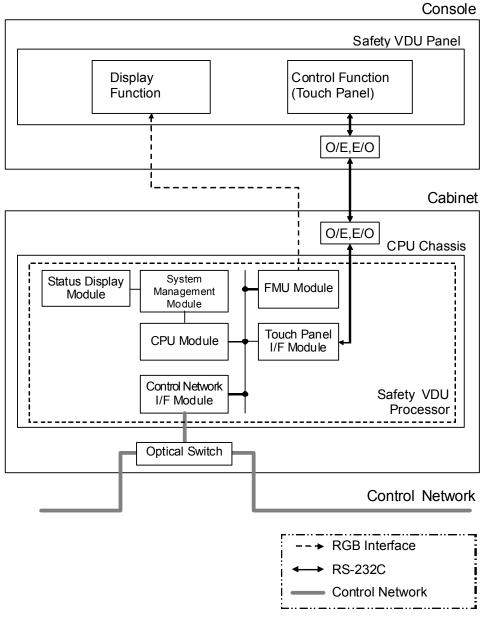

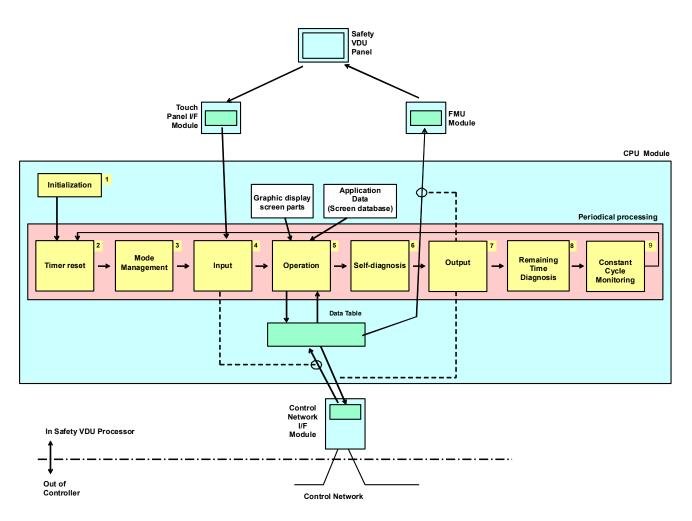

| Figure 4.2-1 Configuration of Safety VDU Processor                                  |      |

| Figure 4.2-2 Configuration of Power Supply for Safety VDU                           | . 75 |

| Figure 4.2-3 Software Structure of Safety VDU Processor                             |      |

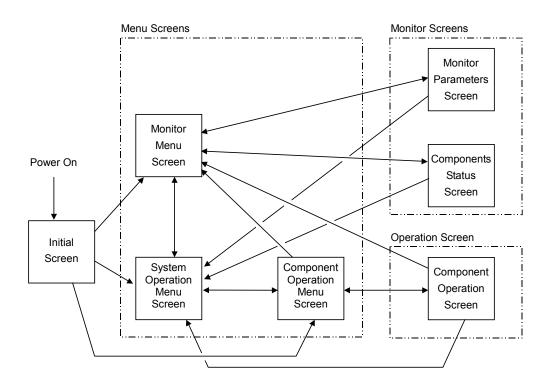

| Figure 4.2-4 Screen Transition of the Safety VDU Processor                          |      |

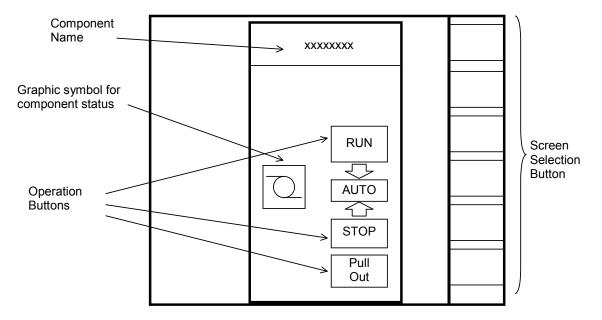

| Figure 4.2-5 A Sample of Operation Switch Pictogram on the Safety VDU Panel         |      |

| Figure 4.2-6 Explanation of the Safety VDU Processor Operation                      |      |

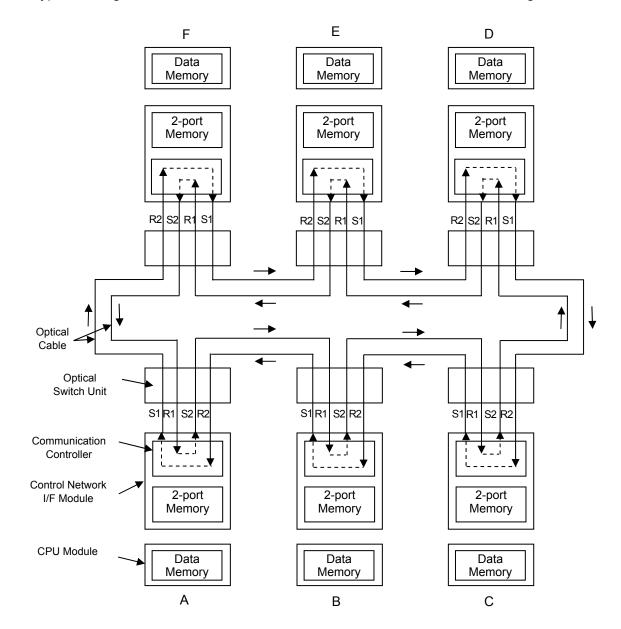

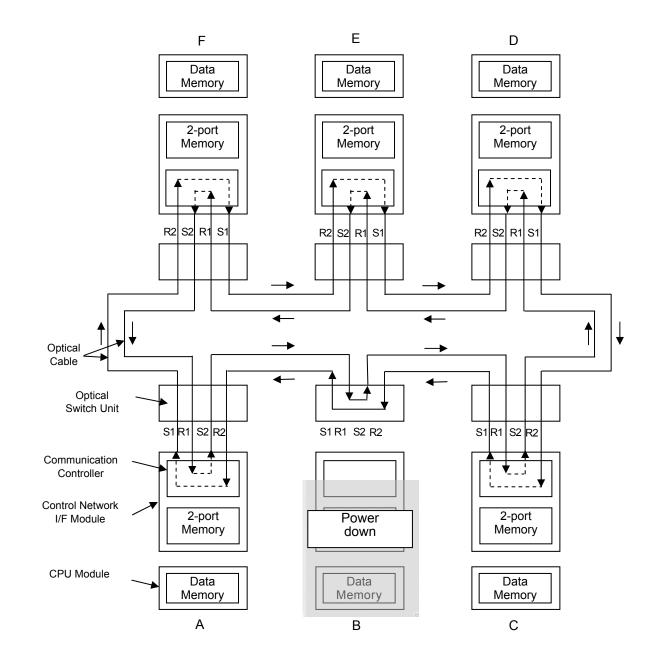

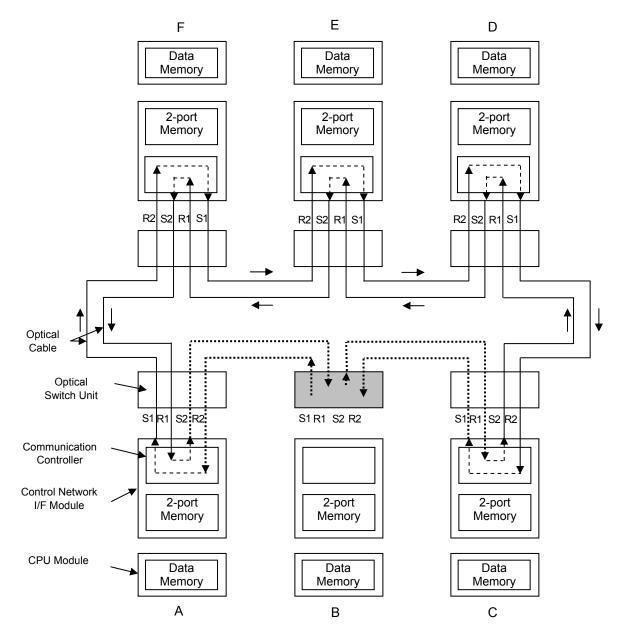

| Figure 4.3-1 Configuration of Control Network                                       |      |

| Figure 4.3-2 Explanation of Bypass Operation by the Optical Switch                  |      |

| Figure 4.3-3 Explanation of Optical Switch Failure                                  |      |

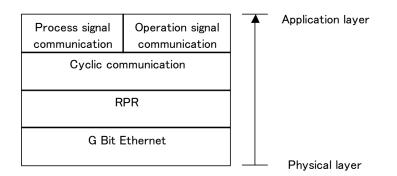

| Figure 4.3-4 Protocol Stack of Control Network                                      |      |

| Figure 4.3-5 Separation in Communication of Control Network                         |      |

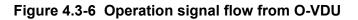

| Figure 4.3-6 Operation signal flow from O-VDU                                       |      |

| Figure 4.3-7 Process signal flow from RPS to Unit Bus                               |      |

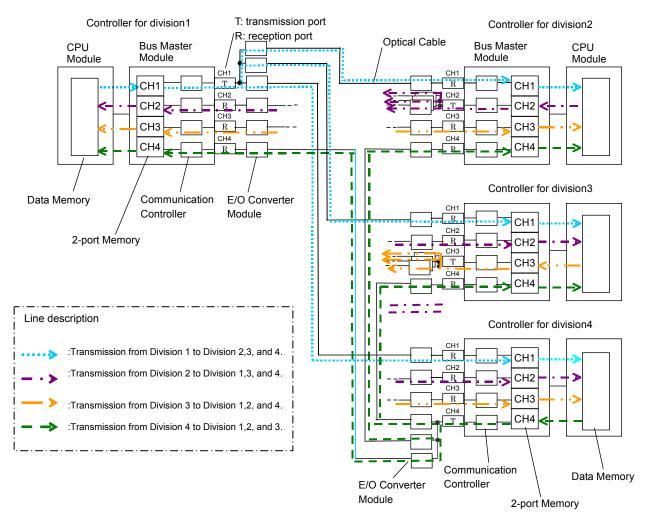

| Figure 4.3-8 Detail signal flow in COM (Receiving process)                          |      |

| Figure 4.3-9 Detail signal flow in RPS (Sending process)                            |      |

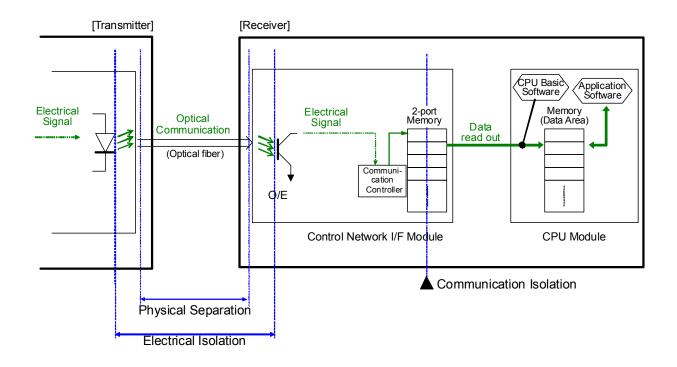

| Figure 4.3-10 Processing by the Control Network I/F Module                          |      |

| Figure 4.3-11 Processing by the main CPU                                            |      |

| Figure 4.3-12 Processing by the main CPU                                            |      |

| Figure 4.3-13 Processing by the Control Network I/F Module                          |      |

| Figure 4.3-14 Example of Connection Configuration of Data Link Configuration        | 115  |

| Figure 4.3-15 Separation in Communication of Data Link                              |      |

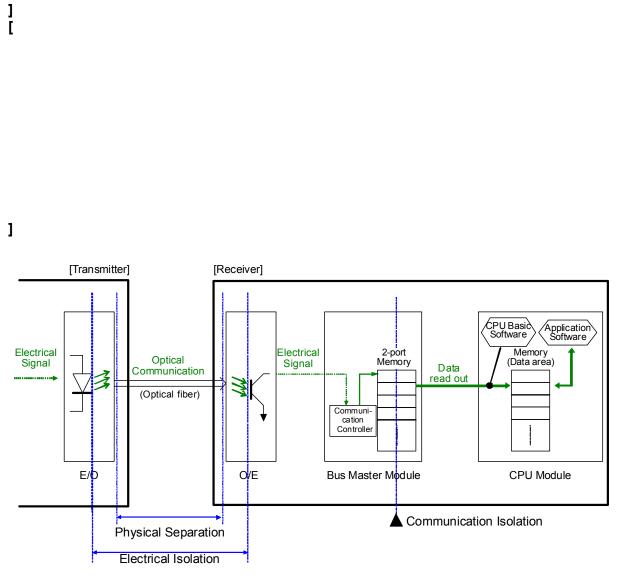

| Figure 4.3-16 Partial Trip signal flow between RPSs                                 |      |

| Figure 4.3-17 Detail signal flow in RPS (Receiving process)                         |      |

| Figure 4.3-18 Detail signal flow in RPS (Sending process).                          |      |

| Figure 4.3-19 Processing by the Bus Master Module                                   |      |

| Figure 4.3-20 Processing by the main CPU                                            | 125  |

| Figure 4.3-21 Processing by the main CPU                                            | 127  |

| Figure 4.3-22 Processing by the Bus Master Module                                   | 129  |

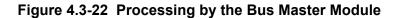

| Figure 4.3-23 Maintenance Network Configuration                                     | 132  |

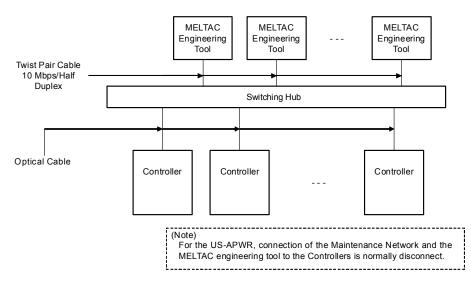

| Figure 4.3-24 Separation in Communication of Maintenance Network                           | 34 |

|--------------------------------------------------------------------------------------------|----|

| Figure 4.3-25 Dedicated Re-programming Chassis for Writing F-ROM                           | 35 |

| Figure 4.4-1 The Time Chart of Fundamental Process in Cyclic                               | 38 |

| Figure 4.4-2 Internal Process Divisions of the MELTAC Platform to Perform Response Time    |    |

| Calculations14                                                                             |    |

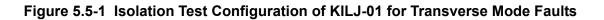

| Figure 5.5-1 Isolation Test Configuration of KILJ-01 for Transverse Mode Faults            | 70 |

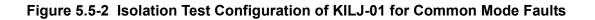

| Figure 5.5-2 Isolation Test Configuration of KILJ-01 for Common Mode Faults                | 70 |

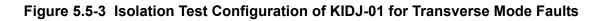

| Figure 5.5-3 Isolation Test Configuration of KIDJ-01 for Transverse Mode Faults            | 71 |

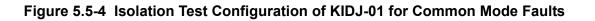

| Figure 5.5-4 Isolation Test Configuration of KIDJ-01 for Common Mode Faults 17             | 71 |

| Figure 6.1-1 Outline of In-house QA Procedures System and Relationship of Various Plans 17 | 78 |

| Figure 6.1-2 Outline of Software Development Plan 18                                       | 32 |

| Figure 6.1-3 Outline of Problem Tracking/Resolution Process                                | 34 |

| Figure 6.1-4 Security Measures of the Software Development/Storage Environment 19          | 90 |

| Figure 6.1-5 Software Installation 20                                                      | 01 |

| Figure 7.1-1 MELTAC Development and Operating History                                      | 19 |

| Figure 7.3-1 Reliability Model 22                                                          | 23 |

| Figure 7.3-2 Fault Tree for Output Failure Spurious Actuation                              | 24 |

| Figure 7.3-3 Fault Tree for Failure to Actuate 22                                          | 25 |

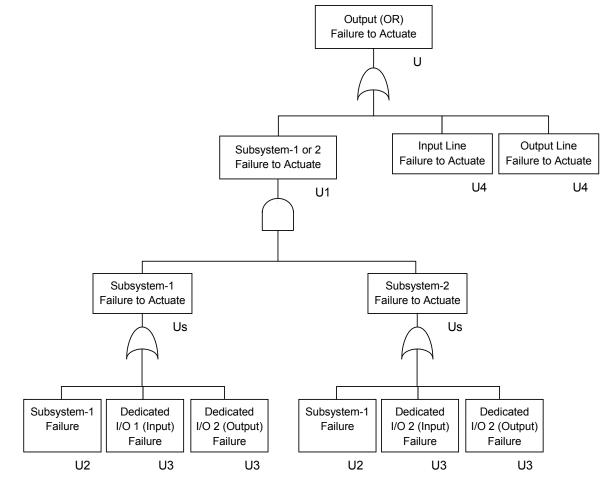

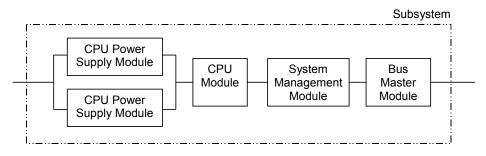

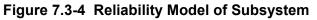

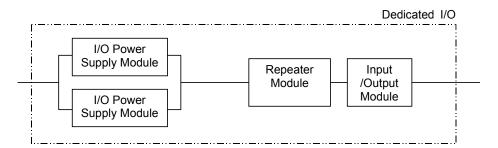

| Figure 7.3-4 Reliability Model of Subsystem 22                                             | 26 |

| Figure 7.3-5 Fault Tree of Subsystem 22                                                    | 26 |

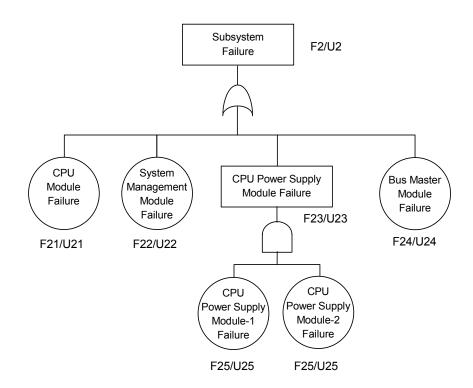

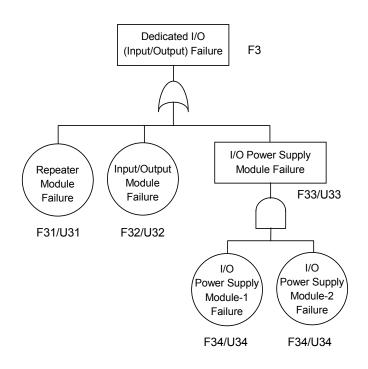

| Figure 7.3-6 Reliability Model of Dedicated I/O 22                                         | 27 |

| Figure 7.3-7 Fault Tree of Dedicated I/O 22                                                | 27 |

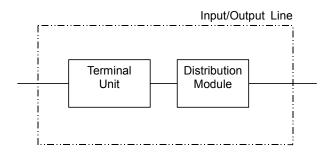

| Figure 7.3-8 Input/Output Line 22                                                          | 28 |

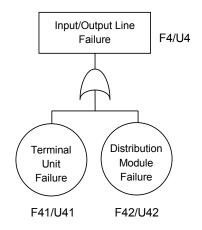

| Figure 7.3-9 Fault Tree of Input/Output Line 22                                            | 28 |

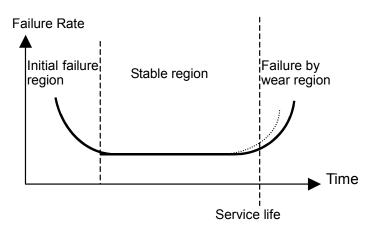

| Figure 7.5-1 Failure Rate Curve                                                            |    |

## List of Acronyms

| AI          | Analog Input                                              |

|-------------|-----------------------------------------------------------|

| ANSI        | American National Standards Institute                     |

| AO          | Analog Output                                             |

| ASME        | American Society of Mechanical Engineers                  |

| ATWS        | Anticipated Transient without Scram                       |

| BTP         | Branch Technical Position                                 |

| CEAS        | MELCO Corporate Electronic Archive System                 |

| CFR         | Code of Federal Regulations                               |

| COTS        | Commercial Off The Shelf                                  |

| CPU         | Central Processing Unit                                   |

| CRC         | Cyclic Redundancy Check                                   |

| CSMA/CD     | Carrier Sense Multiple Access with Collision Detection    |

| DAAC<br>DAC | Diverse Automatic Actuation Cabinet                       |

| DAC         | Design Acceptance Criteria                                |

| DBA         | Diverse Actuation System<br>Design Basis Accident         |

| DI          | Digital Input                                             |

| DO          | Digital Output                                            |

| DSP         | Digital Signal Processor                                  |

| EEPROM      | Electronically Erasable Programmable Read Only Memory     |

| EMC         | Electromagnetic Compatibility                             |

| EMI         | Electromagnetic Interference                              |

| ESC         | Energy Systems Center in Mitsubishi Electric Corporation  |

| ESD         | Electrostatic Discharge                                   |

| ESFAS       | Engineered Safety Features Actuation System               |

| EUT         | Equipment under Test                                      |

| E/O         | Electrical / Optical                                      |

| FBD         | Functional Block Diagram                                  |

| FMEA        | Failure Mode and Effect Analysis                          |

| FMU         | Frame Memory Unit                                         |

| F-ROM       | Flash Electrically Erasable Programmable Read Only Memory |

| GBD         | Graphic Block Diagram                                     |

| GDC         | General Design Criteria                                   |

| GUI         | Graphic User Interface                                    |

| HSI<br>ID   | Human System Interface<br>Identification                  |

| IEC         | International Electrotechnical Commission                 |

| IEEE        | Institute of Electrical and Electronics Engineers         |

| IPL         | Interposing Logic                                         |

| ISO         | International Standardization Organization                |

| IT          | Information Technology                                    |

| ITAAC       | Inspection, Test, Analysis, and Acceptance Criteria       |