# DRS Consolidated Controls PLµS 32 Distributed Control System

U.S. Nuclear Regulatory Commission October 2009

Project Number: 778 DRS-2009-01 Attachment 3-NI

#### Presentation Segments

- Introduction

- Nuclear Quality Assurance

2

- Design Process

- Hardware Design

- Software Design

- Application Software

- Plant Applications

- Qualification

- <u>Cyber Security</u>

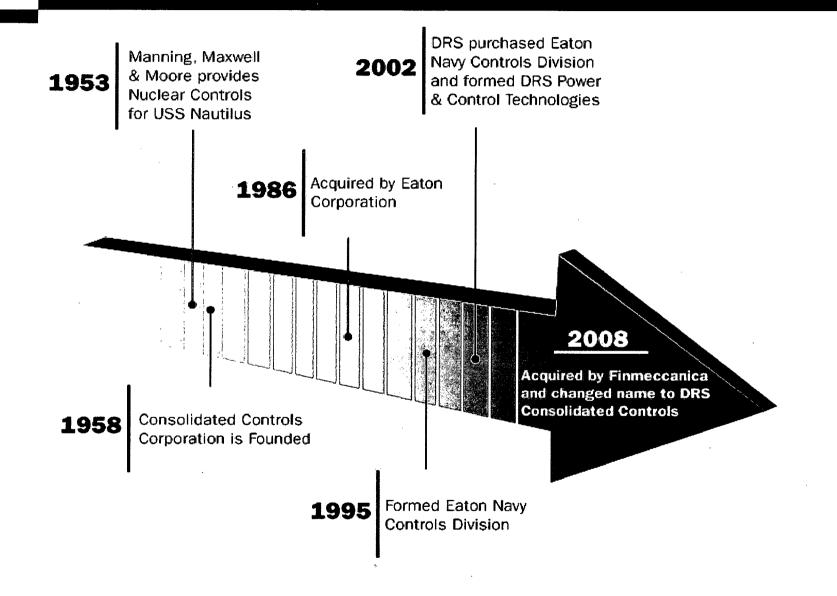

#### Consolidated Controls History

- DRS acquired by Finmeccanica for \$5.2B in October 2008.

- Business units segregated to assure foreign ownership control or influence mitigation is achieved.

- Danbury business name returned to legacy Consolidated Controls

#### **DRS Locations in the United States**

#### Key Products

•

- **Commercial Nuclear Controls**

- ATWS (Anticipated Transient Without Scram)

- ESFAS (Engineered Safety Features Actuation System)

- EDLS (Emergency Diesel Logic Sequence

- MSFR (Main Steam Feed Water Regulator

- ESF (Engineered Safety Features

- EFW (Emergency Feed Water)

- SSLC (Safety System Logic Control)

- BOP (Balance of Plant)

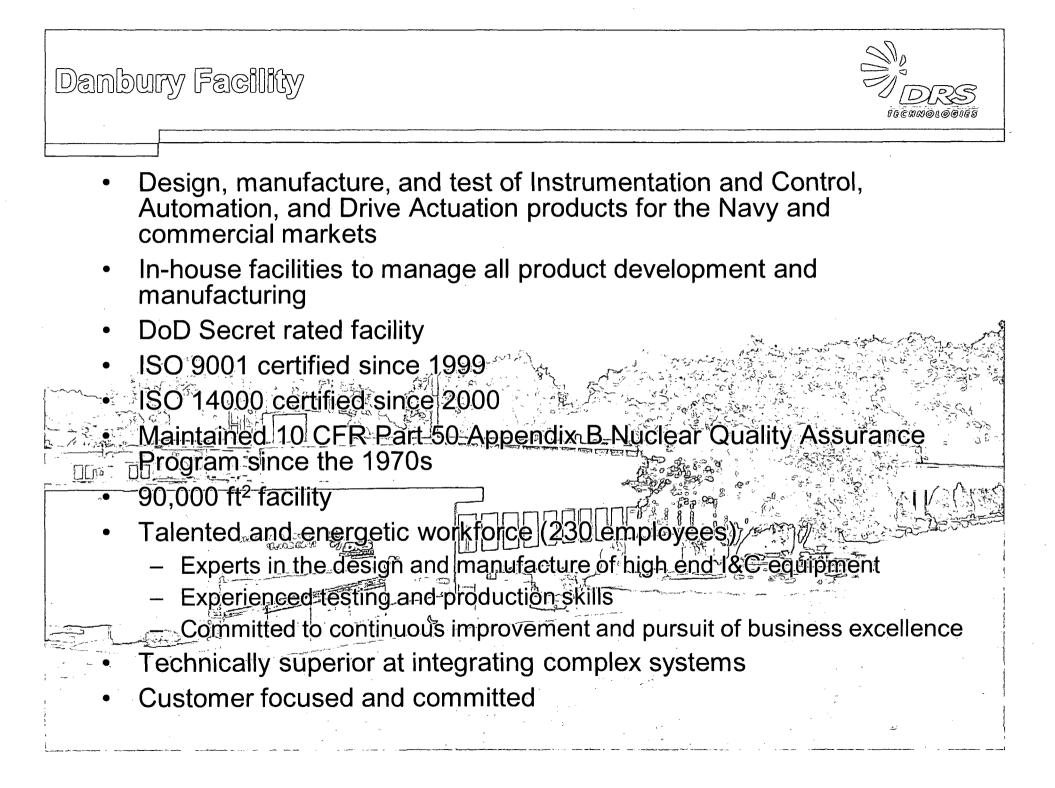

#### Design, Development, and Test Capabilities

8

- DRS has substantial capabilities to develop, manufacture and test electronic equipment

- Facilities

- Development laboratory

- Environmental chambers

- Capable Personnel

- Equipment

- State of art design tools for design and analysis

- All processes executed per :

- NQA for Commercial Nuclear or

- ISO 9001 Procedures

- Navy's world-class power electronics supplier of choice

- Number One Supplier of I&C Equipment

- 50 Years of experience

- Expertise in Commercial Nuclear Controls (over 37 years)

DRS

**To Production Deliverable**

Internationally Recognized

#### **International Commercial Nuclear Plants with DRS Controls**

- Taiwan Power Co.

- Korea Electric Power Co.

- Taiwan Power Co.

- Maanshan 1&2 (W-PWR)(SSLC)

- Kori 3&4 (W-PWR) (SSLC, BOP, ESFAS, MSI)

- Yonggwang 1&2 (W-PWR) (SSLC, BOP, ESFAS, MSI)

- Ulchin 3&4 (KHI/CE-PWR) (ESF/BOP)

- Yonggwang 5&6 (KHI/CE-PWR) (ESF/BOP)

- GE Lungmen 1 & 2 ESF Controls

#### Domestically Chosen By The Nuclear Power Industry

#### **U.S. Commercial Nuclear Plants with DRS Controls**

- Millstone 1&2 (ATWS, ESFAS)

- Saint Lucie 1&2 (ESFAS)

- Davis Besse (ESFAS, MSFR)

- Callaway (ESFAS, EDLS)

- Wolf Creek (ESFAS, EDLS)

- Hope Creek (SSLC, EDLS)

- Arkansas Nuclear One (EFW)

- Vogtle 1&2 (EDLS)

- Shearon Harris (IS)

- Seabrook (MSI)

- Salem 1&2 (EDLS)

- DRS offers products and services to keep nuclear power plants operating safely and competitively worldwide.

- Extensive engineering / test capacities supporting

- Complete design engineering

- Obsolescence redesign and qualification of single components

or entire systems

- Design consulting providing solutions to complex problems

- Field service to support deployed systems

- To Move Forward Toward Seeking Placement on NRC Docket - DRS TR Submittal to NRC in 2-4 Weeks

- Shall Cover A System That Has Been Designed & Qualified For Nuclear Safety-Related, Class 1E Applications - <u>Is Not A Commercial Off The Shelf</u> <u>System</u>

- Shall Focus on: Supplementing Utilities' Licensing Efforts

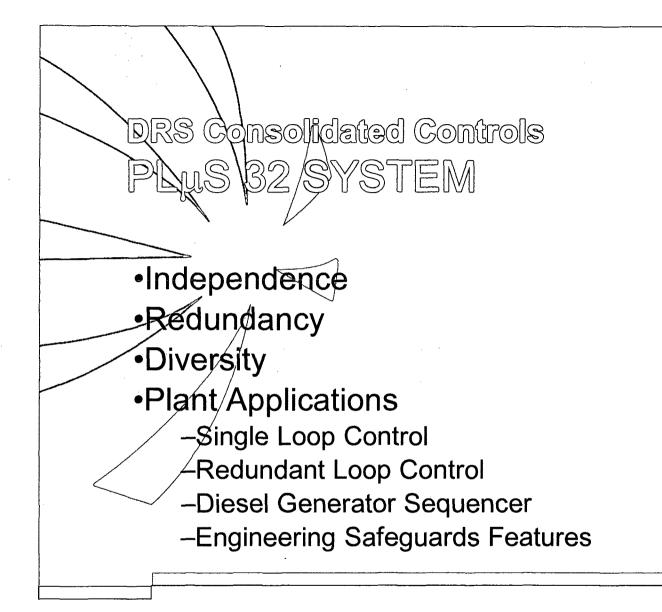

- The PLµS 32 System Is Based on:

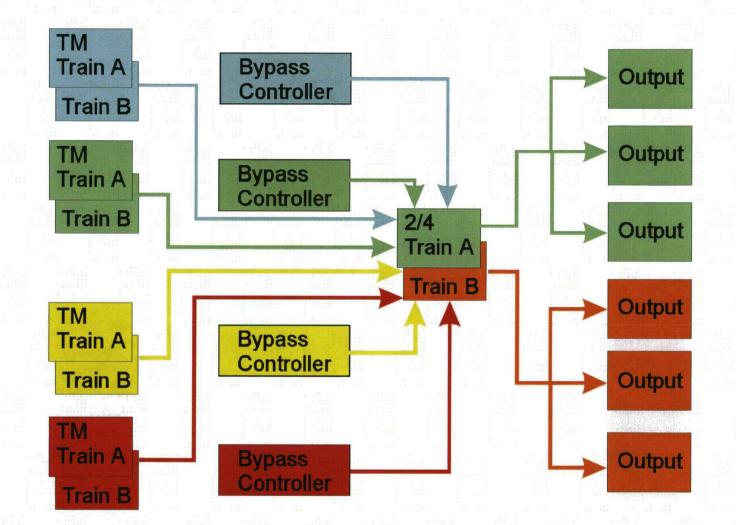

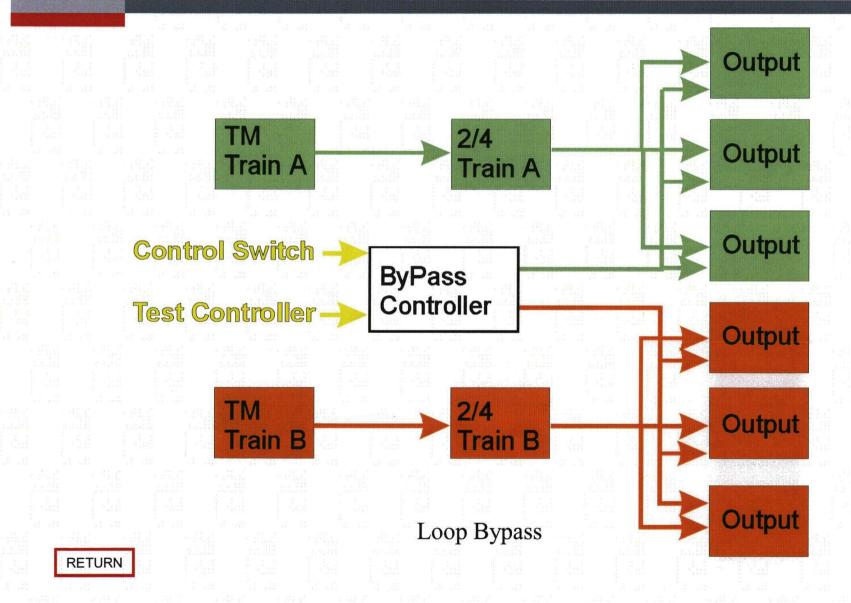

- 1.0 Safety & Redundancy

- 2.0 Safety & Redundancy

- 3.0 Safety & Redundancy

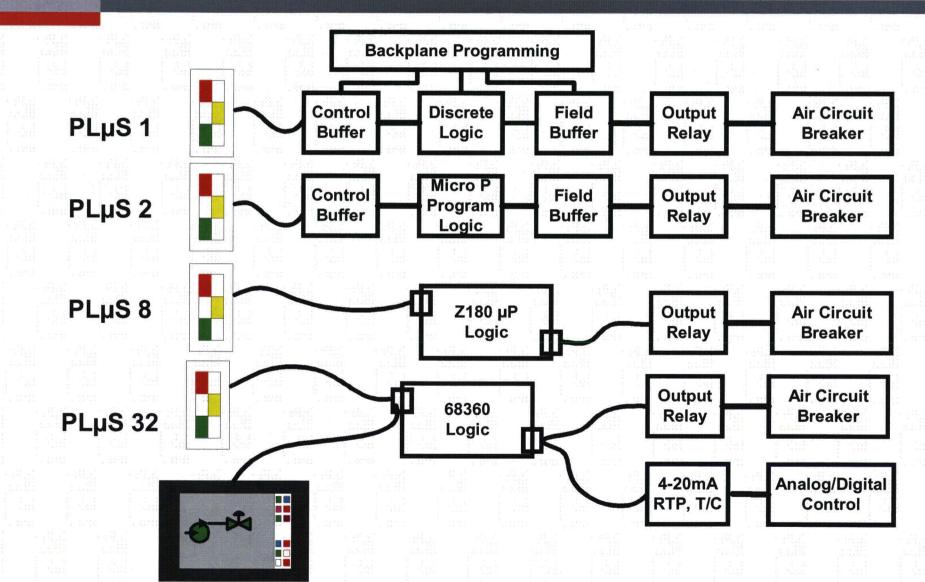

# Generations of The PLµS Series

15

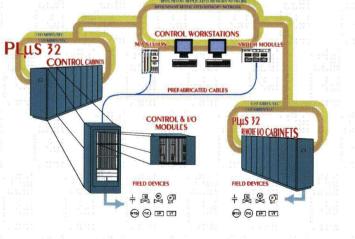

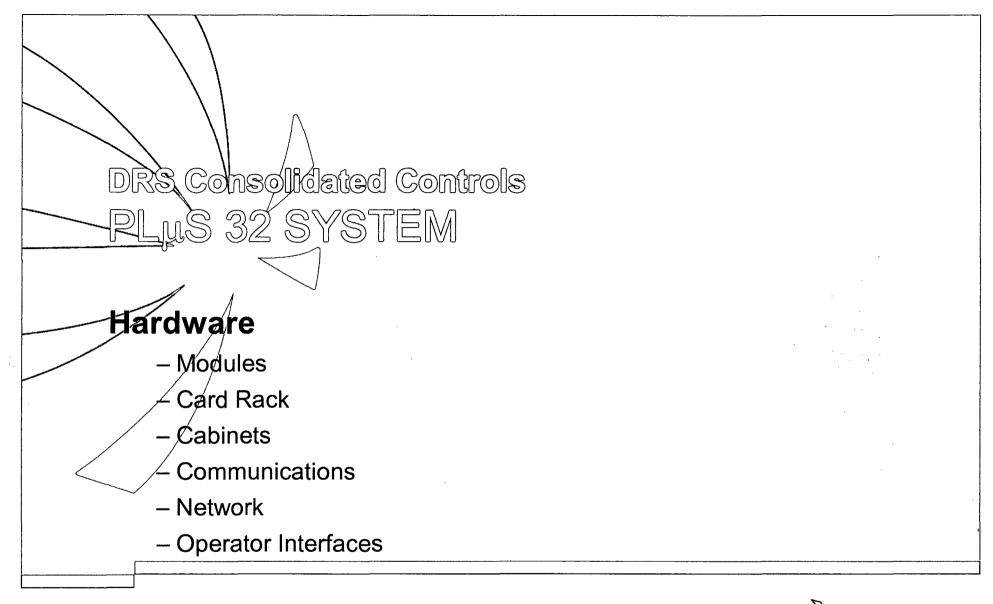

#### PLUS 32 PRODUCT FEATURES

- PLµS 32 <u>Designed</u> as Nuclear Class 1E Distributed Control System

- PLµS 32 Software & Hardware are Modular

- PLµS 32 allows an Architectural Solution that Ranges From Control of a <u>Single</u> Plant Subsystem to an <u>Integrated</u> Distributed Control System

- Major Components Are:

- Control I/O Modules

- Communications Modules

- Operator Interfaces Consisting of:

- Panel Mounted Devices (PMD): Control Switch Modules, Monitoring Light Modules, Manual Auto Station,

- Video Display Units, and

- Operator Interface Station

# PLUS 32 PRODUCT FEATURES

- PLµS 32 Is <u>Supplied</u> with Redundant Deterministic High-Speed Fiber Optic Network

- PLµS 32 Is **Designed** with Hot Swappable Modules

- Control & I/O Modules: Powered by Redundant Power Supply That are Powered from Two Separate Power Sources

- 1996 PLµS 32 Installation Has been <u>Continuously Operational</u> For Over 750,000 Hours <u>Without</u> A Major Incident

#### PLUS 32 PRODUCT FEATURES

- Compliant With (Not all Inclusive):

- 10 CFR Appendix B

- Reg. Guide 1.75 (Physical Class 1E Separation)

- Reg. Guide 1.89 (Qualification)

- IEEE-603, 338, 344 (Seismic), 323 (Mild Environment)

- MIL-STD-461D/462D (EMI/RFI Test Methods)

- EPRI TR102323 Rev.1 (EMI/RFI Acceptance Criterions)

- Software Design Verification & Validation (V&V) to IEEE and U.S. NRC Guidelines for Digital Systems in Safety Related Applications

- ANSI 7-4.3.2-1993

- IEEE-829, 1012, 1028, etc. &

- U.S. NRC Reg. Guide 1.152, 168, 169, etc

- Manufactured Under Applicable Provisions

- 10CFR50 Appendix B, NQA-1, and NQA-2a-1990 Part 2.7 Nuclear Quality Assurance Requirements

RETURN

- Compliance with 10CFR50 Appendix B/ NQA-1 including supplements (1983)

- Internalized via Nuclear Quality Assurance Manual and Administrative Procedures (AP), Instructions, Forms, & Records

- Compliance with ASME NQA-2a, Part 2.7 Software

- BTP HICB-14, IEEE Std. 7-4.3.2, Reg. Guides 1.152 & 1.168

- Internalized via Administrative Procedure AP-3.2

- Compliance with 10CFR Part 21

- Internalized via Administrative Procedure AP-15.1

- Dedication of Commercial Grade Items -

- EPRI TR-106439, EPRI NP-5652; EPRI NP-6406; NRC Generic Letters 89-02 & 91-05

- Internalized via Administrative Procedures AP-7.3

Quality Assurance Responsibilities

- Quality Planning (AP-2.1)

- Qualification and Certification of Personnel (AP-2.3)

- Design & Document Review (AP-3.1 & AP-5.1)

- Software V & V Issue Phase Summary reports (AP-3.2)

- Procurement and Supplier Control (AP-4.1, AP-7.1)

- Dedication Package Support (AP-7.3)

- Manufacturing Process Control (AP-9.1)

- Product Compliance (AP-10.1 & AP-11.1)

- Evaluation of Non Compliances (AP-15.1 & AP-16.1)

- Control of Quality Records (AP-17.1)

- Audit Internal/Supplier (AP-18.1)

- Developed to provide a consistent and methodical process for performing inspections of assemblies.

- Identifies specific inspection activities including inspection methods and sample sizes

- Identifies necessary internal and customer hold points

- Quality Procurement Requirements

- Developed for flow down of quality requirements to suppliers

- Right of Access

- Quality Systems

- Technical Requirements

- MRB Authority

- Hold Points

- Supplier Documentation Requirements

Certification of Personnel

- TEEMNOLOOIES

- Qualification of Inspection and Test Personnel in accordance with NQA-1 1983 and Appendix 2A-1

- Inspectors

- Test Technicians

- Test Engineers

- Software Test

- Qualification Test

- Integrated System Testing

- Qualification of Auditors and Lead Auditors in accordance with NQA-1 1983 and Appendix 2A-3

### Design Control - Hardware Quality Assurance

- Design Review

- Participate in meetings; Follow-up & close-out of Open Items

- Document Review Sign-off Release

- Work Product Review Forms (WPRF)

- Verification/Prototype Testing Module Level

- Witness; Review & Approve Results/Reports

- Class 1E Qualification IEEE 323, IEEE 344, MIL-Std 461 & EPRI TR102323

- Audit Laboratories performing Qualification Tests

- Witness; Review & Approve Results/Reports

- Integrated System Testing Witness; Review/Approve Results

Design Control Software Quality Assurance

- Review Contract documents for requirements

- Generate Software QA Plan (Eng.) IEEE 730

- Generate V&V Plan (NQA) IEEE 1012

- Perform V&V activities

- Attend Peer design review meetings

- Review/Approve meeting minutes

- Review/Approve design documents

- Monitor ACE Analysis process (IEEE 7-4.3.2, Annex F)

- Verify completion and documentation of Software Code Inspection

- Witness Implementation & Installation Phase testing

- Perform assessments and audits of software design activities and testing activities (IEEE 1028)

- Issue Phase Summary reports certifying completion of all activities

# Procurement and Supplier Control

- Assign Quality Requirements for each Purchase Order

- Maintain Approved Suppliers List

- Perform Supplier Quality Program Audits or Commercial Grade Surveys

- Perform Sub-Supplier QA Program Audits or Commercial Grade Surveys

- Product Verification at Supplier Facilities

- Verify Controls of Special Processes

- Witness testing

- Review and Approve Test Results

- Perform Inspections

#### Dedication Packages

DRS

- Review of Technical Evaluations

- Host Component Data

- Item Data

- Item Procurement Evaluation

- Justification and Analysis

- Item Dedication Plan

- Inspection and Test of Critical Characteristics per Dedication Plan

- QA witness of test Activities

- QA sign review and approval of inspection and test results

- Review and Approve Process Instructions

- Assembly Steps

- Required Tooling and Aids

- Internal and Customer Witness and Hold Points

- Required Documentation e.g. aids, test plans IPPs

- Review and Approve Aids used for Manufacturing Processes

#### Product Compliance

- Receiving Inspection

- Review Shipping Release on Source Inspected Items

- Perform Product Inspection (as required)

- In Process and Final Inspections

- Design Drawings

- Inspection Point Plans

- Process Instructions

- Verification of Software Loading

- Correct Device used

- Checksum is verified

- Testing

- Review and Approve Test Results

- Production Level Testing

- FID Logic Testing

- Factory Acceptance Testing

- Qualification Testing

- Packaging Inspections

- Reviewed and Approved Packaging Procedures

- ANSI N45.2.2

#### Evaluation of Non Compliances

- Product Issues Reported on Non Conforming Material Reports (NCMs)

- MRB Review (Engineering and Quality Assurance)

- Assign Disposition

- Review Part 21 Applicability

- Issue Corrective Actions as Necessary

- Seek customer approval for Use-As-Is and Repair Dispositions

- Corrective Actions

- Containment Action

- Review issue for impact to product including Part 21

- Root Cause Identification

- Corrective/Preventative Actions taken

- Follow Up

- Identified

- Classified as Life Time or Non-Permanent

- Retention Periods identified

- Duplicate Storage Locations Maintained

- Accessibility to Records Identified

# Internal Audits

- Scheduled Annually

- All aspects of the Quality Program Reviewed

- Audit Plans and Check Lists Used

- Audits performed by Lead Auditors

- Results are Documented

#### External Audits of Quality Assurance Program

- October 2009 EDG Provider NQA Audit

- April 2009 General Electric Nuclear Engineering (GENE) performs annual audit of Nuclear Quality Program for the Lungmen 1&2 project

- April 2009 Westinghouse initial assessment of DRS's Nuclear Quality Program

- March 2008 General Electric Nuclear Engineering (GENE) performs annual audit of Nuclear Quality Program for the Lungmen 1&2 project

- January 2008 Seven-member NUPIC team led by Progress Energy

RETURN

- PLµS 32 developed and designed to IEEE and U.S.

NRC Guidelines for Digital Systems in Safety Related Applications

- IEEE 7-4.3.2, 1012, 1028, etc.

- U.S. NRC Reg. Guide 1.152, etc.

DESIGN PROCESS

.

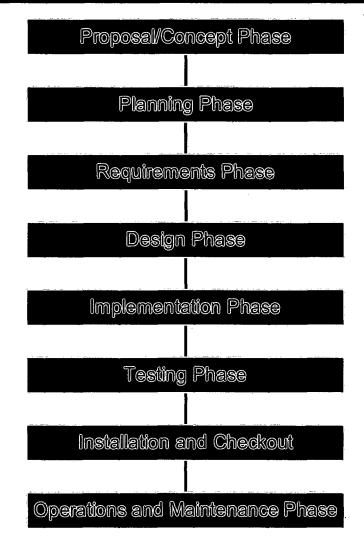

#### **PROPOSAL/CONCEPT PHASE**

- Inputs

- Customer Request for Quote

- Sales and Marketing Information

- Industry Guidelines and Standards

- Internal Processes and Procedures

- Clarifications and Exceptions

- Outputs

- Contract

- Rough Budget

- Rough Schedule

#### PLANNING PHASE

- Inputs

- Contract

- Industry Guidelines and Standards

- Internal Processes and Procedures

- Outputs

- Design Input Requirements Definition

- Project Plan

- Configuration Management Plan

- Software Development Plan

- Software V&V Plan

- System Design Basis Specification

- Baseline Schedule and Budget

#### **REQUIREMENTS PHASE**

| Proposal/Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ncept Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 峰, 전 전 전 전<br>- 1977년 - 6 전 13 55 - 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Planning Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Requireme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ants Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 19. 19. 11. – e deler idea<br>19. 19. 11. – e deler idea<br>19. 19. 1. – deler idea<br>19. 19. 11. 11. 11. 11. 11. 11. 11. 11. | in al falls is all all all all all all all all all al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Implementation Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ister and second s |  |  |  |  |

| Testing Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Installation a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nd Checkout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Operations and Maintenance Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

- Inputs

- Plans from Previous Phase

- System Design Basis Specification

- Software Development Plan

- Outputs

- System Test Plan

- Specific Design Basis Specification(s)

- Software Requirements Document(s)

- Requirements Traceability Matrix

- Abnormal Conditions and Events Analysis

- Software V&V Report(s)

#### DESIGN PHASE

- Inputs

- Plans from Previous Phases

- Specific Design Basis Specification(s)

- Software Requirements Document(s)

- System Test Plan

- Outputs

- Schematic(s) and Drawing(s)

- Software Design Document(s)

- Software Test Plan

- Programming Style Guide

- Requirements Traceability Matrix

- Abnormal Conditions and Events Analysis

- FMEA/Component Stress Analysis

- Software V&V Report(s)

#### **IMPLEMENTATION PHASE**

- Inputs

- Plans from Previous Phases

- Specific Design Basis

Specification(s)

- Software Design Document(s)

- Programming Style Guide

- Outputs

- Factory Acceptance, Qualification, Module, and Software Test Procedures

- Source Code Listing Document(s)

- Requirements Traceability Matrix

- Abnormal Conditions and Events Analysis

- Software V&V Report(s)

#### **TESTING PHASE**

| Proposal/Concept Phase |                  |  |  |  |  |

|------------------------|------------------|--|--|--|--|

|                        |                  |  |  |  |  |

| Planning Phase         |                  |  |  |  |  |

|                        |                  |  |  |  |  |

| Requirements Phase     |                  |  |  |  |  |

|                        |                  |  |  |  |  |

| Design                 | Phase            |  |  |  |  |

|                        |                  |  |  |  |  |

| Implementa             | ation Phase      |  |  |  |  |

|                        |                  |  |  |  |  |

| Testing Phase          |                  |  |  |  |  |

|                        |                  |  |  |  |  |

| Installation a         | nd Checkout      |  |  |  |  |

|                        |                  |  |  |  |  |

| Operations and Ma      | aintenance Phase |  |  |  |  |

- Inputs

- Plans from Previous Phases

- Specific Design Basis Specification(s)

- Factory Acceptance Test Procedure

- This is a multi-phase procedure

- Qualification, Module, System, and Software Test Procedures

- Outputs

- Test Reports

- Field Performance Test Plan

- Requirements Traceability Matrix

- Abnormal Conditions and Events Analysis

- Software V&V Report(s)

#### INSTALLATION AND CHECKOUT PHASE

|          | Proposal/Co            | ncept F      | Phase                                                                  |

|----------|------------------------|--------------|------------------------------------------------------------------------|

|          |                        |              |                                                                        |

|          | Plannin                | g Phase      | 9                                                                      |

|          |                        | 9 14<br>2777 |                                                                        |

|          | Requireme              | ents Ph      | ase                                                                    |

| 5.<br>5. |                        |              | 다. 21 - 14<br>제1 - 관리 - 관리<br>제1 - 관리 - 관리<br>제1 - 관리 - 관리<br>(1 - 관리) |

|          | Design                 | Phase        |                                                                        |

|          |                        |              |                                                                        |

|          | Implementa             | ation Ph     | nase                                                                   |

|          |                        |              |                                                                        |

|          | Testing                | Phase        |                                                                        |

| 12       | 8-0-12-0<br>5-12-0 - 5 | 2.352        |                                                                        |

|          | Installation a         | nd Che       | ckout                                                                  |

|          |                        |              |                                                                        |

| Opera    | ations and M           | aintena      | nce Phase                                                              |

- h Inputs

- Plans from Previous Phases

- Factory Acceptance Test Procedure

- This is a multi-phase procedure

- Outputs

- Factory Acceptance Test Report

- Software Trouble Report(s) (if applicable)

- Requirements Traceability Matrix

- Abnormal Conditions and Events Analysis

- Software V&V Report(s)

#### OPERATIONS AND MAINTENANCE PHASE

|                                     | Proposal/Co   | ncept Pha   | ise            |            |

|-------------------------------------|---------------|-------------|----------------|------------|

| ar an<br>Ar an<br>Ar an<br>Ar an Ar |               |             |                |            |

|                                     | Plannin       | g Phase     |                |            |

|                                     |               | 2.12        |                |            |

|                                     | Requireme     | ents Phase  | Э              |            |

|                                     |               |             | - 61. <u>(</u> | i de       |

|                                     | Design        | Phase       |                |            |

|                                     |               |             |                |            |

|                                     | Implementa    | ation Phas  | se             |            |

| 1 1.31                              |               |             |                | 100<br>100 |

|                                     | Testing       | Phase       |                |            |

|                                     |               | 4.33<br>1 1 |                | - 1.1      |

|                                     | nstallation a | nd Check    | out            |            |

|                                     |               |             | 1              |            |

- Inputs

- Plans from Previous Phases

- Outputs

- Software Trouble Report(s) (if applicable)

- Requirements Traceability Matrix

- Abnormal Conditions and Events Analysis

- Software V&V Report(s)

#### GENERIC SYSTEM CONFIGURATION

#### MODULES

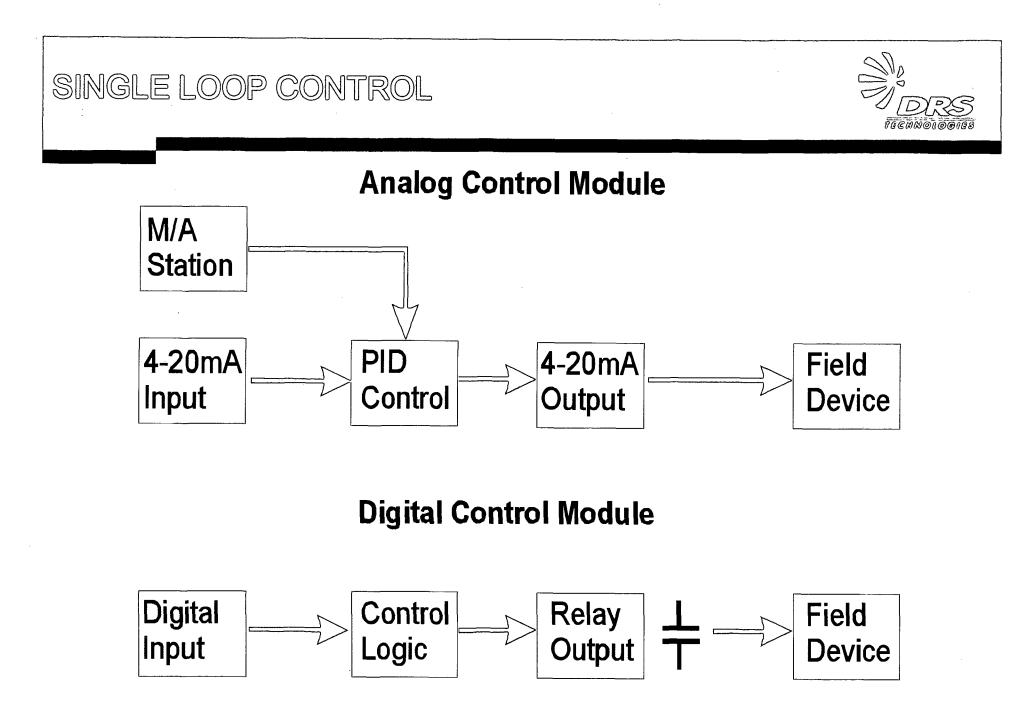

- Control I/O Modules

- Digital Control Module

- Analog Control Module

- Analog Input Module

- Analog Output Module

- Thermocouple Module

- RTD/0-2K Ohm Module

- Digital Output Module

- Communications

- Network Interface Module

- Bridge Transfer Module

- Communications Interface Module

(DCM) (ACM) (AIM) (AOM) (T/CM) (T/CM) (RTD) (DOM)

(NIM) (BTM) (CIM)

#### MODULES

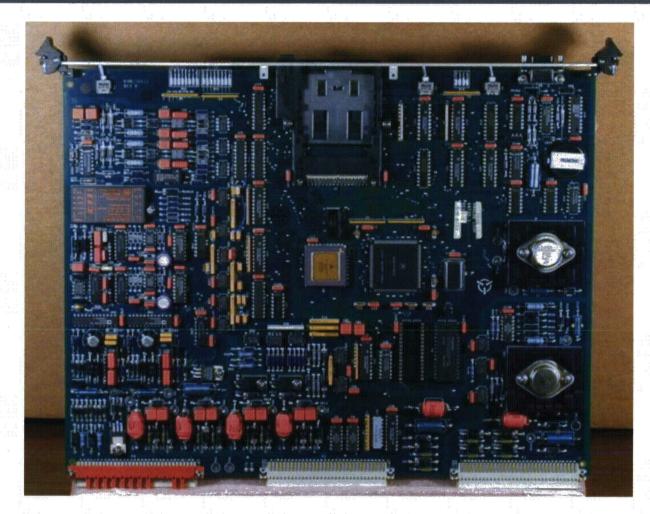

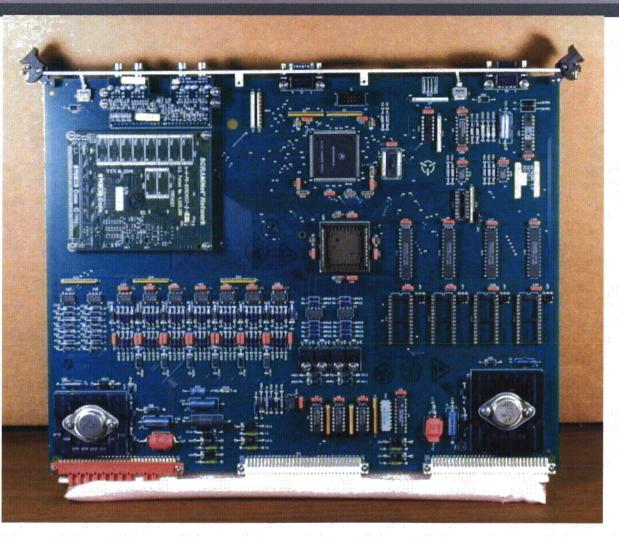

#### • Features on Each Module

- Module Divided Into Three Sections

- Control (Operator Interface)

- Logic (Microprocessor and Communications)

- Field (Field Control Devices)

- Power Auctioneered On Each Module

- Separate Power Supplies for Each Section

- Hot Swappable

- Each Module Has Control Capability With Some Input And/or Output Capability

- 4-20 mA In/Out, TC, RTD (All with Auto-Calibration)

- Digital Modules with On-board Ground Fault Detection on FSR Inputs

#### Features on Each Module

IW

- All Software is Stored on Module in Dedicated EPROM

- Every Module has a Motorola MC68360 Microprocessor

- Designed for a 40 Year Product Life

- DIAGNOSTIC CAPABILITIES

- Continuous On-Line Diagnostics Performed on All Modules

- Levels

- •

- •

.

. .

.

#### MODULES

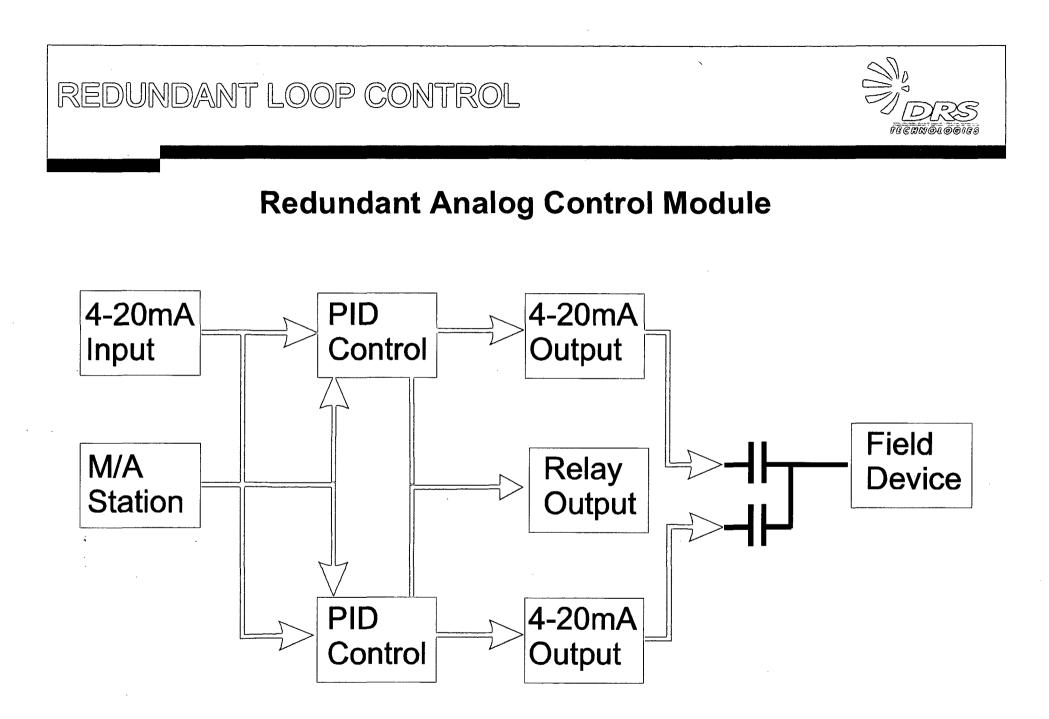

#### ANALOG CONTROL MODULE

#### • FAULT TOLERANT

- Redundant Communication Paths

- Dedicated A/D for Analog Inputs

- Failure of an A/D only impacts a single input

- Dedicated D/A for Analog Outputs

- Failure of a D/A only impacts a single output

- Each Module Determines the Network Used

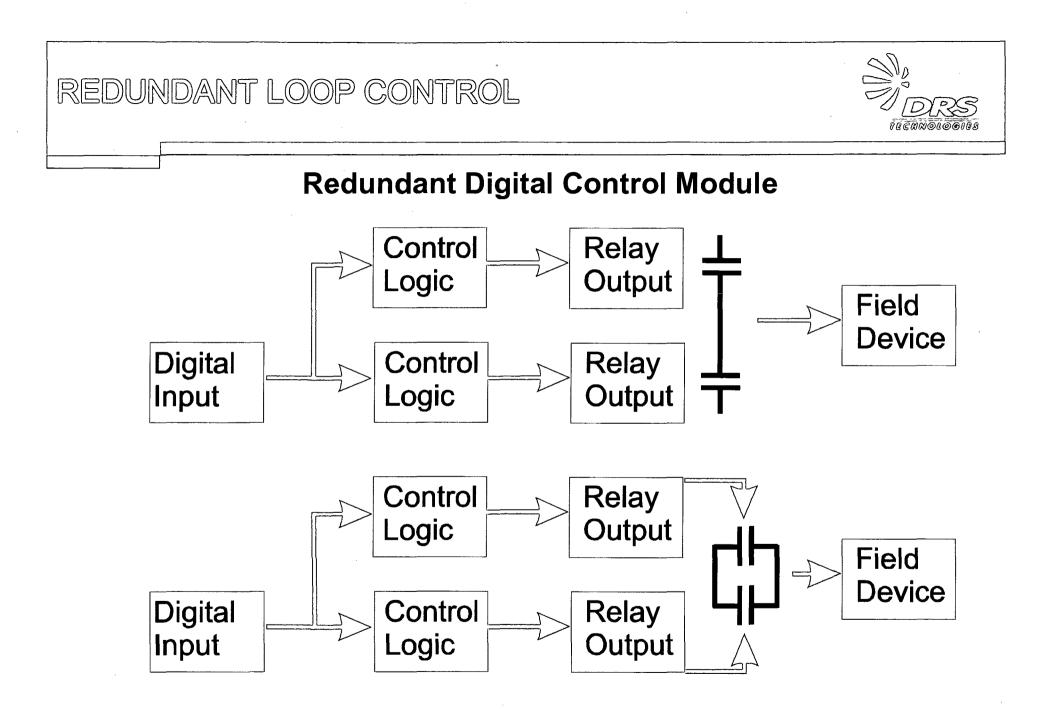

Redundant Module and I/O Capability

#### MODULES

53

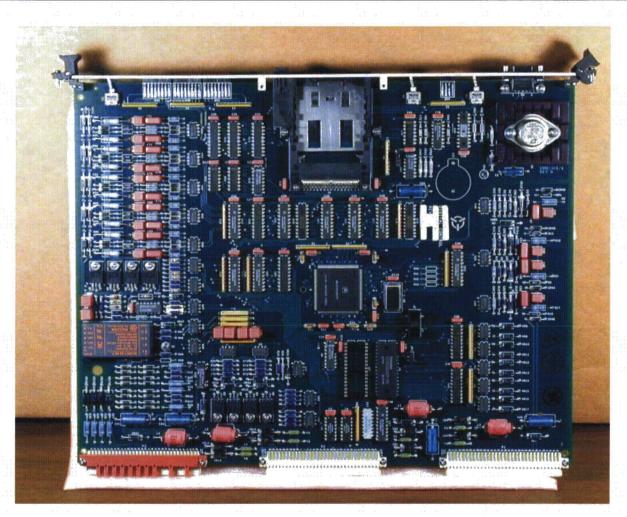

DIGITAL CONTROL MODULE

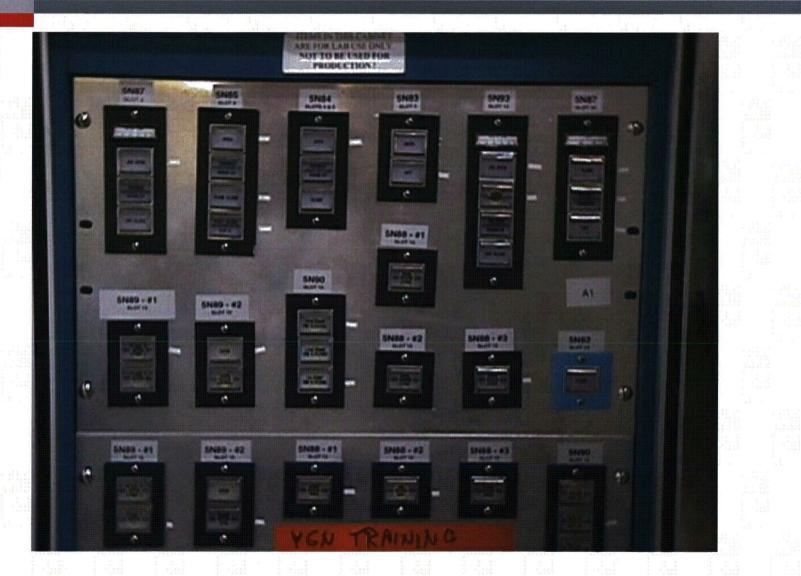

#### CARD RACKS

- Each Rack Holds 16 Modules Plus 2 NIMs

- Redundant DC Power Feeds Per Section

- Designed as Modular Building Blocks

- Any Module Function in Any Slot

- Redundant Backplane Communications

- RS 485 Serial Communication

- 1.5 Mbit/second HDLC Full Duplex Communication

- Identification

- Slot Number

- Rack Number

- Rack to Module Keying

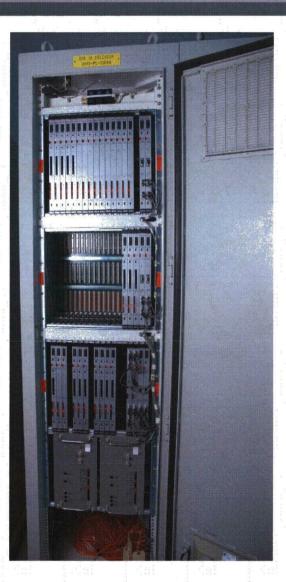

#### CABINETS

- Two Basic Cabinet Types

- Logic Cabinets

- 3 Logic Racks for 48 Modules

- 2 Network Modules per Cabinet

- Power Supply Rack

- Redundant Supplies

- Independent Power Sources

- EMI Filters for Each Power Feed

- Cooling Fans and Controls

- Termination Cabinet

- Separate Cabinet for EMI Control

- Termination Assemblies for Field Wiring and Relay Mounting

- Analog and Digital Designs

- Modular Design

- Plug Connector Interface Cables Between Termination Assemblies and Racks

- Relays and Fusing all on Termination Assembly

#### COMMUNICATION

- Network Interface Module (NIM)

- Communication Link From Cabinet To Cabinet

- Communication Link Network To Module

- Communication Link Module To Module

- Communication Interface Module (CIM)

- Low Data Volume Transfer Network to Network

- Gateway Interface

- Device Net

- Ethernet

- MODBUS

- Serial (RS232/RS422/RS485)

- ATM

- Profibus

- 3 Separate and Independent Communication Paths

- Bridge Transfer Module (BTM)

- High Speed High Data Volume Transfer From Network to Network

#### COMMUNICATION

- One Module for each Network

- Two Modules for Each Cabinet

- Cabinet Identification/Node Number

- Hardware Based

- 128 Maximum Nodes on Network

- Communication

- Serial RS485 Cabinet Internal (NIM/CIM)

- Fiber Optic External

- Software Features

- Cabinet Start-up Node Verification

- Heart Beat Generation and Validation

- Network Data Storage and Distribution

- Cabinet Cooling and High Temperature Alarm (NIM)

- Cabinet Alarm/Status Reporting (NIM)

58

NETWORK INTERFACE MODULE

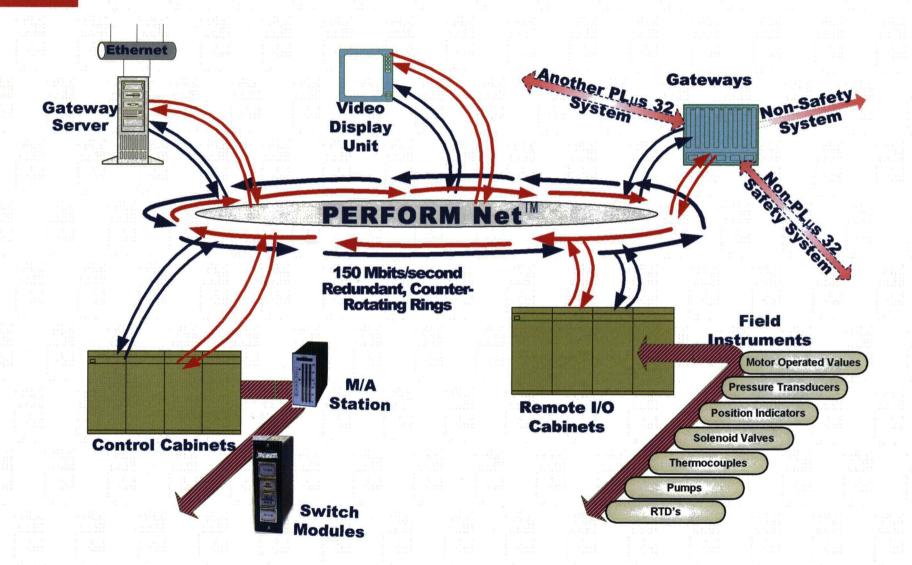

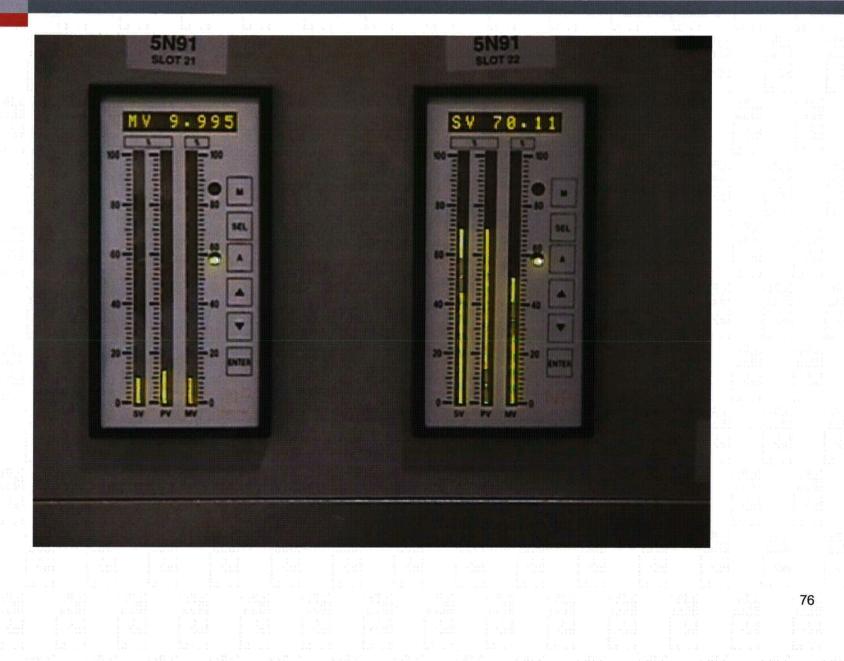

- PERFORM Net

- Performance Enhanced Redundant Fiber Optic Replicated Memory Network

- FEATURES

- Fiber Optic Cabling for Noise Immunity and Electrical Isolation

- Hardware Based, No Software

- 150 Mbits/second Data Transmission

- Redundant Counter Rotating Ring Topology

- Both Networks Active at All Times (No Failover Delay)

- All Data Transmitted All The Time

- FEATURES

- Deterministic Time Response

- 50 Milliseconds

- Input Control Output on a single module.

- 100 Milliseconds

- Input on one module, Control Output on a second module anywhere in the system.

- 150 Milliseconds

- Input on one module, Control on a second module, Output on a third module. Module locations anywhere in the system.

- Flexible System Configurations

- Remote or Local I/O

- Remote or Local Control

How Does It Work?

- Concept

- Concept

- - - •

- Independence

- Per IEEE 7-4.3.2 1993 Appendix G

- NIM Provides Data Control For All Data Passed to the Modules

- Only Data Requested by the FID is Passed From the NIM to the Module

- Separate Communications Drivers And Receivers on the Module and NIM

### NETWORK reciniotocies

RS

- Memory

- -•

- \_

- - - .

· · ·

.

TECHNOLOGIES

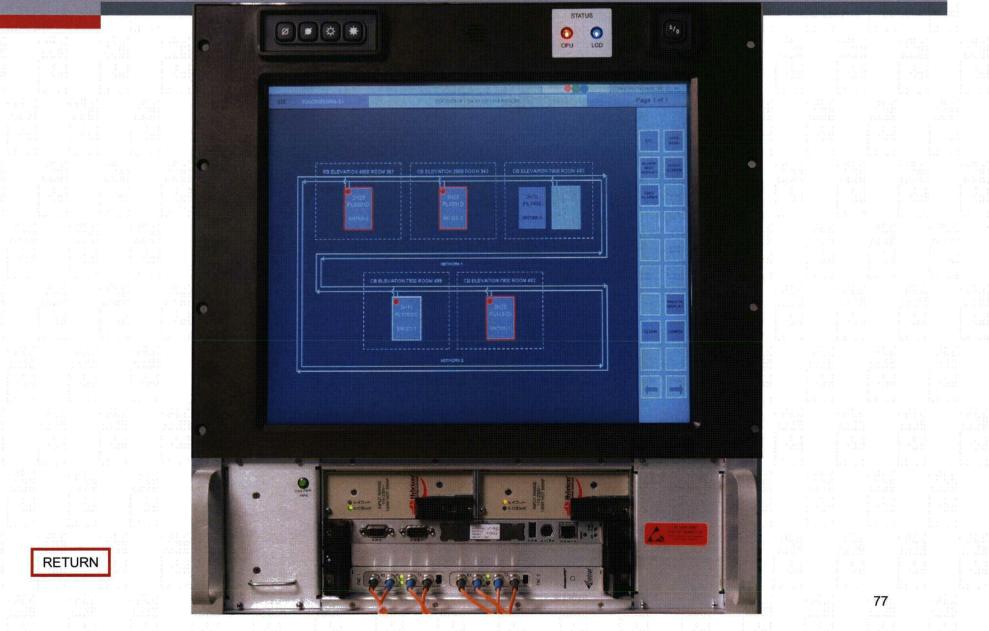

- Hardwired or Soft Control

- Control Board Mounted Switches and Indicator Lights

- M/A Stations for PID Control Loops

- Operator Interface Subsystem (OIS)

- Non-safety Class

- Monitoring and Diagnostics Only

- Windows Based Operating System

- Video Display System (VDU)

- Safety Class

- Control, Monitoring and Diagnostics

- Once Through Operating System

75

DEVELOPMENT PHILOSOPHY

- Keep It Simple Stupid (KISS) Philosophy

- Minimal interrupts

- Interrupts used only for communications

- No recursion, No multi-tasking, No self-modifying code

- No commercial software in the safety operating equipment

- VDU has a small commercial software package that DRS has qualified

- Independence of software test group

- Involvement from cradle to grave

- Abnormal Conditions & Events (ACE) analysis

- Development processes in accordance with IEEE standards and NRC Reg. Guides

- Software development plan / SQAP IEEE 730.1

- Software V&V plan written and enforced by independent NQA group - IEEE 1012, 1028, RG 1.168

- Configuration Management IEEE 828, RG 1.169

- NIM Network Interface Module

- CIM Communications Interface Module

- Control & I/O Modules

- FIDC Functional Interconnect Diagram Compiler

- VDU Video Display Unit

#### SOFTWARE MODULES NIM & CIM Components

- Two per cabinet for redundancy

- Performance of Cabinet Diagnostics

- Power Supply Status, Fan Control, Module Status

NETWORK INTERFACE MODULE (NIM) Operating Cycle

RECANOLOGIAS

- The CIM provides serial buffering between 1E safety systems per IEEE 7-4.3.2

- The CIM software is based on the NIM software

- Operates on a 20 ms operating cycle

#### SOFTWARE MODULES Control & VO Components

ı.

## CONTROL & NO MODULES

- Software Startup Checks

- Module Type

- Rack Location

- Cabinet/Node

- Network Data Validated on each Module before Being Used

·

.

- Interface to hardware devices control and field

90

# CONTROL ALGORITHMS (CA)

- Library of more than 100 control algorithms

FUNCTIONAL INTERCONNECT DIAGRAM COMPILER (FIDC)

- - Processes Information from OrCAD

- Validates the Data from OrCAD

### FUNCTIONAL INTERCONNECT DIAGRAM COMPILER - What does it do?

\_\_\_\_\_

93

FUNCTIONAL INTERCONNECT DIAGRAM COMPILER (FIDC)

- OrCAD to Binary File Manager

- .

- 94

FUNCTIONAL INTERCONNECT DIAGRAM COMPILER (FIDC) DRSS FREEMOLOGIUS

• Binary Processing

95

- Binary Creation

- - .

- .

- - .

96

#### SOFTWARE MODULES VDU Components

.

. .

.

· · · ·

·

-

DRS

VECUNOLOGIES

#### Video Display Unit (VDU)

- The VDU includes the Display Controller and Flat Panel Display Assembly

- Display Controller Intel Pentium III based Single Board Computer and two SCRAMNet cards in a Compact-PCI case

- Flat Panel Display Assembly 18.1" display, touch screen, Analog Interface board, speaker

- The VDU software provides soft controls of the equipment via a flat panel display / touch-screen

- The VDU provides the interface between a human and the PLµS 32 Control System

- The VDU incorporates requirements based on NUREG 0700

## Video Display Unit (VDU) VDU Display Controller Software Components: **Custom Operating System Software** Application Software Custom Operating System Software VDU Control Operating System (VCOS)

#### Video Display Unit (VDU)

- Application Software Components

- Developed in cooperation with the end user

- Screen layout, operation, navigation are developed to meet end user specifications

- Configuration / Setup Screens

- Configuration Entry Screen, Touch Screen Calibration Screen, Clean Screen

- Diagnostic Screens

»

Provide monitoring & control of individual systems within division

RETURN

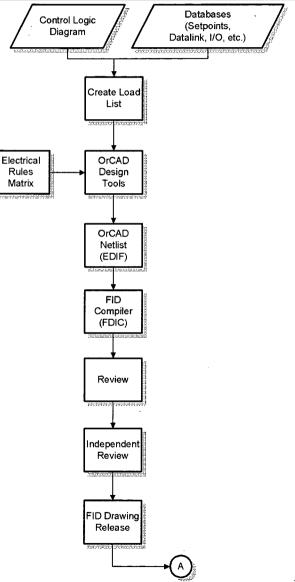

#### FUNCTIONAL INTERCONNECTION DIAGRAMS - FID

- Graphical Representation of Logic

- Hardware and Network Representation

- No Connectivity Database Required

- Easy Modification to Control Application

- Original FID Done by OEM

- Modifications Made by End-User

- Configuration Management Responsibility

1.12

#### Provides Configuration Control

- Documents Each Module

- Control Logic

- Network Connectivity

- Field Terminations

- Cabinet Wiring

- Control Logic

FID

- Standard SAMA Logic Symbols

- Library of Over 100+ Intelligent Symbols

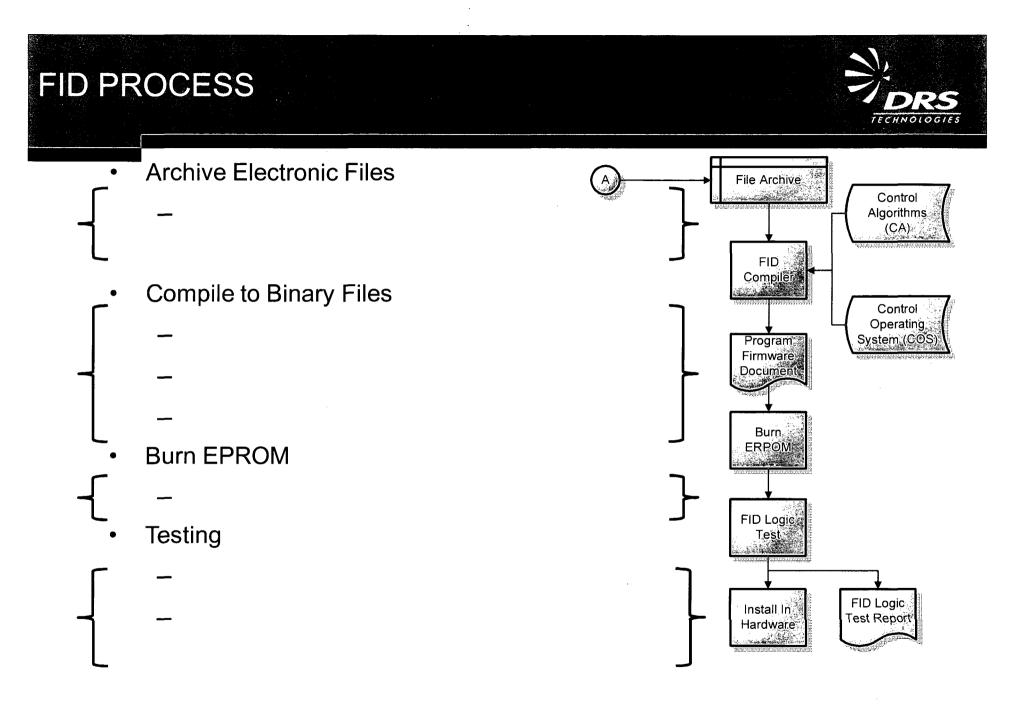

## FID PROCESS

- Design

- Customer I/O Database

- Load Lists

- Control Logic Diagrams (CLDs)

- Typical FIDs

- Unique FIDs

- Peer Review

- Independent Review

- Release FID

#### .

- Programs Hardware Functionality

# CONTROL SECTION

- Operator Input / Output

- \_ \_

- —

- . .

- - .

# ANALOG FIELD SECTION

# NETWORK SECTION

- Variables With Initial Values (VWIVs)

- \_ •

- 115

- U?--

## DESIGN TOOLS

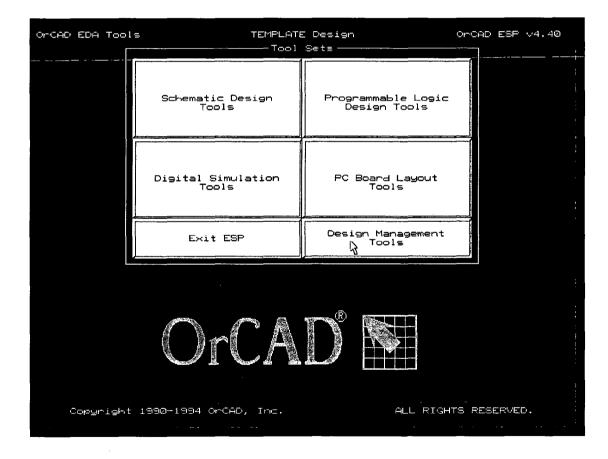

- OrCAD

- Schematic Capture Program

- FID Compiler

- Netlist to Binary Converter

- EPROM Programmer

- Program Module EPROMs or Memory Cards

| OrCAD | <br> | DRSS<br>TECHNOLOGIES |

|-------|------|----------------------|

|       |      |                      |

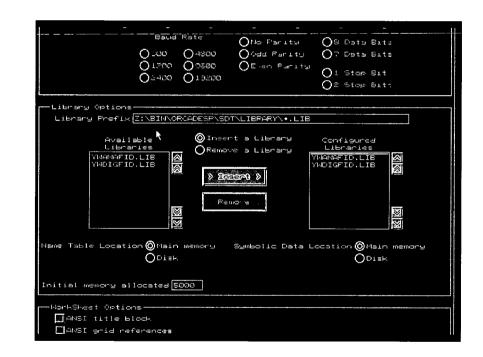

• OrCAD, Schematic Capture Program

ð.

\$

- OrCAD, Schematic Capture Program

- Design Manager

- FID Editor

- Electrical Rules Check (ERC)

- Netlist Generator

- Electronic Design Interchange Format (EDIF)

| Schematic Des<br>Editors   | sign Tools-                             | TYPICAL                     | S-Design                       |                              | AD-ESP V4+40                                    |

|----------------------------|-----------------------------------------|-----------------------------|--------------------------------|------------------------------|-------------------------------------------------|

| Draft                      | Annotate                                | Update<br>Field<br>Contents | Check<br>Design<br>Integrity   | Select<br>Field View         | Fo<br>PLD                                       |

| 3                          | Schematic                               |                             |                                | Compile<br>Schematic         | To Disital                                      |

| Edit File                  | Cleanup                                 | Create Netlist              |                                | Decompile<br>Schematic       |                                                 |

| View<br>Reference          | Schematic                               | Cre<br>Hierarchic           |                                | Back<br>Annotate             | To Main                                         |

| 1                          |                                         |                             |                                |                              |                                                 |

| Libra                      | rians                                   |                             | -Reporters -                   |                              |                                                 |

| Edit                       | List                                    | Cross                       | Create                         | Check<br>Electrical          | Compile<br>FID                                  |

|                            |                                         | Cross<br>Reference<br>Parts |                                | Check<br>Electrical<br>Rules | Compile                                         |

| Edit                       | List                                    | Reference<br>Parts          | Create<br>Bill of<br>Materials | Electrical                   | Compile<br>FID<br>M-A Stat                      |

| Edit<br>Library<br>Compile | List<br>Library<br>Decompile<br>Library | Reference<br>Parts          | Create<br>Bill of<br>Materials | Electrical<br>Rules<br>Plot  | Compile<br>FID<br>M-A Stat<br>Setup<br>M-A Stat |

A

#### OrCAD

- Design Manager

- TEMPLATE Design

- Cabinet Folders

- Module Selection

- File Name

- Date & Time

- Description

- Backup Operations

| -0rCAD-EDA Teols                                                              | Tool                        | 5.Design<br>Set:                                                                                                             | 0rCAD ESP v4.40 |

|-------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|

|                                                                               |                             |                                                                                                                              |                 |

| Désign Direct                                                                 |                             | ign : TYPICALS<br>OFile View                                                                                                 |                 |

|                                                                               | File                        | s wildcard <mark>(*.SCH</mark>                                                                                               |                 |

| DESIGN<br>GE_COS<br>MEMORYCA<br>MINIFCS<br>MISS<br>PROJECT<br>GUALCAB<br>TEMP | <u>(याख</u>                 | Design Files<br>K8819_01.SCH<br>K8819_02.SCH<br>K8819_03.SCH<br>K8819_03.SCH<br>K8819_05.SCH<br>K8819_05.SCH<br>K8819_05.SCH |                 |

|                                                                               |                             | KBB13_08.SCH<br>Y08_42.SCH<br>Y08_42A.SCH<br>Root sheet <u>KBB13_04</u> .                                                    | SCH SCH         |

| Total Siz<br>Description                                                      | e : 418052                  | Last Modified : 03-09                                                                                                        | -101 13:14      |

| Create<br>Design                                                              | Backup Coj<br>Deston Deci   | en Complex to                                                                                                                |                 |

| Pelete<br>Lesten                                                              | Restore Vot<br>Depten BSP ( | ate Sverend<br>to Svetem                                                                                                     | Carcel          |

| Capyright 1990-                                                               | 1994 OrCAD, Inc.            | ALL RIG                                                                                                                      | ITS RESERVED.   |

|                                                                               |                             |                                                                                                                              |                 |

- Analog & Digital

- Title

- Hardware

- Network

- Logic

- CDROM Based

- Z: Drive

- Electrical Rules Check (ERC)

## FID SUMMARY

- Design Manager

- FID Editor

- Electrical Rules Check (ERC)

- FID Compiler

- EPROM Programmer

- FID Process

- > 5000 Successful Online Installations

- 5000 More in the Installation Phase

# INDEPENDENCE

- Redundant Portions Are Independent

- Design Of Application Will Influence

- Redundant Communication Of

- Network

- With in Cabinets

- Isolated Signal Paths

- Fiber Optics Are Used Between Cabinets And Channels

- Separate And Isolated Power Supplies For Sections Of Control Module

- Single Failure In Most Cases Will Not Prevent A Division For Performing It Safety Function

# DIVERSITY AND DEFENCE IN DEPTH

- Implemented by Echelons of Defense

- Each Level has Different Hardware Vendor

- Insuring Different HW and SW Design Teams

- High Quality Software and Hardware

- Reduces Failure Probability

- Evaluated on a Plant by Plant Basis

- Each Level is Independent and Isolated

- DRS has Experience Working with Various Hardware Vendor to Implement

- Working Alliance With RTP

### DIESEL GENERATOR SEQUENCER

System Overview

Typical Communication Interface

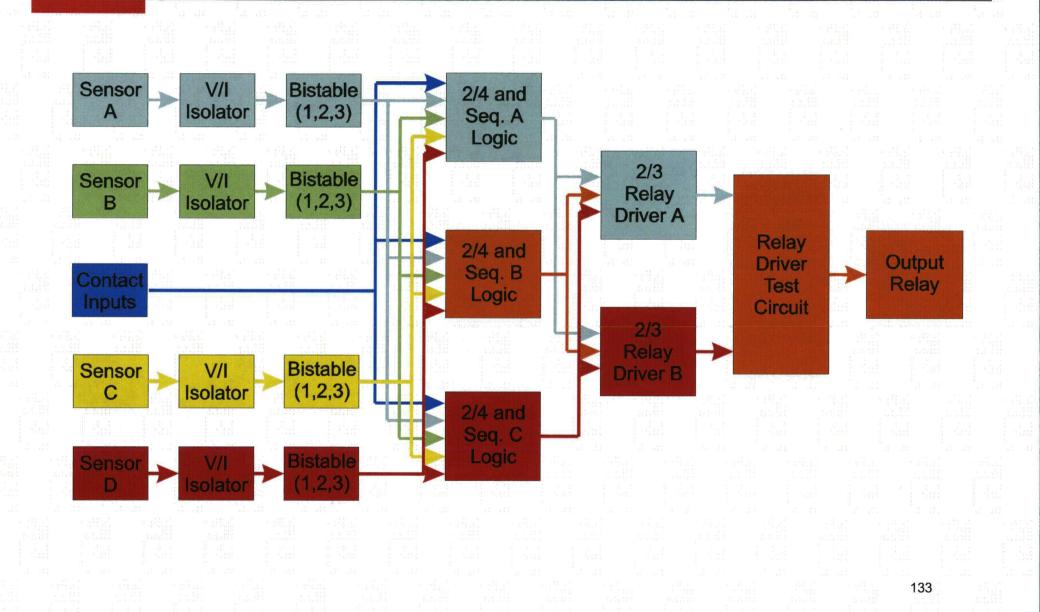

#### ESF Inputs

#### ESF Logic and Outputs

ESF Trip Logic

**ESF** Channels

ESF Inter-Connections

Sensors Bypass

- The Unit Under Test (UUT) consisted of an RMU cabinet, an SSLC/TEST cabinet and a VDU

- At all times the UUT was energized and monitored while subjected to the following:

- ENVIRONMENTAL QUALIFICATION MILD IEEE-323

- SEISMIC QUALIFICATION IEEE-344

- EMI/RFI QUALIFICATION:

- <u>TEST METHODS</u>: MIL-STD-461D

- ACCEPTANCE METHODS: EPRI-TR102323 R1

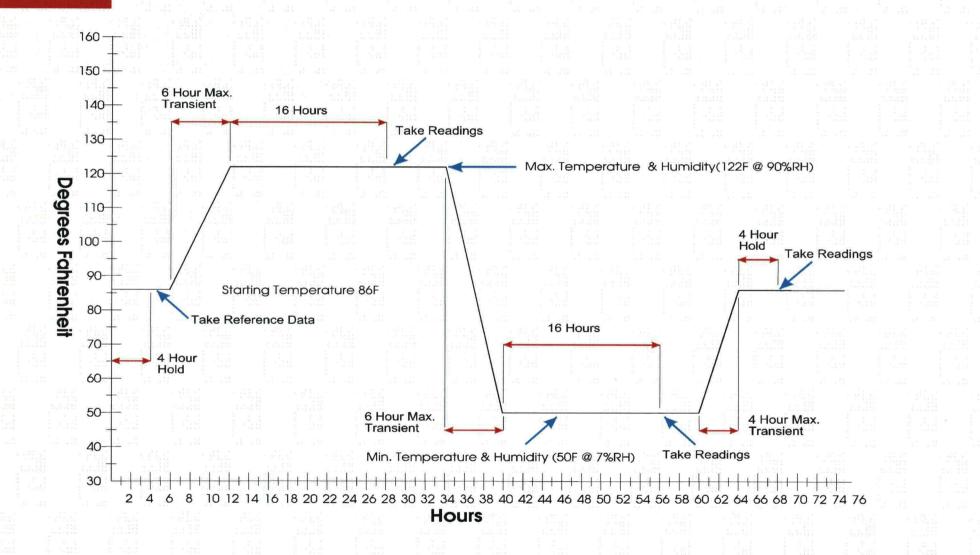

## ENVIRONMENTAL QUALIFICATION

- UUT Installed inside Walk In Chamber

- UUT Powered & Functionally Tested

- Installed T/C in 20 Selected Locations to Monitor Temperatures

- Walk In Chamber's Computer Programmed For the Environmental Profile Soaks

- UUT Monitored During Entire 76 Hour Profile by Automated Data Log Recording, and by DRS & Lab Personnel at the start/end of each Temperature/ Humidity Transition

- Performed Baseline Functional Test

- UUT Subjected to Environmental Soak Profile

- Increase and/or Decrease in the Environmental Profile Was Linear Over a Duration of Time

- Performed Post Functional Test

### ENVIRONMENTAL QUALIFICATION PROFILE

#### SEISMIC QUALIFICATION

- Performed Inspection & Baseline Functional Test

- UUT Mounted on Tri-Axial Shaker Table

- Placed Tri-Axial Accelerometers in Selected Locations

- UUT Energized & Monitored at all times

- Resonant Frequency Search Test

- Visual Inspection (After Each Test)

- Steam Relief Valve (SRV) Dynamic Loads (40)

- Operational Basis Earthquake (OBE) (5)

- Safe Shutdown Earthquake (SSE) (1)

- Chugging Vibration (LOCA) Load (40)

- Final Inspection & Functional Test

- Performed Inspection & Baseline Functional Test

# SEISMIC QUALIFICATION

- VDU Mounted on Tri-Axial Shaker Table

- Placed Tri-Axial Accelerometers in Selected Locations

- UUT Energized & Monitored at all times

- Resonant Frequency Search Test Non Seismic

- Visual Inspection (After Each Test)

- Operational Basis Earthquake (OBE) (5)

- Safe Shutdown Earthquake (SSE) (1)

- Final Inspection & Functional Test

- Test Methods are In accordance with MIL-STD-461D

- Acceptance Methods are in accordance with EPRI TR102323 R1

- As Applicable; Test Levels, EPRI Levels, v. MIL-STD Levels Are Shown in The Same PLOT

- Performed Functional Test After Each of the Following Tests:

- <u>Test Method CE101</u>: Conducted Emissions (Power Leads, 30Hz to 50kHz)

- <u>Test Method CE102</u>: Conducted Emissions (Power Leads, 50kHz to 400 MHz)

- <u>Test Method RE101</u>: 30 Hz to 100 kHz Radiated Emissions, Magnetic Fields

- <u>Test Method RE102</u>: 10kHz to 1GHz, Radiated Emissions, Electric Field

## EMI / RFI QUALIFICATION

- <u>Test Method CS101</u>: 30kHz to 50kHz, Conducted Susceptibility, Power Leads

- <u>Test Method CS114</u>: 50kHz to 400MHz, Conducted Susceptibility, Cables

- <u>Test Method RS101</u>: 30kHz to 100kHz, Radiated Susceptibility Magnetic Field

- <u>Test Method RS103</u>: 10kHz to 1GHz, Radiated Susceptibility, Electric Field

- Test Method IEC 801-2: Electrostatic Discharge

- <u>Test Method IEC 801-4</u>: Electrical Fast Transient/Burst

- <u>Test Method IEC 801-5</u>: Surge Immunity Test

RETURN

Development Cyber Security Wide A<u>rea Access</u>

•

Development Cyber Security Development Share Access

.