**HFC Non-proprietary**

# **HF** Controls Corporation

## HFC-6000 Product Line

HFC-SBC06-DPM06 Boards Module Design-Specification

System Controller

MS901-000-0

**Rev E**

Effective Date

03-27-09

Author/Title

Gregory Rochford

Reviewer/Title

Ivan Chow

Approval/Title \_\_\_\_\_ Terrence Gerardis

Copyright<sup>©</sup> 2009 HF Controls Corporation

| Revision History |          |             |                                           |  |  |

|------------------|----------|-------------|-------------------------------------------|--|--|

| Date             | Revision | Author      | Changes                                   |  |  |

| 10/14/03         | 0        | R. Horn     | Outline                                   |  |  |

| 04/12/04         | 1        | B. Han      | Initial                                   |  |  |

| 04/21/04         | А        | B. Han      | Comments incorporated                     |  |  |

| 10/23/06         | В        | J. Stevens  | KOPEC Comments (Pages 16 & 17)            |  |  |

| 3/9/07           | С        | J Taylor    | SCR 1766                                  |  |  |

| 12/9/08          | D        | I. Chow     | Revised Figures 5, 6, 16 pages 22, 26, 54 |  |  |

| 3/26/09          | E        | G. Rochford | Modified figures with EPROM to PROM       |  |  |

|                  |          |             |                                           |  |  |

# Table of Contents

| 1. INTRODUCTION                                     |    |

|-----------------------------------------------------|----|

| 2. FUNCTIONAL DESCRIPTION                           | 5  |

| 2.1 EXTERNAL COMMUNICATION                          | 6  |

| 2.2 REDUNDANT SYSTEM CONTROLLERS                    | 6  |

| 2.3 EXECUTION OF APPLICATION PROGRAMS               | 9  |

| 3. MODULE ARCHITECTURE                              | 9  |

| 3.1 MEMORY MAPPING STRUCTURE                        |    |

| 3.2 PUBLIC MEMORY DATA                              |    |

| 3.3 REMOTE COMMUNICATION ARCHITECTURE               | 14 |

| 3.3.1 HFC-SBC06 HANDLING OF DDB DATA                |    |

| 3.3.2 HFC-SBC06 HANDLING OF UCP MESSAGES            |    |

| 3.4 SYS PROCESSOR SECTION                           |    |

| 3.4.1 SYS PROCESSOR SOFTWARE ARCHITECTURE           |    |

| 3.5 ICL PROCESSOR SECTION                           |    |

| 3.5.1 ICL SOFTWARE ARCHITECTURE                     |    |

| 3.6 CPC PROCESSOR SECTION                           |    |

| 3.6.1 CPC PROCESSOR SOFTWARE ARCHITECTURE           |    |

| 3.7 HFC-SBC06 AND HFC-DPM06 REDUNDANCY ARCHITECTURE |    |

| 3.8 HFC-SBC06 CPLD DESIGN                           |    |

| 3.9 SEQUENCE OF EVENTS TIMER                        |    |

| 3.10 . HFC-DPM06 BOARD                              |    |

| 4. CONFIGURATION SETUP AND LED DISPLAYS             |    |

| 4.1 HFC-SBC06 ONBOARD SWITCH FUNCTIONS              |    |

| 4.2 HFC-DPM06 ONBOARD SWITCH FUNCTIONS              |    |

| 4.3 HFC-SBC06 ONBOARD JUMPER OPTIONS                |    |

| 4.4 LEDs                                            | 39 |

| 4.4.1 HFC-SBC06 LED FUNCTIONS                       | 39 |

| 4.4.1.1 DS3 AND DS4 LEDs                            |    |

| 4.4.2 HFC-DPM06 LED FUNCTIONS                       |    |

MS901-000-01

2 of 55 Rev E

| 4.5   | INSTALLATION OF SYSTEM SOFTWARE AND APPLICATION PROGRAMS | 42 |

|-------|----------------------------------------------------------|----|

| 4.5.  | 1 System Code Transfer to Flash                          | 42 |

| 4.5.2 | 2 APPLICATION CODE DOWNLOAD                              | 43 |

| 4.5.3 | 3 System Software Updates                                | 44 |

| 4.6   | HARDWARE CONFIGURATION                                   | 44 |

| 5.    | MODULE DESIGN CONSTRAINTS                                | 46 |

| 5.1   | COMMUNICATION INTERFACE SPECIFICATIONS                   | 46 |

| 5.2   | OPERATING SYSTEM SPECIFICATION                           | 46 |

| 5.3   | HARDWARE INTERFACE SPECIFICATIONS                        | 46 |

| 5.1   | Design Safety                                            | 46 |

#### List of Tables

| Table 1. | SYS Processor Configuration Switches                        | 37 |

|----------|-------------------------------------------------------------|----|

| Table 2. | Jumper Options                                              | 38 |

|          | DS3 and DS4 LED Indications for Initialization Failure      |    |

| Table 4. | DS3 and DS4 LED Indications for Individual Tasks            | 41 |

| Table 5. | DS3 and DS4 LED Failure Indications During Normal Operation | 41 |

#### LIST OF FIGURES

| Figure 1. HFC-6000 System Hierarchy                          | 4  |

|--------------------------------------------------------------|----|

| Figure 2. Redundant HFC-SBC06 Boards with DPM06 Board        | 7  |

| Figure 3. ICL Network for Redundant Controller Configuration | 8  |

| Figure 4. Non-Redundant HFC-SBC06 Board and DPM06 Board      | 9  |

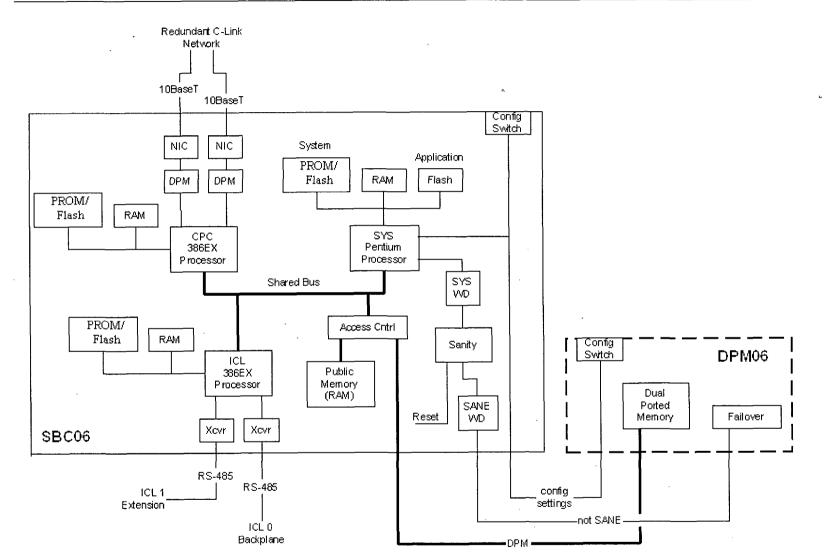

| Figure 5. HFC-SBC06 / DPM06 Module Architectures             | 11 |

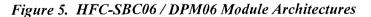

| Figure 6. Microprocessor Address Space                       | 12 |

| Figure 7. Public Memory Data Stores                          | 13 |

| Figure 8. DDB Broadcast Data Paths                           | 15 |

| Figure 9. UCP Point-to-Point Message Path                    | 15 |

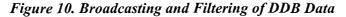

| Figure 10. Broadcasting and Filtering of DDB Data            | 17 |

| Figure 11. UCP Message Processing                            | 18 |

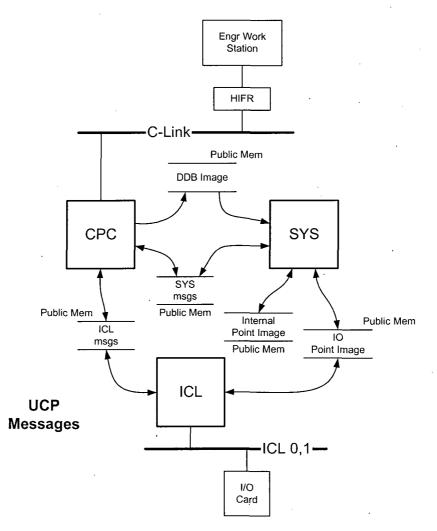

| Figure 12. System Processor Architecture                     | 19 |

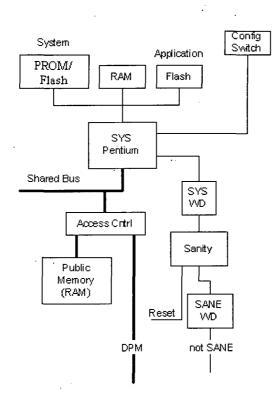

| Figure 13. System Software Architecture                      | 23 |

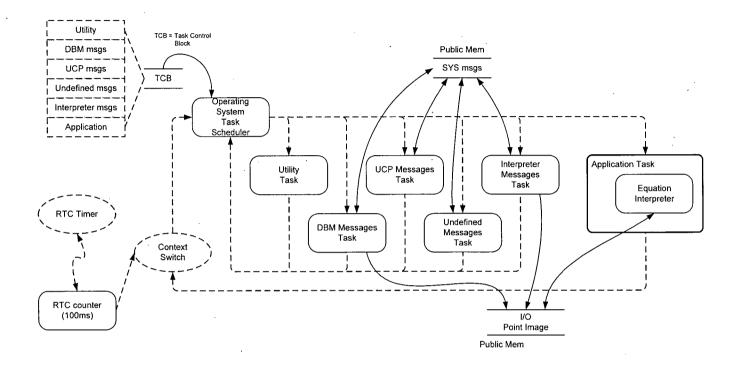

| Figure 14. ICL Processor Architecture                        | 25 |

| Figure 15. ICL Software Architecture                         |    |

| Figure 16. CPC Processor Architecture                        |    |

| Figure 17. CPC Software Architecture                         | 31 |

| Figure 18. HFC-SBC06 Redundancy and Failover                 | 33 |

#### 1. Introduction

The HFC-6000 distributed control system provides plant monitoring and control capabilities, with monitoring and control responsibilities spread over multiple remote control units. The HFC-SBC06 System Controller is the primary board used for implementing plant control functions. This HFC-SBC06-DPM06 Module Design Specification describes the HFC-SBC06 System Controller board and HFC-DPM06 Dual Ported Memory board.

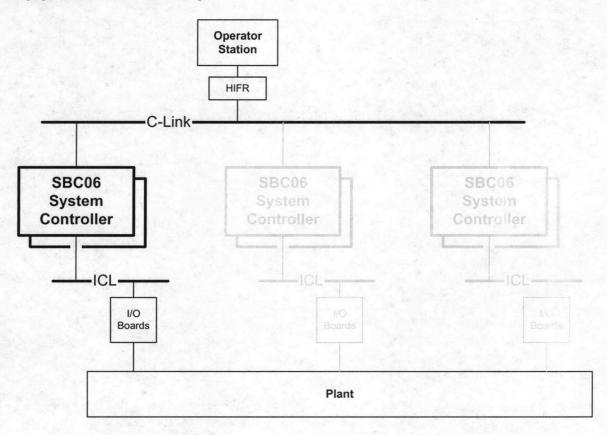

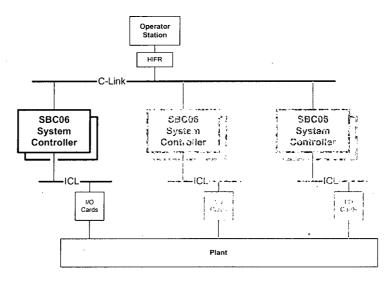

As shown in Figure 1, the HFC-SBC06 System Controller board is positioned in the HFC-6000 system hierarchy between the Operator Station(s), which provides the direct Human Machine Interface to the plant operators, and the I/O boards which provide the signal-level interface to the equipment and devices in the plant.

Figure 1. HFC-6000 System Hierarchy

Descriptions of the functional requirements of the HFC-SBC06 System Controller board and HFC-DPM06 board, from an external perspective, are provided in the HFC-6000 Product Line Requirements Specification, RS901-000-01. The design of the HFC-SBC06 and HFC-DPM06

also complies with the detailed requirements spelled out in 700901-04, 700901-05, and RS901-000-37.

The purpose of this document is to describe the operation and functions of the HFC-SBC06 and HFC-DPM06 boards. The discussion of the operation and function of the HFC-SBC06 and HFC-DPM06 will be presented using architectural, design, and implementation information.

Subsequent sections of this document provide architectural and design descriptions of the HFC-SBC06 board. Lower level descriptions of the HFC-SBC06 and HFC-DPM06 are contained in the HFC-SBC06-DPM06 System Controller Module Detailed Design Specification, DS901-000-01. The major functions performed by the HFC-SBC06 and HFC-DPM06 are listed in the next section which contains brief descriptions of the functions and how the HFC-SBC06 or HFC-DPM06 performs the functions.

### 2. Functional Description

The functions described in this section are the major functions performed by the HFC-SBC06 System Controller. The functional descriptions are presented so as to provide a context for understanding the operation of the HFC-SBC06 and a description of how the functions performed by the HFC-SBC06 System Controller work within the overall architecture of the HFC-6000 distributed control system.

The major functions performed by the HFC-SBC06 System Controller are:

- Communication with other system controllers and workstation PCs connected to the same redundant C-Link (Communication Link), an HFC proprietary network; Broadcasting plant status information;

- Communication with modules connected to the same ICL (Intercommunication Link), another HFC proprietary network; Collecting plant status information and sending plant operation commands;

- Redundant controller operation, System Controller failure detection, failover of the control function to the Secondary System Controller on failure of the Primary System Controller, and maintenance failover.

- Execution of application control programs for the specific control logic;

The following sections supply descriptions of the HFC-SBC06 functional requirements and identify aspects of the HFC-SBC06 that perform functions satisfying the requirements.

#### 2.1 External Communication

Two communication interfaces connect the HFC-SBC06 to other boards and devices in the HFC-6000 system. Two identical 10BaseT interfaces connect the HFC-SBC06 to the redundant fiber optic Communication Link (C-Link) network, an HFC proprietary Ethernet-based network that the HFC-SBC06 uses to transfer data to and from the Operator Stations. Typical data transfers between the Operator Station and a System Controller are operator commands from an Operating Station to the System Controller and plant operation data to the Operator Station. The HFC-SBC06 also uses the C-Link to broadcast its status to other remotes attached to the C-Link.

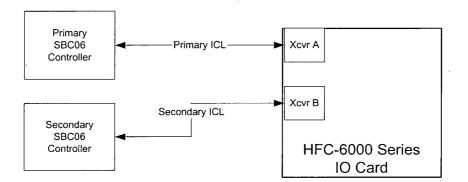

The other HFC-SBC06 communication interface connects the HFC-SBC06 to the Intercommunication Link (ICL), which is an RS-485 serial network connecting the HFC-SBC06 to its I/O boards. Each HFC-SBC06 has two serial channels (ICL0 and ICL1) with each connecting to different I/O boards. Each serial channel can be linked to up to 32 I/O boards. Input values from plant field devices and output values to plant actuators are transferred between the HFC-SBC06 and I/O boards over the ICL serial network. The ICL network implements a master/slave communication protocol. Only the master can initiate communication, and the slave devices only respond to the master's poll. HFC-SBC06 serves as the master for all communication transfers with its configured ICL stations. Each I/O board operates as a slave node on the ICL network. The HFC-SBC06 polls each configured slave device at regular intervals, and the slave devices receive operation commands in the communication messages and respond with plant status information. Although each HFC-SBC06 board has two physical serial channels connected to different I/O boards, these two physical channels are on one logical link under the ICL protocol, either ICL A or ICL B for the I/O boards. Therefore, each ICL can be linked to up to 64 I/O boards.

Refer to DS002-000-01, C-Link Protocol Component Design Specification, and DS002-000-02, ICL Protocol Component Design Specification for details.

#### 2.2 Redundant System Controllers

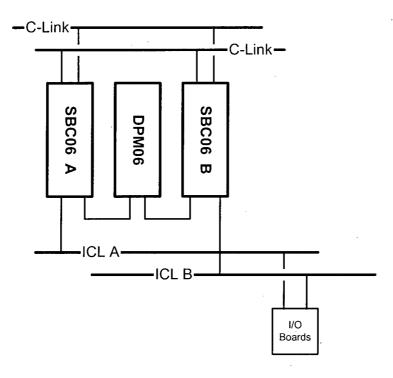

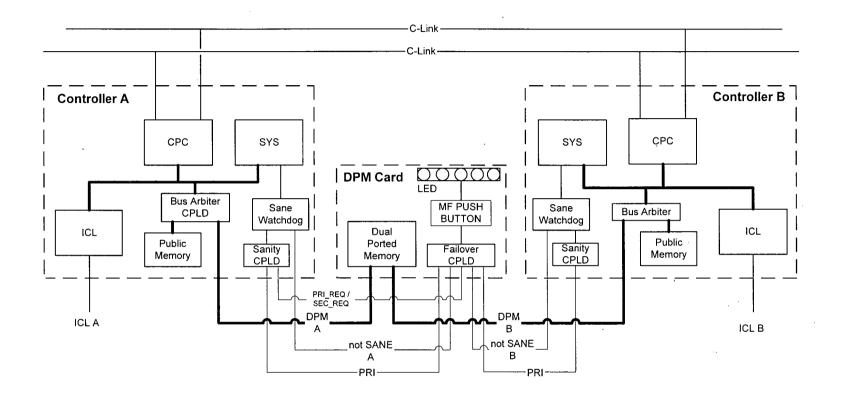

The HFC-SBC06 System Controller board is designed to operate in a redundant controller configuration. As shown in Figure 2, a redundant configuration consists of two System Controller boards (HFC-SBC06 A and HFC-SBC06 B) and a HFC-DPM06 dual ported memory board with the DPM06 board installed in between of the two SBC06 boards. Each HFC-SBC06 board in the redundant pair operates in one of two different modes: one board operates in a Primary controller mode, and the other board operates in a Secondary controller mode. Controller mode operation is determined at controller board start-up, with the first HFC-SBC06 to complete its initialization routine becoming the Primary, and the other HFC-SBC06 board defaults to Secondary controller mode.

Each HFC-SBC06 in a redundant pair is connected to redundant C-Link networks for communication with the Operating Station and one of two ICL serial networks that provides communication between the HFC-SBC06 and to each of its I/O boards. Each I/O board connects

MS901-000-01

6 of 55

Rev E

with two system controllers via its dual serial ports as shown in Figure 2. The mode (Primary or Secondary) in which the HFC-SBC06 is operating determines how the HFC-SBC06 will use C-Link (Ethernet) and ICL (serial) networks.

Figure 2. Redundant HFC-SBC06 Boards with DPM06 Board

During redundant operation, the Primary controller periodically copies application and system status data to dual ported memory (DPM) contained on the DPM06 board. The Secondary controller, on the other hand, periodically validates the status data in the DPM and updates its own record of status data if the data is valid. This DPM Transferring Mechanism keeps the secondary controller updated with a current copy of the primary running status and ensures a smooth transition from one controller to the other in the case of failover. During a failover event when control responsibility switches from the Primary to the Secondary, the Secondary uses the most recent application and system status data as an initial state for starting its control of the system. Starting with an initial state that is one second old or less minimizes disturbances to the plant induced by the controller switch over, and prevents potentially hazardous bumping caused by transfer of control. After switch over is complete, the Secondary, which is now the controlling the plant, switches to operation in the Primary control mode. Additional discussion of the failover mechanism is listed DS001-000-08, Failover Mechanism Component Design Specification.

A Maintenance Failover function is supported to perform regular check on the working status of the secondary controller to make sure it will be able to take over the control when the primary controller fails. A pushbutton on the HFC-DPM06 allows failover to be triggered manually.

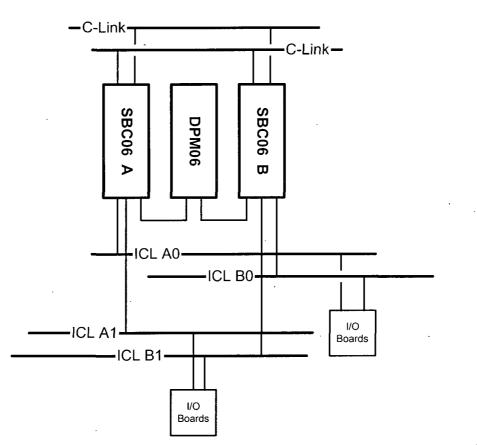

As shown in Figure 3, the ICL network for a redundant controller configuration includes four physical serial channels for the redundant controllers: ICL A includes ICL A0 and ICL A1 for controller A; ICL B includes ICL B0 and ICL B1 for controller B. A single controller can have up to 64 I/O boards under its control.

Figure 3. ICL Network for Redundant Controller Configuration

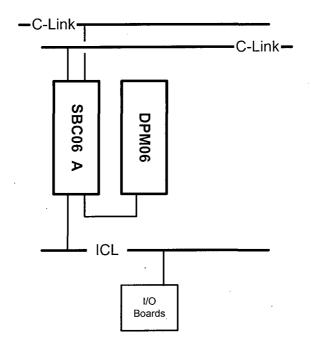

The HFC-SBC06 board may also be configured as a non-redundant System Controller. In a non-redundant of configuration, a single HFC-SBC06 is installed in slot 12 or 14 of a 19-inch HFC-6000 controller rack, and a DPM06 is installed in slot 13. (If the system uses 23-inch racks, the controller may be in slot 16 or 18, and the DPM 06 be installed in slot 17.) Configuration switches located on the front edge of the DPM06 board are used to setup a number of system configuration parameters. The HFC-SBC06 must access a DPM06 to read the configuration settings as part of its initialization process.

Another difference between a redundant and non-redundant configuration is that a non-redundant. HFC-SBC06 configuration only supports a non-redundant ICL network, as shown in Figure 4 instead of the redundant ICL network shown in Figure 3.

### HFC-5BC06-DPM06 Board Module Design Specification

Figure 4. Non-Redundant HFC-SBC06 Board and DPM06 Board

#### 2.3 Execution of Application Programs

The primary function of the HFC-SBC06 System Controller board is to provide control of the plant system actuators based upon the values of system inputs collected from plant field sensors. Control logics, such as arithmetic calculations and logical operations, operate upon field input values to provide control output values that drive plant actuators, operator status displays, and alarm indicators. These control logics are defined in an Application Program, which is installed in the PROM or flash memory in the HFC-SBC06 System Controller. It is transferred to the RAM during power up initialization, and the program is executed during operation of the controller.

Refer to DS001-000-002, Equation Interpreter Component Design Specification, and DS001-000-003, CQ4 Blocks Component Design Specification, for detailed descriptions of control logic algorithms. Refer to UG004-000-01, EWS User's Guide for detailed information about the structure of application program code.

#### 3. Module Architecture

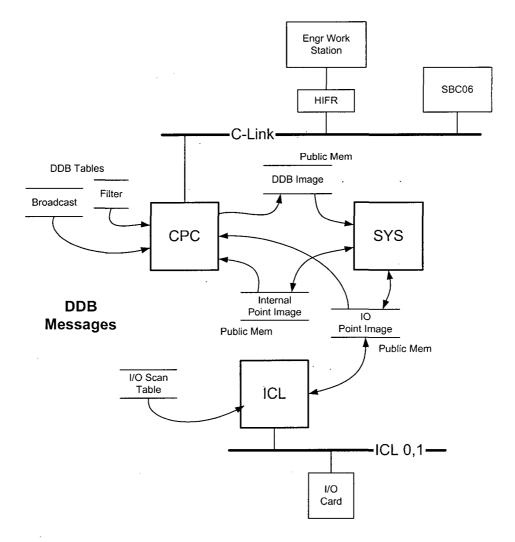

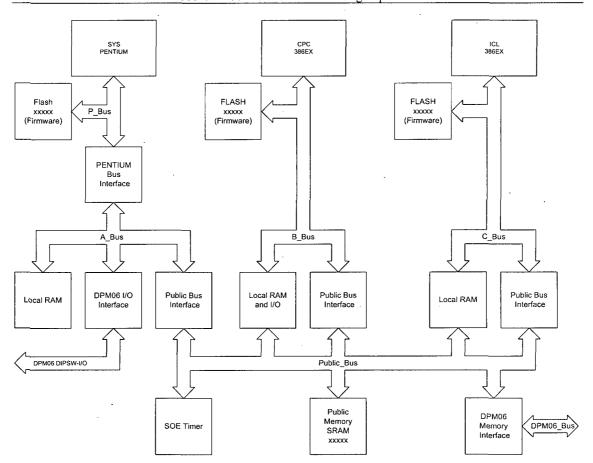

The architecture and design of the HFC-SBC06 board is based upon a partitioning of the module functions between three separate microprocessor sections: the SYS microprocessor section, the ICL microprocessor section, and the CPC microprocessor section. Each microprocessor section is dedicated to a specific set of functional responsibilities, with the SYS processor being the main

processor or system processor for the whole controller and the other two processors being subordinate processors.

The three independent microprocessors uses Public Memory to communicate and coordinate their individual operations. Public Memory is a shared onboard memory (RAM) section that may be accessed by the three microprocessors over a Shared Bus. As shown in Figure 5, the three microprocessors connect to the Public Memory address and data bus (Shared Bus) on the board, with each microprocessor's access to Public Memory controlled by a bus arbitration circuit. Public Memory contains data that is shared by the microprocessors and data that must be transferred between the microprocessors.

In addition to available use of Public Memory, each microprocessor is configured with Private Memory with separate PROM, Flash, and RAM sections. System firmware codes are installed in the PROM or flash memory. Private Memory is accessible only to the microprocessor in that circuit section.

The CPC Section has two RJ45 10BASET ports for the redundant C-Link interface. The ICL Section includes two RS-485 communication links for the ICL.

There is an onboard Sanity circuit for detection of controller failure. The SANE status and PRI (Primary) status signals from the Sanity circuit are routed to the Failover circuit on the HFC-DPM06 board. The Failover circuit supports failover on failure of Primary controller and maintenance failover.

There is a dual-ported memory on the HFC-DPM06 board which is accessible to both the primary and secondary controllers. The three processors connect to the DPM address and data bus, with each processor's access to the DPM controlled by a bus arbitration circuit. Software arrangements coordinate Read and Write to the DPM by the primary and secondary controllers to avoid conflicts or corrupted data.

The System Controller provides Sequence of Events (SOE) master clock with 1 ms resolution over 24 consecutive hours of operation.

Both the HFC-SBC06 and HFC-DPM06 board have DIP switches for controller configuration. These switch settings are accessible to the SYS processor on board.

HFC Non-proprietary

#### 3.1 Memory Mapping Structure

The individual memory address spaces for the three microprocessors on the HFC-SBC06 board have the same basic structure, with each address space including both Public and Private Memory areas. As shown in Figure 6, the top range of the address space (PROM / Flash) contains executable code. The microprocessor data area (RAM) is mapped to the bottom range of the address space. Public Memory is mapped to the center range of the microprocessor address space.

#### Figure 6. Microprocessor Address Space

The DPM memory area located in Public Memory address space shown in Figure 6 is dual ported memory residing on the DPM06 board installed in the slot next to the HFC-SBC06 board. DPM memory is used by two HFC-SBC06 boards operating as a redundant pair for transferring data between Primary and Secondary.

The Private Memory area shown in Figure 6 labeled **Microprocessor Specific** has different uses within the three processor sections. In the SYS processor section, this area of Private Memory contains the Application Program instructions. In the CPC processor section, this area is mapped to a dual ported memory part that is used to interface the CPC microprocessor to the Ethernet controllers managing low-level communication functions on the C-Link network. In the ICL processor section, this area of Private Memory is not used and contains no RAM, PROM, or Flash memory.

#### 3.2 Public Memory Data

The design of the HFC-SBC06 board uses a Public Memory Data area to allow the three microprocessors to share and transfer data during operation. Public Memory contains a number of data stores used by the microprocessors with the main data stores holding I/O and UCP message data.

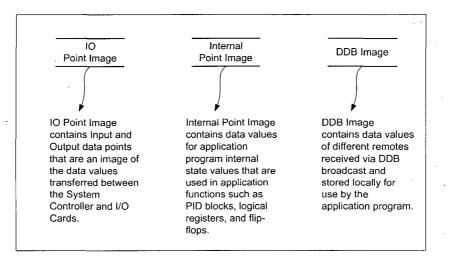

The I/O data stores hold data that is accessed and shared by all three microprocessors. As an example of shared data, Public Memory contains three main shared data areas: IO Point Image, Internal Point Image, and DDB Image. These data image areas are used by all three processors on the System Controller board. The data stores shown in Figure 7 are three of the main data items in Public Memory, and these data stores will be encountered a number times during discussion concerning aspects of the software architectures of the three microprocessor sections on the HFC-SBC06 System Controller board.

Figure 7. Public Memory Data Stores

The IO Point Image data area holds Input and Output data values that are accessed by:

- the SYS processor during execution of the application program. The SYS processor uses the input data values as the inputs to the application programs and results of execution will be used to update the output data values.

- the ICL processor for storing Input values read from the I/O boards and retrieving Output values that need to be sent to the I/O boards over the ICL serial link;

- the CPC processor for DDB data broadcasts on the C-Link network.

The UCP message data stores hold UCP messages that need to be transferred between the microprocessors. UCP messages are point-to-point communication messages used in HFC control systems. The next section, Section 3.3 provides more descriptions of UCP messages. The UCP messages stored in the Public Memory are mainly operator commands or inquiries from operator workstations and responses from the SBC06 System Controller to the operator workstations. A UCP message is normally processed in the following sequences:

- The CPC processor receives a UCP message from the C-Link and stores it in the Public Memory if the message is not addressed to itself

- The SYS processor retrieves any UCP message addressed to itself from the Public Memory, executes the command and stores the UCP response messages in the Public Memory.

- The ICL processor retrieves any UCP message addressed to itself or ICL I/O boards in the Public Memory, and stores the UCP response message in the Public Memory

- The CPC processor retrieves any UCP response message from the Public Memory and transmits it to the C-Link

#### 3.3 *Remote Communication Architecture*

Remote communication is used when an HFC-SBC06 System Controller exchanges data with another System Controller, Operator Station, or Engineering Workstation. The HFC-SBC06 supports remote communication over the Communication Link (C-Link) network and provides dual network ports for connection to a redundant C-Link network. Two protocols are used to carry data over the C-Link network. These two protocols are:

- Dynamic Database (DDB) protocol. Refer to DS002-000-001, C-Link Protocol Component Design Specification for detailed descriptions of DDB protocol.

- Universal Communication Packet (UCP) protocol. Refer to DS002-000-003, UCP Protocol Component Design Specification for detailed descriptions of UCP protocol.

The use of one protocol versus the other depends upon whether the data being carried is information that is transferred on a regularly scheduled basis or whether the information is being transferred due to a system event. The DDB protocol is designed to carry data traffic occurring on a regularly scheduled basis, and the UCP protocol is designed to carry a periodic traffic such as operator commands and controller status inquiries.

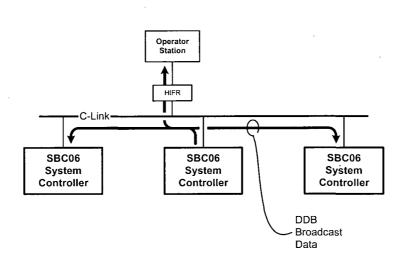

Figure 8. DDB Broadcast Data Paths

The Dynamic Database protocol is a broadcast protocol in which a transmitting node on the C-Link network broadcasts data packets to all nodes on the network. As shown in Figure 8, one network node, the HFC-SBC06 System Controller in center, is broadcasting DDB data while all other nodes are receiving DDB data. The DDB protocol is the method used for transferring system operating data, such as field input values, actuator output values, and control state values, among System Controllers and Operator Workstations. In the HFC-6000 system, DDB data is broadcast from each System Controller in a round-robin sequence.

The Universal Communication Packet protocol is designed as a point-to-point protocol for transferring data that is not sent on a regular basis during system operation.

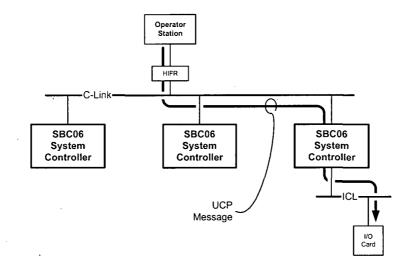

Figure 9. UCP Point-to-Point Message Path

An example of a typical UCP message is an operator query for the status of a device in the plant. As shown in Figure 9, the UCP message originates at the Operator Station and travels to the I/O board connected to the plant device for which the status is being queried.

The complete transaction for this UCP example message actually would consist of two UCP messages. The first message in the transaction would be a UCP request message sent from the Operator Station to the I/O board responsible for the operation of the device. The point-to-point message would be a request for the value control state. The second UCP message in the transaction would also be a UCP response message providing the device control state and going point-to-point from the I/O board to the Operator Station.

Network transmission control for the C-Link network uses a token passing mechanism. In a token passing transmission control scheme, a single node within the network holds the token, and the node with the token is the only one that is allowed to **transmit** data on the C-Link network at a given point in time. While the transmitting node has the token, all other nodes on the network can only receive data. Error detecting functions and mechanisms use network error timers running at each node that are designed to detect token passing errors such as "Lost Token", "Fail to Pass Token", "Fail to Claim Token", and "Token Claim Collision".

Remote communication for the HFC-SBC06 is handled by the CPC processor. However, data for remote communication may be produced or consumed by any of the three microprocessors on the HFC-SBC06 board. The next two sections describe the CPC processors handling of the data sent and received via remote communication.

#### 3.3.1 HFC-SBC06 Handling of DDB Data

As explained previously, the DDB protocol uses a broadcast of data for transferring information from one node to all other nodes on the network. Each HFC-SBC06 System Controller on the network must be able to both broadcast DDB data and receive DDB data. The specific information that the HFC-SBC06 broadcasts when it has possession of the token is specified in the DDB Broadcast Table. The actual data that is broadcast by the HFC-SBC06 is contained in the IO Point Image and Internal Point Image data stores, as shown in Figure 10. During a DDB broadcast, the CPC processor uses the Broadcast table to determine which data in the two Point Image data stores to select and broadcast on the C-Link.

Not all DDB data broadcast on the C-Link will typically be needed by an HFC-SBC06 for performing its required operations. When the HFC-SBC06 is receiving DDB data from the C-Link, a filter is applied to the data, and only the DDB data specified by the filter is processed CPC processor. As shown in Figure 10, the DDB Filter Table, which lists the DDB data that is needed by the particular HFC-SBC06, is used by the CPC processor to determine which incoming DDB data is to be processed and stored by the CPC processor in the DDB Image data store. DDB data from the C-Link that is **not** listed in the Filter is skipped by the CPC processor.

The I/O Scan Table lists all the configured I/O boards on the ICL for the SBC06 and board information, such as type of I/O points on board, number of points, and assigned point numbers.

The ICL processor uses the I/O Scan Table to determine which I/O board to scan, how to scan it, and where the I/O point values should be stored in the Public Memory.

#### 3.3.2 HFC-SBC06 Handling of UCP Messages

UCP messages are designed to be transferred on a point-to-point basis, and as such, any UCP message received by the HFC-SBC06 will either end up being processed by a task running on one of the three HFC-SBC06 processors, or will end up being passed to an I/O board attached to the HFC-SBC06 via the ICL serial network. UCP messages are received from the C-Link network by the CPC processor, which processes the message header to determine where to post the message. If the UCP message is destined for a task running on the CPC processor, the message is stored in a CPC data store for processing by the specific CPC task.

| HFC-6000                                       | ·    | HFC Non-proprietary |

|------------------------------------------------|------|---------------------|

| HFC-SBC06-DPM06 Board Module Design Specificat | tion |                     |

If the UCP message is not addressed to a CPC task, the message will be stored in message data store in Public Memory. As shown in Figure 11, a UCP message addressed to a task running on the SYS processor is stored in the SYS message data store in Public Memory. A UCP message that is addressed to a task running on the ICL processor, or a UCP message addressed to an I/O board, is stored in the ICL message data store in Public Memory.

UCP messages sent from a task running on either the SYS processor or the ICL processor, or a UCP response message received from an I/O board attached to the HFC-SBC06, is stored in respective message data store (SYS messages or ICL messages) in Public Memory.

Figure 11. UCP Message Processing

A message event mechanism, with events passed between processors using Public Memory, is used by a processor in the HFC-SBC06 to notify another processor in the HFC-SBC06 that a UCP message has been placed in its respective message data store. Refer to DS001-000-001, Operating System Component Design Specification for details of the UCP message event mechanism.

#### 3.4 SYS Processor Section

The SYS processor section is based on an Intel Pentium processor. Figure 12 shows the architecture of the SYS Processor section. The major functions of the SYS Processor section are as follows:

- Execution of application programs on I/O point images

- Coordination of the other two processors on board

- Monitoring overall controller status

Figure 12. System Processor Architecture

The SYS processor has access to the flash memory that has application programs installed. The application program consists of a sequential set of instructions that are executed by the Equation Interpreter software task. The Equation Interpreter processes the instructions from the application program to generate digital and analog output values using input values currently in

#### HFC-SBC06-DPM06 Board Module Design Specification

memory. The descriptions of architecture, interface and design of Equation Interpreter component are provided in DS001-000-002, Equation Interpreter Component Design Specification.

The application program in the SYS processor's flash memory also contains DDB Filter Table, DDB Broadcast Table, and I/O Scan Table. During controller initialization, the SYS processor copies these tables from its flash memory to the Public Memory for the use by the CPC Processor and the ICL Processor.

On the HFC-SBC06 board and HFC-DPM06 board, there are DIP switches for controller configuration. The SYS processor reads the switch settings and stores the configuration data in the Public Memory.

As the system processor, the SYS Processor performs initialization for the Public Memory during controller initialization. It configures the Public Memory according to the predefined structure. After the Public Memory Initialization is done, the SYS processor sets a READY flag in the Public Memory to inform the other two subordinate processors that the Public Memory is ready for use.

The other two subordinate processors report to the SYS Processor after they finish initialization successfully and wait for the SYS processor's indication as when to start operating. The SYS Processor, after verifying that all the processors on board have finished initialization, sets a System\_Go flag in the public memory, enabling normal operation to begin. The subordinate processors start normal operation after the System\_Go flag is set. Thus, the whole controller enters normal operation mode.

Each of the subordinate processor has a "Mailbox" in the Public Memory to report the status of the processor. During normal operation, the subordinate processor periodically updates its mailbox by loading a preset value into it. As a parallel process, the SYS processor monitors subordinate processor running status by decrementing the mailbox at preprogrammed intervals. The setting of mailbox preset value and mailbox decrementing amount and intervals determine how soon a failure of the subordinate processor can be detected.

The SYS processor also maintains the system watchdog timer (a MicroMonitor chip) by strobing the timer periodically. If the SYS processor fails to strobe the watchdog timer, the timer will time out and trigger a failover if the controller is in Primary mode. Refer to details of controller failure detection and failover mechanism in Section 3.7.

The SYS processor maintains a controller status flag in the Public Memory. In case of a status change, the SYS processor updates the controller status flag, so that the two subordinate processors will change their running mode from primary to secondary, or vice versa. This mechanism ensures that the whole controller operates in the same mode: either primary or secondary.

The SYS Processor is also responsible for transferring system status data between the Public Memory and the DPM periodically. If the SYS Processor is in primary mode, it transfers data from the Public Memory to the DPM. If the SYS Processor is in secondary mode, it transfers data from the DPM to the Public Memory. This mechanism keeps the secondary controller updated with system status data and ensures a smooth transition of control in case of a failover from primary controller to secondary controller.

#### 3.4.1 SYS Processor Software Architecture

The SYS Processor software consists of the following routines:

- Initialization

- Power up/Reset Initialization

- Controller Configuration

- Processor Specific Initialization

- Memory Initialization for Public Memory

- Task Initialization

- Operating System Component

- Processor Specific Tasks

- System Tasks

- DBM Tasks and System Database Manager

- Equalization Task for DPM

- Processor Status Monitor Task

- Equation Applications

- Equation Interpreter Task

- Logic Algorithms

- Analog Processing Algorithms CQ4 Block Algorithms

- Timer Interrupt Service Routines

- UCP Utility Component

- UCP Memory Manager

- Network Manager for Path-Element

- Network Message Routine

- UCP Message Handling Tasks

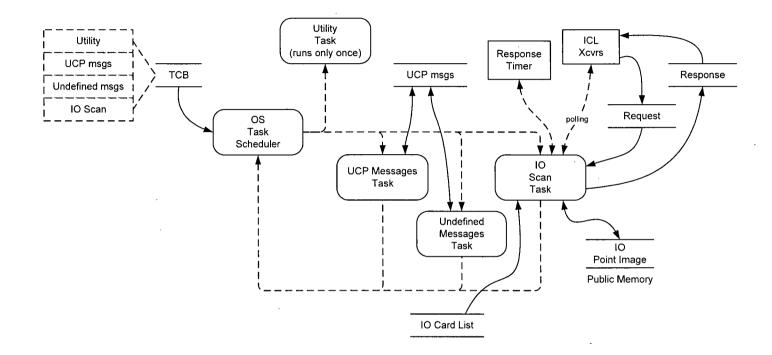

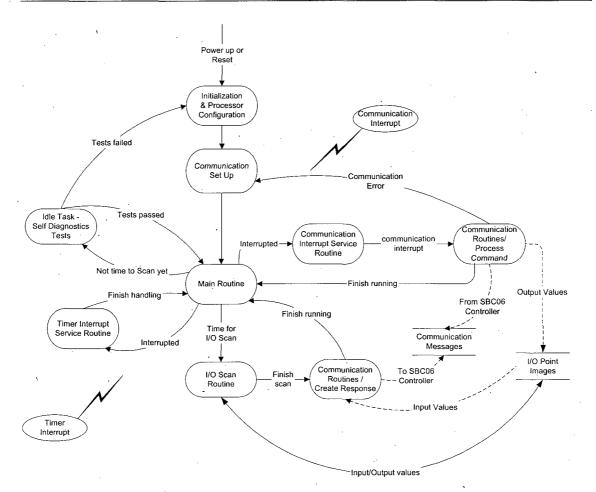

The SYS Processor software is designed based on an operating system common to all processors on the HFC-SBC06 board and a set of configurable tasks that will be run by the operating system. Figure 13 provides an overview of the SYS Processor Software Architecture. The Operating System is mainly a task scheduler, which executes the configured tasks one after another according to a task control block (TCB) list. Page 22 is intentionally left blank.

**HFC-6000** HFC-SBC06-DPM06 Board Module Design Specification

Figure 13. System Software Architecture

MS901-000-01

23 of 55

Rev E

The tasks running on the SYS processor are:

- Equation Interpreter Task for running the application program on I/O point images. This is implemented by individual logic subroutines and analog processing algorithms. o IOSS TSK

- UCP Message Handling Tasks which will process the UCP message and call the appropriate routines to provide service to the UCP requests. The services requested include:

- CQ4INT CQ4 block update

- PIDTSK PID block task,

- DBMTSK DBM Task for I/O point images in the Public Memory 0

- XEQUAL Equalization Task for DPM 0

- **EQMSGTSK** Equation Interpreter service 0

- PKTXHG Packet exchange service 0

- UNDEFTSK handling undefined UCP messages 0

- OFFLINETSK handling UCP messages from EWS workstation intended for offline controllers for updating various controller configuration information. The Equation Interpreter will be stopped so that the application programs will not be executed.

- Operating System tasks:

- UTILTSK Performs configured initialization and utility functions

- o UCPTSK UCP message activity monitoring task

- System processor tasks, such as

- o STATSK Processor Status Monitor Task

- o IOSTSK I/O Simulation Task for simulation of the operation of control system like I/O image changes without the presence of real field devices.

- BLRQ Build DDB Filter Task, etc.

During initialization, the SYS processor configures several Mailbox utility functions for the OS Utility Task. These mailbox functions are essential to determine the System Controller's Sanity. During every Operating System task scan cycle, these functions will be executed by the Utility Task according to the operation mode of the controller: Primary or Secondary. Refer to Section 3.7.2 for detailed descriptions.

Existing software components will be used to build the SYS Processor software. All of the above tasks, the Operating System and UCP Network Utilities are covered by Component Design Specifications. Refer to Section 5 for the reference document numbers.

The descriptions of Initialization Process are provided in the DS901-000-001, HFC-SBC06 Module Detailed Design Specification.

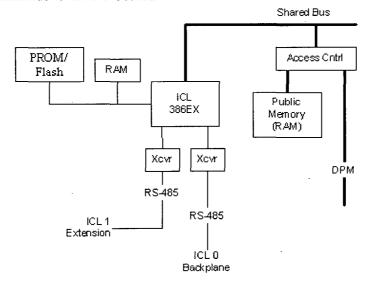

#### 3.5 ICL Processor Section

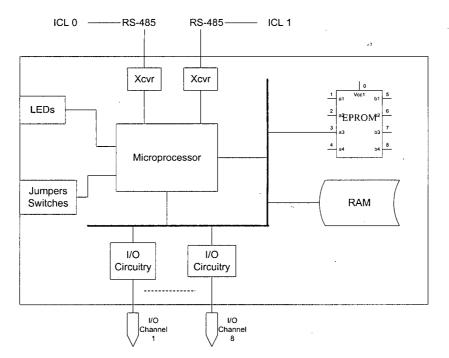

The ICL Processor section is based on an Intel 386 processor. Figure 14 shows the architecture of the ICL Processor section. The major function of the ICL Processor section is to handle communication on the ICL to obtain current plant status information from the I/O boards and to send operation commands to the I/O boards.

Figure 14. ICL Processor Architecture

The control system interface to field devices in the plant, such as process input sensors and output actuators, is handled by I/O boards mounted in the HFC-6000 board rack. The I/O boards measure signals from field device inputs, convert the measurements to digital images, and control output drive-level signals to plant actuators. The output drive-level signals are the converted values of output images sent to the I/O board from the HFC-SBC06.

The digital images the HFC-SBC06 receives from and sends to the I/O boards are carried by the ICL network that connects the HFC-SBC06 System Controller to its I/O boards. The ICL is structured as an RS-485 network implementing a master/slave communication control protocol. The HFC-SBC06 System Controller board provides the network master function and controls communication on the connected ICL network connected to it. Each I/O board operates as a slave node on the ICL network to which it is attached. The System Controller polls each I/O board, requesting data values for field inputs connected to the I/O board and sending data values for field outputs connected to the I/O board will initiate a communication on the ICL with a request message.

The HFC-SBC06 System Controller board has two serial channels: ICL0 and ICL1. ICL0 is on the controller backplane, but it has a connector on the backplane so that it can access boards in expander chassis. ICL1 only goes to expander chassis. Both channels can communicate with

boards in up to two chassis. ICL0 and ICL1 will be connected to different I/O boards but they are logically one ICL. In a redundant configuration, each of the dual serial ports of an I/O board is connected to one of the redundant controllers via an ICL.

The ICL Processor has access to the DPM. This capability is used in a redundant configuration for the secondary ICL Processor to takes over the scan task of an I/O board if the primary ICL does not function well with a particular I/O board. If an I/O board does not respond to a regular poll message from the primary ICL Processor, the primary ICL Processor transfers the request message to a dedicated area in the DPM for the secondary ICL Processor to poll that particular I/O board. If the secondary ICL is functional, the secondary ICL processor takes over the scan task for that I/O board and uses the DPM to pass the response data to the primary ICL Processor. Periodically, the secondary ICL Processor performs a loopback test for that I/O board to determine if the primary link is functioning. If the loop test results show that the primary ICL is functioning properly with that I/O board, the primary ICL resumes polling this I/O in its normal sequence.

#### 3.5.1 ICL Software Architecture

The ICL Processor software consists of the following routines:

- Initialization

- Power up/Reset Initialization

- Controller Configuration

- Processor Specific Initialization

- ICL Communication Initialization

- Operating System Component

- Processor Specific Tasks

- o ICL Scan Task

- ICL Download Table Routine

- ICL Scan Routine

- Primary Mode Routine

- Build ICL Command

- Perform Transaction Routine

- Process Response Routines

- Secondary Mode Routine

- Communication Utility Routines

- Send Message Routine

- Receive Message Routine

- ICL Utilities

$\triangleright$

- Timer Interrupt Service Routines

- UCP Utilities

- UCP Memory Manager

- Network Manager for Path Element

- Network Message Routine

HFC-6000 HFC-SBC06-DPM06 Board Module Design Specification

Figure 15. ICL Software Architecture

The ICL Processor software is also designed based on the operating system component common to all processors on the HFC-SBC06 board and a set of configurable tasks that will be run by the operating system. Figure 15 provides an overview of the ICL Processor Software Architecture.

The tasks running on the ICL Processor are:

- ICL I/O Scan Task:

O IOFSCN

- UCP Message Handling Tasks which will process the UCP message and call the appropriate routines to provide service to the UCP requests. The services requested include:

- UNDEFTSK handling undefined UCP messages

- OFFLINETSK handling UCP messages intended for offline controllers for updating various controller configuration information

- Operating System tasks:

- UTILTSK No utility routines configured

- UCPTSK UCP message activity monitoring task

The ICL Processor software does not have any special utility functions configured for the OS Utility Task. So after finishing the initialization part of functions, the OS Utility Task will remove its self from the OS task control block list and will not be executed again.

The existing software components will be used to build the ICL Processor software. All of the above tasks, the Operating System and UCP Network Utilities will be described in Component Design Specifications. Refer to Section 5 for the reference document numbers.

The descriptions of Initialization Process are provided in the DS901-000-001, HFC-SBC06 Module Detailed Design Specification.

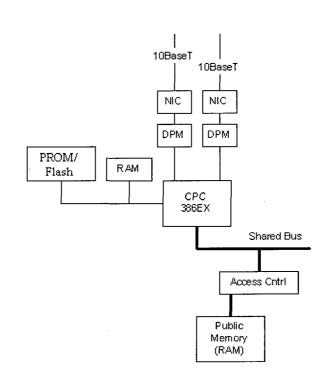

#### 3.6 CPC Processor Section

The CPC Processor section is based on an Intel 386 processor. Figure 16 shows the architecture of the CPC Processor section. The CPC Processor section includes hardware for two identical Ethernet channels with twisted pair 10BaseT configuration. The Ethernet interface is implemented with two serial interface network controller chips (NIC). The 10BaseT interface to the C-Link functions in accordance with IEEE 803.2 standards.

The NICs incorporate receiver, transmitter, collision detection, heartbeat, jabber timer, and link integrity test functions. There is one DPM between each NIC and the CPC processor. This DPM provides the memory buffer for the messages received and to be transmitted by the NIC.

The CPC processor controls overall operation of the Ethernet interface to the C-Link, transfer of data to or from the NIC via the DPM, and transfer of data to and from the Public Memory.

Figure 16. CPC Processor Architecture

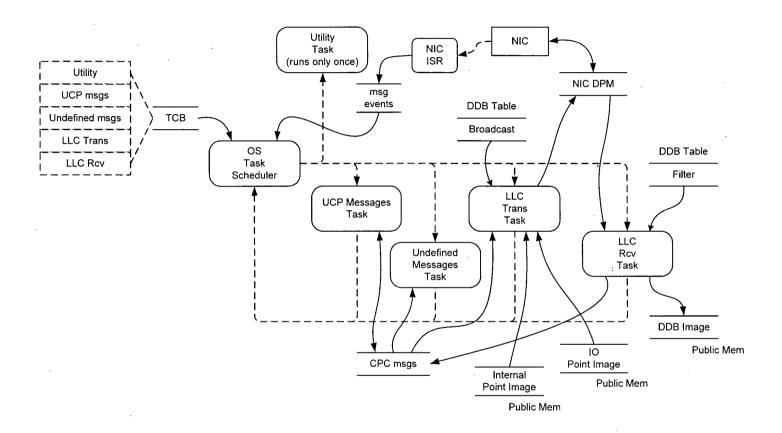

#### 3.6.1 CPC Processor Software Architecture

The CPC Processor Software consists of the following routines:

- Initialization

- Power up/Reset Initialization

- Controller Configuration

- Processor Specific Initialization

- NIC Initialization

- Tasks Initialization

- Data Initialization

- Interrupt Vectors Initialization

- Operating System Component

- Processor Specific Tasks Communication Tasks

- Transmit Tasks

- Interface Transmit Task

- LLC Transmit Task

- NIC Transmit Driver

HFC-SBC06-DPM06 Board Module Design Specification

- Receive Tasks

- Receive ISR

- LLC Receive Task

- Interface Receive Task

- Timer Interrupt Service Routines

- Timer 0 ISR

- Timer 1 ISR

- Timer 2 ISR

- o DDB Process Routine

- Get DDB Routine

- Put DDB Routine

- Save DDB Routine

- UCP Utilities

- UCP Memory Manager

- o Network Manager for Path Element

- Network Message Routine

The CPC Processor software is also designed based on the operating system component common to all processors on the HFC-SBC06 board and a set of configurable tasks that will be run by the operating system. Figure 17 provides an overview of the CPC Processor Software Architecture.

The tasks running on the ICL Processor are:

- C-Link Communication Tasks:

- LLCRCV LLC layer receive task

- LLCTRN LLC layer transmit task

- ITFRCV Interface layer receive task

- ITFTRN Interface layer transmit task

- UCP Message Handling Tasks which will process the UCP message and call the appropriate routines to provide service to the UCP requests. The services requested include:

- UNDEFTSK handling undefined UCP messages

- OFFLINETSK handling UCP messages intended for offline controllers for updating various controller configuration information

- Operating System tasks:

- UTILTSK No utility routines configured

- UCPTSK UCP message activity monitoring task

Figure 17. CPC Software Architecture

The CPC Processor software does not have any special utility functions configured for the OS Utility Task. So after finishing the initialization part of functions, the OS Utility Task will remove its self from the OS task control block list and will not be executed again.

The existing software components will be used to build the CPC Processor software. All of the above tasks, the Operating System and UCP Network Utilities will be described in Component Design Specifications. Refer to Section 5 for the reference document numbers.

The descriptions of Initialization Process are provided in the DS901-000-001, HFC-SBC06 Module Detailed Design Specification.

#### 3.7 HFC-SBC06 and HFC-DPM06 Redundancy Architecture

Refer to Section 2.2 for descriptions of Redundant System Controllers. Two HFC-SBC06 boards and a HFC-DPM06 board in the redundant configuration are installed in the three leftmost slots of the HFC-6000 controller rack, with the DPM06 board installed between the two HFC-SBC06 boards. The three boards include hardware and software designed to support redundant controller operation. The main functions of the redundant architecture are as follows:

- Logic to determine controller operation mode: Primary or Secondary

- Failover mechanism on failure of primary controller

- Manual maintenance failover

- Controller failure detection mechanism

- Mechanism to ensure a smooth transition of control during failover

XXXXX

HFC-6000 HFC-SBC06-DPM06 Board Module Design Specification HFC Non-proprietary

Figure 18. HFC-SBC06 Redundancy and Failover

#### HFC-6000 HFC Non-proprietary HFC-SBC06-DPM06 Board Module Design Specification

During the start up of redundant controllers, the SANE signals in both controllers are inactive, and so are the PRI signals. The controller that finishes initialization first sends a strobe to its watchdog timer first. The Sanity circuit sets both the SANE and PRI signals true. The SYS Processor software of this controller reads the PRI signal to determine its operation mode, sets a remote operation status flag to Primary in the Public Memory, and starts operating in Primary mode. The other two subordinate processors of this controller read the operation mode flag in the Public Memory and start operating in Primary mode too. On a parallel process, the other controller finishes initialization, strobes its watchdog timer and becomes sane, but its Sanity circuit can not set the PRI signal to true, because the PRI signal from this controller is already true. So every processor on the other controller will operate in Secondary mode.

The SYS Processor software strobes the Watchdog Timer periodically, so that the SANE signal from the Sanity circuit will remain true. If the software fails to strobe the Watchdog Timer, the watchdog timer will time out. The SANE status signal will then be disabled. The change in SANE signal from true to false will cause the PRI signal to become false. If the controller is currently in secondary mode, the maintenance failover function will be disabled to prevent manual activation of failover while the secondary controller is not functioning properly. If the controller is currently in primary mode, a failover will be triggered. The current primary controller will become secondary, and the current secondary controller will become primary. During the failover process, the SYS Processor detects the need for an operation mode change first by comparing the hardware PRI signal with its current remote operation status. It changes its remote operation status flag in the Public Memory and sets the Synchronization of operation status is needed for all tasks running on that processor. After each processor is synchronized, the Operating System on the SYS Processor will clear the Synchronization flag.

As long as both controllers are operating normally (SANE and all applications data validated), the failover circuit on the DPM06 board activates an output to the LED DS1. This display indicates that the maintenance failover function is available. If the user presses the maintenance failover button on the DPM06 board, the failover circuit activates a SEC\_REQ signal for controller A if it is currently the Primary controller, or a PRI\_REQ signal if it is currently the Secondary controller. This signal causes controller A to initiate failover to controller B by setting its PRI status from Primary to Secondary (with SEC\_REQ signal) or from Secondary to Primary (with PRI\_REQ signal). Assuming that controller A is the current primary controller, the change of its PRI status will cause the current secondary controller to change its PRI from Secondary to Primary. However, if one of the two controllers loses SANE status, the DS1 LED goes out, and the maintenance failover function is disabled.

Additional information of the Failover Mechanism and DPM Transfer is provided in DS001-000-08, Failover Mechanism Component Design Specification.

#### 3.8 HFC-SBC06 CPLD Design

XXXXX

#### 3.9 Sequence of Events Timer

The HFC-SBC06 system controller maintains a Sequence of Events (SOE) timer over 24 consecutive hours of operations. The SOE timer is used for "time tagging" events that occur system wide. This timer can be synchronized by some master SOE timer located elsewhere in the system, or can be the master timer itself. The SOE timer provides a resolution of 100  $\mu$ S for synchronizing similar SOE timers on each I/O boards.

XXXXX

#### 3.10 HFC-DPM06 Board

The HFC-DPM06 board provides three onboard DIP switches for the configuration settings of the HFC-SBC06 System Controller board. It also provides a dual ported memory, a failover circuit, LEDs, four bus driver chips, and a maintenance failover push button for redundant controller configuration.

There is a CPLD on the HFC-DPM06 board. This CPLD supports arbitration and bus control functions and maintenance failover. It receives a set of status and control signals from both the redundant System Controller boards. The resulting outputs from the CPLD control operation of the four onboard bus drivers and status displays on the board edge LEDs. The same CPLD also provides logic to support the failover mechanism for redundant system controller configuration.

#### 4. Configuration Setup and LED Displays

The HFC-SBC06 board contains one 8-position DIP switch, two toggle switches and nine jumpers. The switches and jumpers enable manual control of reset, hardware configuration, and programming of the board. Additional configuration switches are physically located on the HFC-DPM06 common board.

#### 4.1 HFC-SBC06 Onboard Switch Functions

- SW1 Power on/off, RESET

- SW2 Positioned down (toward the board) permits write cycles to onboard flash memory chips. The switch is placed in this position to program flash memory for the ICL and CPC processors and to download the application program to the flash memory of the SYS processor.

Positioned away from the board enables a write-protect function for flash memory. For safety-related applications, the switch should remain in this position for normal operation.

SW4 8-position DIP switch defines operating modes and control parameters as indicated in Table 1.

HFC-5BC06-DPM06 Board Module Design Specification

| Switch | Function |  |

|--------|----------|--|

| SW4-1  | xxxxx    |  |

| SW4-2  | xxxxx    |  |

|        | xxxxx    |  |

|        | xxxxx    |  |

| SW4-3  | xxxxx    |  |

| SW4-4  | xxxxx    |  |

| SW4-5  | xxxxx    |  |

| SW4-6  | xxxxx    |  |

| SW4-7  | xxxxx    |  |

| SW4-8  | XXXXX    |  |

Table 1. SYS Processor Configuration Switches

### 4.2 HFC-DPM06 Onboard Switch Functions

Three eight-position DIP switches on the DPM common board control values for the following parameters:

### 4.3 HFC-SBC06 Onboard Jumper Options

Table 2 defines the function of each jumper included on the HFC-SBC06 controller.

### HFC-6000 H HFC-SBC06-DPM06 Board Module Design Specification

| Jumper | Function |

|--------|----------|

| J1     | XXXXX    |

|        |          |

|        |          |

| -      |          |

| J8     | XXXXX    |

|        |          |

|        |          |

|        |          |

|        |          |

| W2     | XXXXX    |

|        |          |

|        |          |

|        |          |

| W3     | XXXXX    |

|        |          |

| W5     | XXXXX    |

|        |          |

|        |          |

| W/C    |          |

| W6     | XXXXX    |

| J5     | xxxxx    |

| E1, E2 | xxxxx    |

|        |          |

### Table 2. Jumper Options

MS901-000-01

Rev E

### 4.4 LEDs

The HFC-SBC06 board contains eight board-edge LEDs, which provide a visual indication of functional status of the controller hardware and software. The HFC-DPM06 board contains five board-edge LEDs, which provide a visual indication of functional status of the controller.

### 4.4.1 HFC-SBC06 LED Functions

DS1 Includes four LEDs to indicate hardware status of the Ethernet interface as follows:

- DS1-1 flashes on for approximately 50 ms when C-Link channel 1 transmits in TPI mode.

- DS1-2 flashes on for approximately 50 ms when receive data is detected for C-Link channel 1 in TPI mode.

- DS1-3 flashes on for approximately 50 ms when C-Link channel 0 transmits in TPI mode.

- DS1-4 flashes on for approximately 50 ms when receive data is detected for C-Link channel 0 in TPI mode.

- DS2 Includes four LEDs. Two LEDs are controlled directly by the P1.6 and P1.7 ports of the ICL microprocessor, and two are controlled by the corresponding ports of the CPC microprocessor.

DS3 and DS4 Includes 8 LEDs controlled by the SYS Processor. Refer to Section 4.4.1.1.

#### 4.4.1.1 **DS3 and DS4 LEDs**

If the SYS processor detects a failure condition during system initialization/reset, the display freezes with the LEDs displaying a binary code for that fault. Table 3 lists the defined error codes and the error conditions that they represent. Throughout normal operation, the LED display represents a binary code for different processor tasks, and the LED code for a particular task lights while it is running. As a result, all 16 LEDs flicker constantly during this phase of operation. The bottom LED is always on when the board is running normally. Table 4 lists the defined task LED code. If the board detects a failure condition during normal operation, the display freezes with the LEDs displaying a binary code for that fault. Table 5 lists the defined error codes and the error conditions they represent.

| Code            | Error Condition |

|-----------------|-----------------|

| 01 <sub>H</sub> | XXXXX           |

| 02 <sub>H</sub> | XXXXX           |

| 03 <sub>H</sub> | xxxxx           |

| 04 <sub>H</sub> | XXXXX           |

| 05 <sub>H</sub> | XXXXX           |

| 06 <sub>H</sub> | xxxxx           |

| 07 <sub>н</sub> | xxxxx           |

| 08 <sub>H</sub> | XXXXX           |

| 09 <sub>H</sub> | XXXXX           |

| 0A <sub>H</sub> | XXXXX           |

| 0B <sub>H</sub> | XXXXX           |

| 0C <sub>H</sub> | XXXXX           |

| 0D <sub>H</sub> | xxxxx           |

| 0E <sub>H</sub> | xxxxx           |

| 0F <sub>H</sub> | XXXXX           |

| 10 <sub>H</sub> | XXXXX           |

| 11 <sub>H</sub> | xxxxx           |

| 12 <sub>H</sub> | xxxxx           |

| 13 <sub>H</sub> | xxxxx           |

| 14 <sub>H</sub> | xxxxx           |

| 15 <sub>H</sub> | xxxxx           |

| 16 <sub>H</sub> | XXXXX           |

| 17 <sub>н</sub> | XXXXX           |

| 18 <sub>H</sub> | xxxxx           |

| 19 <sub>H</sub> | XXXXX           |

| 1A <sub>H</sub> | XXXXX           |

Table 3. DS3 and DS4 LED Indications for Initialization Failure

| Bit   | Hex               |       | Task |

|-------|-------------------|-------|------|

| 0     | 1 <sub>H</sub>    | XXXXX |      |

| 2     | 4 <sub>H</sub>    | XXXXX |      |

| 3     | 8 <sub>H</sub>    | XXXXX |      |

| 5     | 20 <sub>H</sub>   | XXXXX |      |

| 6     | 40 <sub>H</sub>   | XXXXX |      |

| 7     | 80 <sub>H</sub>   | XXXXX |      |

| 9     | 200 <sub>H</sub>  | XXXXX |      |

| 10    | 400 <sub>H</sub>  | XXXXX |      |

| 11    | 800 <sub>H</sub>  | XXXXX |      |

| 15    | 8000 <sub>H</sub> | XXXXX |      |

|       |                   |       |      |

| Other | Other             | XXXXX |      |

Table 4. DS3 and DS4 LED Indications for Individual Tasks

#### Table 5. DS3 and DS4 LED Failure Indications During Normal Operation

| Code                             | Error Condition                                                                                                    |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 01 <sub>H</sub>                  | XXXXX                                                                                                              |

| 02 <sub>H</sub>                  | XXXXX                                                                                                              |

| 03 <sub>H</sub>                  | XXXXX                                                                                                              |

| 04 <sub>H</sub> -10 <sub>H</sub> | XXXXX                                                                                                              |

| 11 <sub>H</sub>                  | XXXXX                                                                                                              |

| 12 <sub>H</sub>                  | XXXXX                                                                                                              |

| 13 <sub>H</sub>                  | XXXXX                                                                                                              |

| 14 <sub>H</sub>                  | XXXXX                                                                                                              |

| 15 <sub>H</sub>                  | XXXXX                                                                                                              |

|                                  | cessor failure codes are defined, but they are functional only if that<br>or is configured for the control system. |

#### 4.4.2 HFC-DPM06 LED Functions

- DS1 Lights when the maintenance failover function is available (controller A and controller B both sane).

- DS2 Lights when controller A is primary.

- DS3 Lights when controller A is sane.

- DS4 Lights when controller B is primary.

- DS5 Lights when controller B is sane.

HFC-SBC06-DPM06 Board Module Design Specification

#### 4.5 Installation of System Software and Application Programs

Each of the three onboard processors has a dedicated flash memory and a dedicated PROM for system software. SYS processor also has a dedicated flash memory for its application program code. Switch and jumper selections on the board cause the processor to boot from either the PROM or the flash memory.

XXXXX

#### 4.5.1 System Code Transfer to Flash

Initially, the flash memory chips are blank. The following steps describe the procedural sequence required to transfer system software code to each of the onboard flash memory chips.

- 1. Install jumper J1 to enable the SYS processor to boot from its system code PROM.

- 2. Install the PROM containing system software for the SYS processor in socket U52.

- 3. Set DIP switch SW4-8 in the ON (toward the board) position.

- 4. Install jumper J8 to enable the ICL and CPC processors to boot from their system code PROMs.

- 5. Install the PROM containing the system software for the ICL processor in socket U7.

- 6. Install the PROM containing the system software for the CPC processor in socket U8.

Make sure that S1 is positioned toward the board before installing it in the board rack. If SW1 is positioned away from the board and power is applied to the rack, power transients could damage components on the board.

7. Mount the board in a controller slot of the HFC-6000 controller board rack.

- HFC-SBC06-DPM06 Board Module Design Specification

- 8. Ensure that power is applied to the board rack, and position S2 toward the board to enable write cycles to flash memory.

- 9. Ensure that power is applied to the board rack, and position SW1 away from the board.

- 10. Following application of operating power, the system software will be transferred from U52 to the flash memory for the SYS processor. Successful transfer will be indicated by the following:

- LED01 lights for several seconds and then goes out.

- LED00 through LED07 light in sequence.

- 11. The system software for the ICL and CPC processors should be transferred to flash memory.

#### NOTE

As long as J1 remains installed, the SYS processor will boot from the PROM installed in socket U52. That code will be compared with the code currently in flash memory; and if it is different, the contents of PROM will be transferred to flash memory and the processor will operate from that code. If J1 is removed, the SYS processor will boot from the flash memory without examining the contents of its PROM.

As long as J8 remains installed, the ICL and CPC processors will boot from their respective PROMs. If SW2 is positioned as write enable, the contents of the PROMs will also be transferred to the flash memories for the two processors.

12. After the installation of the system software to flash, do the following:

- Remove jumper J1.

- Set DIP switch SW4-8 OFF (away from the board).

- Leave jumper J8 installed (for current software design).

#### 4.5.2 Application Code Download

The application program codes can be compiled by an EWS workstation software and downloaded to the controller over the C-Link. This download can be repeated following any modification or update to the application code during application development; however, the download function should be disabled during normal operation to prevent inadvertent changes to the application.

1. Set S1 toward the board to remove power from the board.

- 2. DIP SW4 can be set to place the software in offline mode (SW4-1 ON and SW4-2 OFF). While operating in this mode, the system software runs normally, but the equation interpreter task does not run.

- 3. Set S2 toward the board to enable flash write cycles.

- 4. For redundant controllers, set SW4-5 ON.

- 5. For redundant controllers, repeat steps *1* through *4* for the second controller.

- 6. Set S1 away from the board to enable distribution of operating power on the board (both controllers for redundant configurations).

- 7. At the EWS workstation, compile the final application code for the controller.

- 8. Download the equations, RQ file, and CQ4 blocks, as applicable.

- 9. For redundant controllers, initiate failover to the secondary controller.

- 10. Download the equations, RQ file, and CQ4 blocks as applicable.

- 11. Set S2 away from the board to disable flash memory write cycles.

- 12. If the controller was placed in offline mode, power down the controller and set both SW4-1 and SW4-2 OFF to enable normal operation. Power the controller up to enable controller operation to begin.

### 4.5.3 System Software Updates

If an upgrade is provided for the system software of one or more processors on the controller board following installation, repeat the procedure described ion paragraph 4.5.1. Direct download of system programs code to flash memory is not presently supported.

### 4.6 Hardware Configuration

Refer to Tables 1 and 2 for a general definition of functions controlled by the onboard switches and jumpers. The following steps identify typical switch and jumper settings required for normal operation. Record the specific DIP switch settings required for each controller to be used in the system.

# CAUTION

Make sure that S1 is positioned toward the board before removing or installing the board in the board rack. If SW1 is positioned away from the board and power is applied to the rack, power transients could result in damage to components on the board.

- 1. Set SW4-1 and SW4-2 on the HFC-SBC06 board both in the open position. This configuration enables normal run mode for the system software.

- 2. If the controller is used as part of a redundant pair, set SW4-5 closed. This enables regular transfers of status from the primary to the secondary via the HFC-DPM06 array.

- 3. Set SW4-6 closed. This enables the sanity function.

- 4. Set SW4-7 and SW4-8 both open. This disables software downloads from the EWS workstation.

- 5. Set DIP switches on the HFC-DPM06 board to provide the following configuration parameters:

- Set SW2 to the binary value for the remote number assigned to this controller. The valid range is from 0 to 255.

- Set SW4 to the binary value for the total number of remotes configured for this system (up to 255).

- Set SW1 to the binary value for the sequence number of this remote on the C-Link. The valid range is from 0 to 31.

# CAUTION

The remotes must be configured on the C-Link in numeric sequence with the HIFR assigned the sequence number of 0. If any remote is installed out of sequence, reliable communication with that remote over the C-Link could be disrupted.

6. When the HFC-SBC06 board is used as a redundant controller, a jumper should be installed from node J5–1 to J5–2. This hardware interlock requires the controller chassis to complete its power up initialization sequence successfully (SANE status TRUE) and become the primary controller before the ICL processor can begin transmitting over its serial link. Removing all jumpers results in a configuration in which the transmit interface remains enabled as long as logic power is present.

### 5. Module Design Constraints

The following is a list of specifications that constraint the design of an HFC-SBC06 board module.

### 5.1 Communication Interface Specifications

- Document DS002-000-01, C-Link Protocol Component Specification

- Document DS002-000-02, ICL Protocol Component Specification

- Document DS002-000-03, UCP Protocol Component Specification

### 5.2 Operating System Specification

- Document DS001-000-01, Operating System Component Design Specification

- Document DS001-000-02, Equation Interpreter Component Design specification

- Document DS001-000-03, CQ4 Component Design Specification

- Document DS001-000-06, System Component Design Specification

- Document DS001-000-07, Job Component Design Specification

- Document DS001-000-08, Failover Mechanism Component Design Specification

### 5.3 Hardware Interface Specifications

- Document 40040901, HFC-BPC01-19 Backplane Specification

- Document 40041401, HFC-BPE01-19 Backplane Specification

- Document DS901-000-34, HFC-BPC01-23 Backplane Specification

- Document DS-901-000-35, HFC-BPE0-23 Backplane Specification

- Document DS-901-000-36, HFC-BPC02-23 Backplane Specification

- Document DS-901-000-37, HFC-BPC02A-23 Backplane Specification

- Document DS901-000-38, HFC-BPC03-23 Backplane Specification

### 5.1 Design Safety

#### 5.4.1 Main Processor – SC Code

# 5.4.1.1 Criticality

Xxxxx

### 5.4.1.2 Hazard

Xxxxx

xxxxx

# 5.4.1.3 Security

.xxxxx

### 5.4.1.4 Risk

Xxxxx

### 5.4.2 ICL Processor – SAP Code

# 5.4.2.1 Criticality

xxxxx

### 5.4.2.2 Hazard

# 5.4.2.3 Security

### 5.4.2.4 Risk

HFC-6000 H HFC-SBC06-DPM06 Board Module Design Specification

. •,

XXXXX

MS901-000-01

52 of 55

### 5.4.3 C-Link Processor – SEP Code

# 5.4.3.5 Criticality

XXXXX

### 5.4.3.6 Hazard

xxxxx

### 5.4.3.7 Security

XXXXX

### 5.4.3.8 Risk

Xxxxx

MS901-000-01

55 of 55

**HFC Non-proprietary**

**HF** Controls Corporation HFC-6000 Product Line **I/O Module** Design Specification MS901-000-02 Rev Effective Date 1/29/2009 Gregory Rochford Author Pat Thibodeau Reviewer Approval David Briner

Copyright<sup>©</sup> 2009 HF Controls Corporation

HFC-6000 Product Line I/O Module Design Specification HFC Non-proprietary

### **Revision History**

| Date     | Revision | Author     | Changes                      |

|----------|----------|------------|------------------------------|

| 10/23/03 | 0        | B Han      | Initial                      |

| 11/11/03 | 1        | B Han      | Review comments incorporated |

| 11/18/03 | A        | B Han      | Review comments incorporated |

| 2/23/07  | В        | J Taylor   | SCR 1766                     |

| 1/27/09  | С        | G Rochford | Review comments incorporated |

|          |          |            | · · ·                        |

|          |          |            |                              |

|          |          |            |                              |

|          |          |            |                              |

# Table of Contents

| 1. IN | TRODUCTION                             | 4  |

|-------|----------------------------------------|----|

| 2. FU | UNCTIONAL DESCRIPTION                  | 5  |

| 3. M  | ODULE ARCHITECTURE                     |    |

| 3.1   | I/O BOARD ARCHITECTURE                 | 6  |

| 3.2   | ADDRESS SPACE ARCHITECTURE             |    |

| 3.3   | SOFTWARE ARCHITECTURE                  |    |

| 3.3.1 | X86 SOFTWARE ARCHITECTURE              | 11 |

| 3.3.2 |                                        |    |

| 3.3.3 | FAULT DETECTION AND PROCESSING         | 16 |

| 3.4   | ONBOARD SWITCHES, JUMPERS, AND LEDS    | 16 |

| 4. M  | ODULE DESIGN CONSTRAINTS               | 17 |

| 4.1   | COMMUNICATION INTERFACE SPECIFICATIONS | 17 |

| 4.2   | DETAILED DESIGN SPECIFICATIONS         | 17 |

| 5. DE | ESIGN SAFETY                           | 17 |

| 5.1   | Common Modules                         | 17 |

| 5.1.1 | Security                               |    |

| 5.1.2 | RISK                                   |    |

| 5.2   | OUTPUT MODULES                         | 19 |

| 5.2.1 | CRITICALITY                            | 19 |

| 5.2.2 | HAZARD                                 |    |

| 523   | Risk                                   | 20 |

# HFC-6000 Product Line I/O Module Design Specification

| 5.3<br>5.3.1<br>5.3.2<br>5.3.3 | INPUT MODULES<br>CRITICALITY<br>HAZARD<br>RISK                                                                                      | 21<br>21 |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2.<br>Figure 3.         | HFC-6000 System Hierarchy<br>HFC I/O Board Module Architecture<br>ICL Communication Architecture<br>I/O Board Software Architecture | 7<br>9   |

### MS901-000-02

### 1. Introduction

The HFC-6000 distributed control system provides plant monitoring and control capabilities with monitoring and control responsibilities spread over multiple remote control units. The I/O boards are sensors and drivers for implementing plant control functions. They provide signal-level interfaces to the equipment and devices in the plant. As shown in Figure 1, an HFC-6000 I/O board is positioned in the HFC-6000 system hierarchy between the HFC-SBC06 System Controller(s), which is the CPU of HFC-6000 system, and the equipments and devices in the plant.

Figure 1. HFC-6000 System Hierarchy

Descriptions and discussions of the functional requirements of the HFC-6000 I/O boards are provided in 700901-06, *HFC-6000 Product Line General I/O Card Requirements Specification*.

Subsequent sections of this document provide top-level architectural and design descriptions of HFC-6000 I/O boards. Two different designs are currently in use. In general, the digital I/O boards employ a common processor kernel based on an xxx microprocessor. The assemblies with AI channels use a Digital Signal Processor (DSP) to control the main processing functions. Both designs provide a common architecture that is used on multiple assemblies. Lower level descriptions of each I/O board are contained in a separate Detailed Design Specification for each board type. The design descriptions of the common software modules and the common hardware characteristics are covered in the individual *HFC-6000 I/O Board Module Detailed Design Specifications*. The purpose of this document is to present the methods and strategies used to accomplish the operation and functions required of an HFC-6000 I/O board. The discussion of the operation and function of an HFC-6000 I/O board are presented using architectural, design, and implementation information.

### 2. Functional Description

This section describes the major functions performed by both design implementations of HFC-6000 I/O boards. The functional descriptions are presented to provide a context for understanding the internal operation of an HFC-6000 I/O board and how the functions performed by an HFC-6000 I/O board work within the overall architecture of the HFC-6000 distributed control system.

The major functions performed by an HFC-6000 I/O Board are:

- Initialization

- Communication with system controller connected to an Inter-Communication Link (ICL)

- Setting each digital/analog output channel using digital output images, and/or getting digital input images from each digital/analog input channel

- Self diagnostics functions

An I/O board generally has two operation stages: Initialization state and Normal Operation state. Upon power up or reset, the processor firmware will accomplish initialization for hardware, software, and communication set up. During initialization, some self diagnostics tests will be performed, such as RAM Write/Read test and EPROM/flash checksum test. Any error detected at this state is fatal and will cause the software to halt execution.