# Review Guidelines for Field-Programmable Gate Arrays in Nuclear Power Plant Safety Systems

# AVAILABILITY OF REFERENCE MATERIALS IN NRC PUBLICATIONS

#### **NRC Reference Material**

As of November 1999, you may electronically access NUREG-series publications and other NRC records at NRC's Public Electronic Reading Room at http://www.nrc.gov/reading-rm.html. Publicly released records include, to name a few, NUREG-series publications; Federal Register notices; applicant, licensee, and vendor documents and correspondence; NRC correspondence and internal memoranda; bulletins and information notices; inspection and investigative reports; licensee event reports; and Commission papers and their attachments.

NRC publications in the NUREG series, NRC regulations, and *Title 10, Energy*, in the Code of *Federal Regulations* may also be purchased from one of these two sources.

- The Superintendent of Documents U.S. Government Printing Office Mail Stop SSOP Washington, DC 20402–0001 Internet: bookstore.gpo.gov Telephone: 202–512–1800 Fax: 202–512–2250

- The National Technical Information Service Springfield, VA 22161–0002 www.ntis.gov 1–800–553–6847 or, locally, 703–605–6000

A single copy of each NRC draft report for comment is available free, to the extent of supply, upon written request as follows:

Address: Office of the Chief Information Officer

Reproduction and Distribution Services Section U.S. Nuclear Regulatory Commission Washington, DC 20555–0001 E-mail: DISTRIBUTION@nrc.gov Facsimile: 301–415–2289

Some publications in the NUREG series that are posted at NRC's Web site address http://www.nrc.gov/reading-rm/doc-collections/nuregs are updated periodically and may differ from the last printed version. Although references to material found on a Web site bear the date the material was accessed, the material available on the date cited may subsequently be removed from the site.

#### Non-NRC Reference Material

Documents available from public and special technical libraries include all open literature items, such as books, journal articles, and transactions, *Federal Register* notices, Federal and State legislation, and congressional reports. Such documents as theses, dissertations, foreign reports and translations, and non-NRC conference proceedings may be purchased from their sponsoring organization.

Copies of industry codes and standards used in a substantive manner in the NRC regulatory process are maintained at-

The NRC Technical Library Two White Flint North 11545 Rockville Pike Rockville, MD 20852–2738

These standards are available in the library for reference use by the public. Codes and standards are usually copyrighted and may be purchased from the originating organization or, if they are American National Standards, from—

American National Standards Institute 11 West 42<sup>nd</sup> Street New York, NY 10036–8002 www.ansi.org

Legally binding regulatory requirements are stated only in laws; NRC regulations; licenses, including technical specifications; or orders, not in NUREG-series publications. The views expressed in contractor-prepared publications in this series are not necessarily those of the NRC.

The NUREG series comprises (1) technical and administrative reports and books prepared by the staff agency (NUREG-XXXX) contractors or (NUREG/CR-XXXX), (2) proceedings of conferences (NUREG/CP-XXXX), (3) reports resulting from international agreements (NUREG/IA-XXXX), (4) brochures (NUREG/BR-XXXX). and (5) compilations of legal decisions and orders of the Commission and Atomic and Safety Licensing Boards and of Directors' decisions under Section 2.206 of NRC's regulations (NUREG-0750).

212-642-4900

**DISCLAIMER:** This report was prepared as an account of work sponsored by an agency of the U.S. Government. Neither the U.S. Government nor any agency thereof, nor any employee, makes any warranty, expressed or implied, or assumes any legal liability or responsibility for any third party's use, or the results of such use, of any information, apparatus, product, or process disclosed in this publication, or represents that its use by such third party would not infringe privately owned rights.

# Review Guidelines for Field-Programmable Gate Arrays in Nuclear Power Plant Safety Systems

Manuscript Completed: October 2009

Date Published: February 2010

Prepared by M. Bobrek<sup>1</sup>, D. Bouldin<sup>2</sup>, D.E. Holcomb<sup>1</sup>, S.M. Killough<sup>1</sup> S.F. Smith<sup>1</sup>, C. Ward<sup>1</sup>, and R.T. Wood<sup>1</sup>

<sup>1</sup>Oak Ridge National Laboratory P.O. Box 2008 Oak Ridge, TN 37831-6010

<sup>2</sup>University of Tennessee 419 Ferris Hall, 1508 Middle Drive Knoxville, TN 37996-5483

M.E. Waterman, NRC Project Manager

NRC Job Code N6351

Office of Nuclear Regulatory Research

#### **ABSTRACT**

This report is a compilation of safe field-programmable gate array (FPGA) design practices that can be used by NRC staff as guidance for reviewing FPGA-based safety systems in nuclear power plants. It can also serve as a basis for development of specific activities that will support the licensing process such as FPGA-specific review procedures and acceptance criteria. The report follows on the investigation of existing regulatory documents and standards related to design and review of safety-related FPGA systems. Since the existing regulatory documents are not specific about FPGA design practices, this report also serves as the complement to the standards that cover general issues related to digital and software safety systems in nuclear power plants.

FPGA design practices are classified into three major groups—FPGA hardware design practices, FPGA design entry methods, and FPGA design methodologies. Within these major groups, design practices are further classified according to four top-level attributes—reliability, robustness, traceability, and maintainability according to the framework used in NUREG/CR-6463.

The report focuses on listing and describing FPGA design practices that are potentially unsafe as well as on suggesting which ones are acceptable for safety-critical designs. Additionally, the report outlines a design life cycle that could be used by the designers and the reviewers for FPGA-based safety systems.

• •

#### **FOREWORD**

Although field programmable gate arrays (FPGAs) (and complex programmable logic devices (CPLDs)) have not been used extensively in safety-related nuclear applications to date, it is highly likely that this technology will be used in safety systems submitted for NRC review in the foreseeable future.

A common misunderstanding about FPGAs (and CPLDs) is that these devices are less complex than microprocessor-based systems and therefore are inherently safer than microprocessor-based safety systems. FPGA devices are fundamentally complex software designs implemented by hardware engineers. As more functions are moved onto single integrated circuit (IC) chips, greater attention should be given to the system development process. Experience has shown that FPGA disciplined design methodologies have not progressed at the same rate as the capability to add functionality to FPGAs, implying that project managers may not fully appreciate the risk to safety. There also could be a perception that the process is improved by using automated design tools. In fact, there may be an overreliance on these design tools, as indicated by several projects in which problems were linked to improper use of the tools or unintended loss of redundancy arising from the tools optimizing the intended design into unintended functionality.

From a safety perspective, it is difficult to assess the correctness of FPGA devices without extensive documentation, tools, and review procedures. Therefore, several aspects of these technologies should be addressed during safety reviews. First, NRC reviewers should review vendor information about FPGA design processes, including software design tools and development methodologies (similar to that used for current software reviews). Second, NRC reviewers should consider specific device design information (over and above the system-level documentation) for the system under review, such as requirements and design specifications, data sheets, user manuals, programmer manuals, and so forth. Third, NRC reviewers should review device failure mode information, including mitigating fault tolerant designs (e.g., triple modular redundancy and concurrent cell error detection) and workaround design changes resulting from faults found too late in the design process to correct without extensive cost (a potential issue with third-party FPGA devices). Fourth, to ensure consistent reviews of FPGA safety systems, the NRC should acquire tools and review procedures (as well as corresponding training) to support staff evaluations of safety functions implemented in FPGAs.

The primary objective of the research described in this report was to develop comprehensive guidance the NRC staff could use to confirm that FPGA-based safety systems are in conformance with NRC regulations, including Title 10 of the Code of Federal Regulations, Part 50 (10CFR50), Appendix A, General Design Criteria for Nuclear Power Plants, Criterion 21, Protection system reliability and testability. Criterion 21 states, "The protection system shall be designed for high functional reliability and inservice testability commensurate with the safety functions to be performed. Redundancy and independence designed into the protection system shall be sufficient to assure that (1) no single failure results in loss of the protection function and (2) removal from service of any component or channel does not result in loss of the required minimum redundancy unless the acceptable reliability of operation of the protection system can be otherwise demonstrated. . . . ." The use of unsafe design practices could decrease the reliability of a safety system. Consequently, unsafe design practices should be identified during the development of the system by the vendor or licensee, and verified to be not in the system by the NRC reviewer during the licensing process.

Because the regulatory Offices are ultimately responsible for revising their standard review plans and interim staff guidance documents, the research is described in a NUREG-series report suitable for translating into regulatory guides and standard review plans. This report emphasizes the importance of a proactive approach to safety assessments of FPGA-based safety systems. The results of this work also could be used to develop NRC policy and regulations regarding acceptable FPGA design and application practices and procedures.

### **CONTENTS**

|     |                                                                    | Page       |

|-----|--------------------------------------------------------------------|------------|

| AB  | STRACT                                                             | iii        |

| FO  | REWORD                                                             | v          |

| LIS | ST OF FIGURES                                                      | ix         |

|     | ST OF TABLES                                                       |            |

|     | CRONYMS                                                            |            |

|     |                                                                    |            |

| 1.  | INTRODUCTION                                                       |            |

|     | 1.1 Background                                                     |            |

|     | 1.2 Document Organization                                          |            |

| 2.  | FPGA HARDWARE DESIGN PRACTICES                                     |            |

|     | 2.1 Reliability                                                    |            |

|     | 2.1.1 Board-Level Design Attributes                                |            |

|     | 2.1.2 FPGA Internal Logic Design Attributes                        |            |

|     | 2.2 Robustness 2.3 Traceability                                    |            |

|     | 2.4 Maintainability                                                | 11         |

| 2   | FPGA DESIGN ENTRY METHODS                                          |            |

| 3.  |                                                                    |            |

|     | 3.1 Reliability                                                    |            |

|     | 3.3 Traceability                                                   |            |

|     | 3.4 Maintainability                                                |            |

| 4.  | FPGA DESIGN METHODOLOGIES                                          |            |

| 4.  | 4.1 Design for Safety                                              |            |

|     | 4.1 Design for Safety  4.2 FPGA Selection                          |            |

|     | 4.3 Design Tool Selection                                          |            |

|     | 4.4 Design Flow                                                    |            |

|     | 4.4.1 Design Requirements                                          |            |

|     | 4.4.2 Architectural Design                                         |            |

|     | 4.4.3 Detailed Design                                              |            |

|     | 4.4.4 Design Review                                                |            |

|     | 4.4.5 Behavioral Description                                       |            |

|     | 4.4.6 Behavioral Simulation                                        |            |

|     | 4.4.7 Logic Synthesis                                              |            |

|     | 4.4.8 Logic-Level Simulation                                       |            |

|     | 4.4.9 Physical Implementation                                      |            |

|     | 4.4.10 Post-Layout Simulation                                      |            |

|     | 4.4.11 Prototype                                                   |            |

|     | 4.4.12 FPGA Verification                                           |            |

|     | 4.4.13 Hardware Implementation                                     |            |

| _   |                                                                    |            |

| 5.  |                                                                    |            |

| AP  | PENDIX A: SURVEY OF FIELD PROGRAMMABLE GATE ARRAY DESIGN           |            |

|     | AND EXPERIENCE RELEVANT TO NUCLEAR POWER PLANT APPLICATION         |            |

| AP  | PENDIX B: RESULTS OF SEARCH FOR TECHNICAL STANDARDS RELATED DESIGN | ED TO FPGA |

## LIST OF FIGURES

| Figure                | e                                                                         | Page         |

|-----------------------|---------------------------------------------------------------------------|--------------|

| 1                     | Metastability occurs at Q <sub>A</sub> and causes error at Q <sub>B</sub> | 6            |

| 2                     | Reset synchronizing circuit 1                                             | 7            |

| 3                     | Reset synchronizing circuit 2                                             |              |

| 4(a)                  | Three different time constraints                                          | 8            |

| <b>4</b> ( <i>b</i> ) | Single time constraint                                                    | 8            |

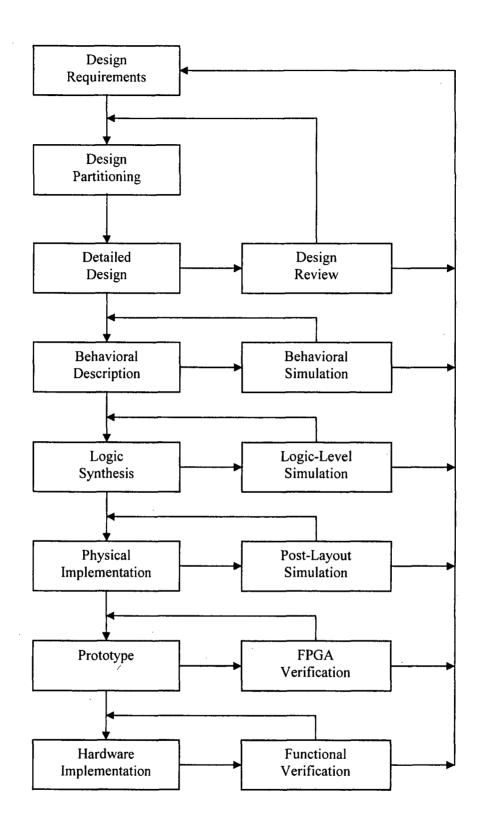

| 5                     | FPGA design flow                                                          | 47           |

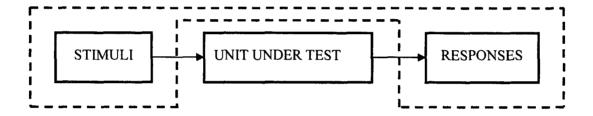

| 6                     | Testing procedure for each design step                                    | 51           |

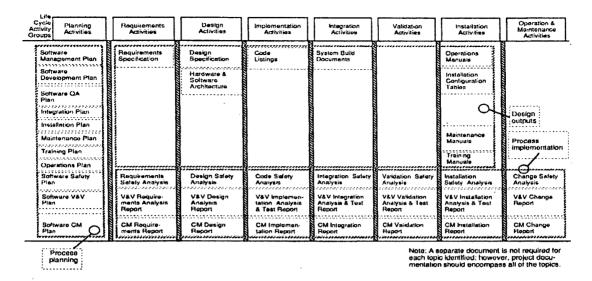

| A-1                   | Documents required throughout the software life cycle                     | A <b>-</b> 9 |

# LIST OF TABLES

| Tabl | le                       | Pag | e |

|------|--------------------------|-----|---|

| 1    | Recovery time for XC2VP4 | (   | 6 |

|   |   |  | • |   |  |

|---|---|--|---|---|--|

|   |   |  |   |   |  |

| • |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   | • |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   | • |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

|   |   |  |   |   |  |

#### **ACRONYMS**

ASIC application-specific integrated circuit

BIST built-in self-test

BRAM block random access memory

CPLD complex programmable logic device

DCM digital clock manager

EDA Electronic Design Automation EDAC error detection and correction

EDIF Electronic Design Interchange Format

ESA European Space Agency

ESD electrostatic discharge

ESF engineering safety feature

FIFO first-in-first-out

FMEA failure mode effects analysis FPGA field-programmable gate array

FTA fault tree analysis

HDL hardware description language I&C instrumentation and controls

IC integrated circuits

I/O input/output

IP intellectual property

II intercettal property

IV&V independent verification and validation

JTAG joint test action group

LUT lookup table

mil-spec military specifications

MSB most significant bit

MTBMO mean time between metastability occurrences

NASA National Aeronautics and Space Administration

NRC Nuclear Regulatory Commission

ORNL Oak Ridge National Laboratory

PC personal computer PCB printed circuit board

PGA pin grid array

PLD programmable logic device

PLL phase locked loop

PROM programmable read-only memory

radiation hardening rad-hard **RAM** random access memory read-only memory **ROM** RTL register transfer level quality assurance OA quad flat pack **QFP** SEE single-event effect single-event upset **SEU**

SRAM static random access memory

TDDB time-dependent dielectric breakdown

TID total ionizing dose

TMR triple-modular redundancy UVA University of Virginia

VHDL V&V

very high speed integrated circuits HDL verification and validation

#### 1. INTRODUCTION

Oak Ridge National Laboratory (ORNL) has been engaged by the U.S. Nuclear Regulatory Commission (NRC) Office of Nuclear Regulatory Research to develop the technical basis for assessing field-programmable gate array (FPGA) technology in safety-related systems within nuclear power plants. In particular, ORNL has investigated programmable digital logic technology and implementation practices to support development of review guidance. In the first part of this study, ORNL surveyed information on the use of FPGA technology for high-assurance applications. A finding of these surveys, along with a summary of particularly relevant programmable logic device standards, is given in Appendix A of this document. In the second part of the study, ORNL developed FPGA review guidance as a set of suitable design practices for safety-critical systems. Additionally, a FPGA-specific design life cycle is outlined including specific design steps and the corresponding verification steps. The term FPGA in this document refers to complex programmable logic devices (CPLDs) as well. When there is a safety-related issue specific only to CPLDs, then the term CPLD is specifically used.

Information for this report was obtained through publicly available sources such as published papers and presentations. No proprietary information is represented.

#### 1.1 Background

Existing regulatory documents for instrumentation and control systems in nuclear power plants are tailored for pre-FPGA technology including analog circuitry, discrete digital electronics, and microcontrollers. Additionally, a number of existing regulatory documents address safety issues related to software applications running on standard platforms such as personal computers (PCs) or embedded hardware platforms. Given the FPGA's dual nature as being both hardware and software, and its inherent complexity, there is a need for a FPGA-specific regulatory document that would address issues such as system safety assessment, design life cycle, verification and validation (V&V), configuration management, documentation requirements, etc. Many of the existing documents such as DO-254, IEEE 1012, IEEE 603, IEEE 7-4.3.2, and IEC 61508 address these issues in more general terms and, as such, may be used for the review of FPGA-based systems. However, FPGA-specific areas that are not sufficiently addressed in any of the existing documents should be addressed in a separate FPGA review guidance document. Some of these areas include FPGA hardware design practices, FPGA design entry methods, and FPGA design tools.

The main issue in achieving sufficiently comprehensive guidance arises from the need to tailor the design life cycle and V&V process to account for the specific characteristics of FPGAs. Even a relatively simple FPGA design in most cases prohibits 100% testing during code simulation and hardware verification. Therefore, FPGA-based safety systems need to be treated as complex systems as defined in DO-254, Section 1.6, and a suitable design cycle including the V&V process is needed for FPGA-based safety-related designs. The V&V process may also include design tool verification, such as that established in IEEE 7-4.3.2. Also, comprehensive guidance should include specific FPGA design practices that will lead to readable, traceable, and verifiable designs. Some of these practices should include using combinatorial design only, partitioning the design to verifiable pieces, redundancy, error reporting, etc.

#### 1.2 Document Organization

The review guidance document contains acceptable design practices and V&V procedures that will improve the safety of FPGA designs. These practices are divided into three chapters: (1) FPGA Hardware Design Practices, (2) FPGA Design Entry Methods, and (3) FPGA Design Methodologies. This document

adopted the framework of NUREG/CR-6463 where the acceptable practices are organized in a three-level hierarchy. Only the top-level attributes are exactly the same as those in NUREG/CR-6463, while the lower-level attributes are specific to FPGA design practices. The four top-level attributes used throughout this document are reliability, robustness, traceability, and maintainability.

In Chapter2, the FPGA hardware design practices are divided into two groups: the board-level design practices and FPGA internal logic design practices. The board-level design practices deal with issues related to FPGA placement on the printed circuit board (PCB) and issues related to FPGA interfaces to other circuitry residing on the same board. The internal logic design practices include general digital design safe practices as well as FPGA-specific design practices.

The Chapter 3 covers safety design issues related to design entry methods based on VHDL and Verilog, the most commonly used Hardware Description Languages (HDLs). The safe coding practices are listed as base-level attributes grouped into the four top-level attributes. The base-level attributes are accompanied by examples in both HDLs to show preferable coding practices that should produce reviewable, traceable, and verifiable codes. Some of the base-level attributes indicate potentially unsafe coding practices and suggest appropriate coding examples. The others present a preferred way to code common digital blocks such as state machines, encoders, decoders, shift registers, counters, read only memories, random access memories, and FIFO memories to help the safety evaluation review.

In Chapter 4, a FPGA-specific design life cycle is described, and an appropriate design flow through the life cycle is established. In most cases, FPGA designs are complex to the level that makes the 100% testability too costly and time consuming. The proposed design life cycle including the V&V process should be used as a substitute for 100% testability. Also in Chapter 4, the design life cycle includes a number of sequential design steps accompanied with their corresponding V&V steps. Every step is described in detail and necessary output documentation is specified.

Appendix A summarizes the survey of FPGA design guides and experience relevant to nuclear power plant applications.

#### 2. FPGA HARDWARE DESIGN PRACTICES

This chapter discusses the safety-critical issues related to the hardware of FPGA design safety-related systems. It includes both the board-level design issues and the FPGA internal logic design issues. This chapter is organized into four sections, each addressing one of the top-level attributes.

#### 2.1 Reliability

FPGA hardware design reliability is the ability of a system or component to perform its required safety and non-safety functions under stated conditions for a specified period of time. The base-level attributes for reliability are divided into two groups—board-level design attributes and FPGA internal logic design attributes.

#### 2.1.1 Board-Level Design Attributes

The following base-level attributes facilitates the board-level reliability of FPGA designs:

- FPGA Power-Up

- FPGA Configuration Time

- Input/Output Standards

- Power Pin Decoupling

- Simultaneous Switching Outputs

- Output Slew Rate

- Output Current Drive

- Unused I/O Pins

- External Reset

- Ground and Power Planes

- Power Dissipation/Consumption

- Clock Traces

- FPGA Programming Pins

- Printed-Circuit-Board Layer Stacking

#### FPGA Power-Up

Most FPGAs use multiple power supplies, at least one for the FPGA core and one for the input/output (I/O) buffers. In addition, some FPGAs use separate reference voltage supplies for differential I/O buffers. Proper power sequencing is required in some of FPGAs to avoid an unpredictable behavior of the input and output buffers during power-up and power-down. Additionally, most FPGAs have power ramp-up timing requirements which set the upper and the lower limit of the power ramp time.

An additional issue is the startup current which in some cases can exceed the operational current. Care should be taken to implement voltage regulators that can support excess currents during the power-up.

#### **FPGA Configuration Time**

After power-up, reconfigurable FPGAs are configured from an internal or an external memory which can take up to several hundreds of microseconds depending on the FPGA size and the configuration clock. Care should be taken to prevent transient behavior of the external circuitry driven by the FPGA

during the configuration time. Appropriate measures include keeping the interfacing circuitry disabled during the configuration time or pulling up or down the critical inputs of the interfacing circuitry.

#### Input/Output Standards

FPGA outputs and inputs can be configured for different input/output (I/O) standards. It is essential that these standards are compatible with the I/O requirements of the external circuitry connected to the FPGA.

#### Power Pin Decoupling

Due to a simultaneous switching of a large number of gates in an FPGA, the supply current has a shape of periodic spikes which can cause spike-like voltage bounces at the ground pins. To reduce the ground bounce and the digital noise, every power pin should be decoupled using decoupling capacitors. Some of the FPGAs have their decoupling capacitors built in.

#### Simultaneous Switching Outputs

FPGA outputs that transition at the same time should be distributed across the FPGA output pins so that the simultaneous switching output requirement satisfies the FPGA technical specifications.

#### **Output Slew Rate**

To reduce the digital noise due to the output switching, the slew rate of the FPGA output pins should be set to the minimum value defined in the FPGA technical specifications. The use of high-slew-rate outputs should be limited to the case where the fast output switching is essential for proper FPGA interfacing.

#### **Output Current Drive**

Most of the FPGAs have a selectable current drive at the output pins. To reduce the digital noise due to the output switching, the current drive of the FPGA output pins should be set to the minimum value unless a higher current drive is needed for proper FPGA interfacing.

#### Unused I/O Pins

To reduce the power dissipation, the unused I/O pins should be properly programmed or tied to the ground or the power, depending on the particular FPGA I/O specifications. All unused differential I/Os should be configured as single-ended to save the power used by the differential I/O bias circuitry.

#### External Reset

If an external reset signal is provided to an FPGA, it should be bounce-free and have a sufficiently fast transition between the logic levels. Since different FPGAs may require different rise times at their inputs; the use of a dedicated reset integrated circuit (IC) is suggested.

#### Ground and Power Planes

The analog and the digital parts of the design residing on the same board should be physically separated to reduce injection of the digital noise into the analog signals. Also, separate power supplies and separate ground and power planes should be used. The analog and the digital ground planes should be connected in a single point to reduce the current loops in the planes.

#### Power Dissipation/Consumption

The timing behavior of the FPGA is guaranteed by the design tools only for a given junction temperature range. The power dissipation of the FPGA should be estimated and later measured to see if additional cooling is needed to keep the junction temperature within the required range.

#### **Clock Traces**

Long signal lines, if not properly terminated, can cause reflections and crosstalk. This is especially important for the clock and other high-speed lines that should be terminated at the source and/or the end of the line using serial and/or parallel termination networks.

#### **FPGA Programming Pins**

FPGA programming pins, such as joint test action group (JTAG) pins, may be subject to noise if not pulled up or down by resistors. This noise can either alter or erase the configuration memory. Also, FPGAs with external configuration memory require specific rules for the layout of the connections between the external configuration memory and the FPGA programming pins. To prevent accidental or malicious reconfiguration of CPLDs or external configuration programmable read-only memories (PROMs), the configuration memory should be write-protected by using write security bits. Malicious reconfigurations should be prevented by design and/or by administrative controls. For example, the FPGA design can include error detection circuitry or built-in self test (BIST) to constantly monitor the health of the FPGA system. Making JTAG connector physically accessible only to the trusted personnel may be one of the administrative measures.

#### Printed-Circuit-Board Layer Stacking

To ensure a high integrity of the FPGA board design, the stacking of the board layers is critical. Preferred layout-stacking alternates the signal layers and the power/ground layers. Below are shown two examples of a preferred 8-layer PCB stacking.

| Signal | Signal/Power |

|--------|--------------|

| Ground | Ground       |

| Signal | Signal/Power |

| Power  | Ground       |

| Ground | Power        |

| Signal | Signal/Power |

| Ground | Power        |

| Signal | Signal/Power |

#### 2.1.2 FPGA Internal Logic Design Attributes

This section discusses the following base attributes that facilitate the predictability of the FPGA internal logic design:

- Asynchronous Design

- Metastability

- Internal FPGA Reset

- Phase Locked Loop Locking Time

- Timing Constraints

- State Machines

- Multiple Clock Domains

- Latches

- High Fan-out Lines

#### Asynchronous Design

The FPGA design should be synchronous as much as possible. Asynchronous designs are prone to glitches, bus skews, and other timing issues. Furthermore, the FPGA design tools do not generally support asynchronous timing constraint and analysis. If asynchronous designs are used for 100% testability or any other reason, appropriate measures need to be taken to make sure that the output glitches and the bus skews are not affecting safe operation of the FPGA design. These measures may include use of registered I/Os or analog filtering of the FPGA outputs.

#### Metastability

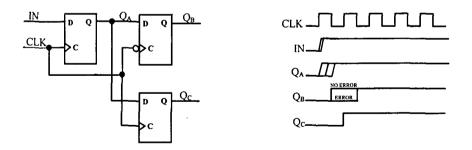

Metastability can occur when an asynchronous input gets clocked within the FPGA, and it is expressed as an undetermined state at the output of a flip-flop (Figure 1). The undetermined state resolves itself after the *recovery time*, which is on the order of several ns to several tens of ns for most of FPGAs. Table 1 shows the recovery times and their corresponding mean times between metastability occurrences (MTBMO) for XC2VP4 FPGA from Xilinx. For example, metastability with a recovery time of 1ns occurs on average every microsecond while the metastability with a 3 ns recovery time is extremely rare. The FPGA designer should consider the recovery time when determining the maximum clock speed of the design.

Figure 1. Metastability occurs at QA and causes error at QB.

Table 1. Recovery time for XC2VP4

| Recovery time | 1 ns | 1.8 ns | 2.1 ns | 2.4 ns      | 2.7 ns          |

|---------------|------|--------|--------|-------------|-----------------|

| MTBMO         | 1 us | 1 day  | 1 year | 1,000 years | 1,000,000 years |

#### Internal FPGA Reset

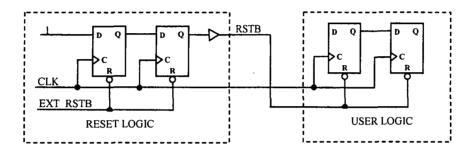

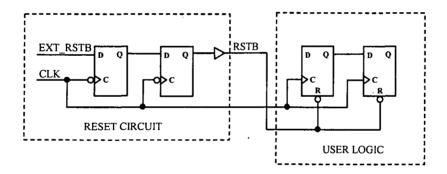

Usually, all flip-flops in FPGAs are cleared after the power-up unless specified differently by the designer, in which case a dedicated synchronous/asynchronous reset network controlled by the reset logic inside the FPGA is used. Care should be taken to ensure synchronous reset of all flip-flops across the FPGA. This is especially critical when an asynchronous reset signal is used to clear counters or state machines that need to run synchronously. Figures 2 and 3 show two different methods for synchronizing an asynchronous reset line to ensure reset of all flip-flops within the same clock period. The approach in Figure 3 assumes that the clock period is greater than the resolution time for the flip-flops as well as skews on the reset network are less than half of the clock period. Both of these requirements are easily satisfied in modern FPGAs, since most FPGAs have dedicated low-skew lines for the reset signal and use low-resolution time flip-flops.

Figure 2. Reset synchronizing circuit 1.

Figure 3. Reset synchronizing circuit 2.

#### Phase Locked Loop Locking Time

The Phase Locked Loops (PLL) inside FPGAs may be used to generate synchronous clocks or to fine-control signal delays. They require an additional time to lock after the FPGA power-up. The user logic should monitor the PLL lock signal, which indicates when the signals coming from the PLL are valid.

#### **Timing Constraints**

Most of FPGA design tools base their timing constraints and analysis on synchronous design. The timing constrains include the period, the pad-to-clock delay, the clock-to-pad delay, the skew, and the from-to delay.

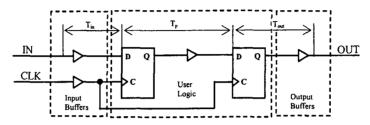

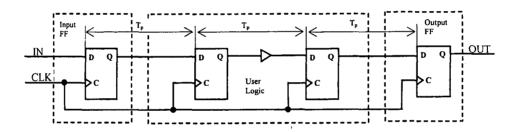

Appropriate timing constrains are critical in high-speed and safety-related FPGA designs. Due to different FPGA architectures and design tools, it is important to standardize and simplify the way the timing constraints are assigned and verified. As Figure 4(a) shows, one should specify three different timing parameters to ensure proper FPGA performance at the required clock speed (T<sub>in</sub>, T<sub>p</sub>, and T<sub>out</sub>). By using registered I/O buffers, one can reduce the number of timing constraints to one as shown in Figure 4(b).

Another critical timing issue is the maximum delay and/or maximum skew on high-fan signals such as RESET and EN. Designers should ensure that the maximum delay on these lines is less than the clock period to ensure the resetting and/or enabling of all flip-flops in the design occur within the same clock period.

Figure 4(a). Three different time constraints.

Figure 4(b). Single time constraint.

#### State Machines

Behavior of a state machine should be defined not only for the used states but also for the unused states. Most synthesis tools will ignore unused states and synthesize a state machine that can become stuck in an undefined state after entering it unexpectedly. A similar situation occurs if a state in the state machine is not defined for all possible combinations of its inputs. Therefore, all states and state transitions in a state machine should be explicitly defined.

#### Multiple Clock Domains

When designing the interface between clock islands that use different synchronous or asynchronous clocks, one should use double registers for edge-sensitive transfers to mitigate the occurrence of metastability.

#### Latches

Even though latches use fewer gates than conventional flip-flops, special care should be taken when the use of latches is necessary as the noise occurring at the latch inputs may propagate to the latch outputs. Use of flip-flops eliminates this problem.

#### High Fan-Out Lines

FPGAs have dedicated high-speed routing lines for clocks and other high fan-out signals such as RESET or EN. However, it is the designer's responsibility to properly assign these lines using the FPGA design tools. Also, the designer should impose necessary timing constraints with enough margin to ensure proper functioning of the FPGA in extreme environmental conditions.

#### 2.2 Robustness

Robustness refers to the capability of an FPGA-based safety system to operate in an acceptable manner under abnormal conditions or events over the entire lifetime of the system. The following are the base-level attributes relevant to robustness of the hardware design of FPGA-based safety-critical systems:

- Timing Performance

- Single-Event Upsets (SEU)

- Configuration Data Retention

- Program/Erase Cycles

- Lead-Based Soldering

#### **Timing Performance**

Appropriate timing constraints with sufficient margin should be set by the designer during the synthesis and/or place and route process to ensure correct functioning of the time-critical paths of the FPGA design. The timing reports should be checked after the implementation of the design to ensure the constraints are satisfied and that there is enough margin in the timing performance.

#### Single Event Upsets

Single-event upsets (SEU) can affect both the FPGA logic as well as the FPGA configuration memory. Even in a radiologically benign environment, cosmic rays and alpha particles from the FPGA packaging material can produce enough charge inside an FPGA to change a state in one or more flip-flops or memory cells. Occurrence of SEUs over the entire lifetime of the FPGA system could be significant enough to require protective measures during the design as well as use of the system. These measures can be divided into two groups—the measures to mitigate SEUs in the user logic and the measures to mitigate SEUs in the configuration memory. The following are the possible measures to mitigate SEUs in the user logic:

- Redundancy in the design to ensure detection and/or correction of a SEU

- Error detection and correction (EDAC) for setpoints and memory data

- Error detection and/or correction in state machines and control logic

- Using SEU-immune or SEU-tolerant FPGAs

- Periodic resetting of the FPGA logic

- Watchdog timers

Measures to protect the FPGA configuration from an SEU are as follows:

- Using one-time programmable FPGAs

- Selecting the flash-based over the static random access memory (SRAM)-based reconfigurable FPGAs

- Run-time checking of the configuration memory

- Scheduled and error-initiated reloading of the FPGA configuration memory.

#### Configuration Data Retention

Configuration data retention for CPLDs, flash-based FPGAs, and programming devices used to configure SRAM-based FPGAs can be from less than 10 years to more than 20 years. During the operation period of an FPGA system, the programming data should be stored on a separate high-reliability memory media and then periodically used to refresh the configuration memory in the FPGAs/CPLDs. For one-time programmable FPGAs the concern is the self healing of the configured interconnects. The data sheets and reliability reports for one-time programmable FPGAs needs to be checked to determine the life time of the programmed interconnects.

#### Program/Erase Cycles

The program/erase cycles for the configuration memories are limited, ranging from several thousands to several tens of thousands. A log file regarding the number of program/erase cycles should be established to ensure there are enough program/erase cycles remaining in the FPGA throughout the entire life-cycle of the system.

#### Lead-Based Soldering

Growth of tin whiskers over time is especially critical for FPGAs due to the high pin count and the small pitch of the Pin Grid Array (PGA) and Quad Flat Pack (QFP) packages. Avoiding the use of lead-free tin parts and PCBs is an administrative control measure to eliminate failures due to whisker growth. Design techniques that include error detection and built-in self test can be an alternative solution.

#### 2.3 Traceability

Traceability refers to attributes of a safety-critical FPGA design that support V&V of the design throughout the development design life cycle as well as the safety evaluation review during the licensing process. The traceability attributes cover issues such as use of predefined vendor- or tool-specific macros, use of nonstandard HDL libraries, implementing a hierarchical design, using version control tools, using a particular design style, and the design documentation. These attributes are more applicable to the Design Entry Methods and the Design Methodology that are described in separate chapters. The following are the traceability attributes that apply to the Hardware Design Practices:

- Board-Level Design Documentation

- FPGA Internal Logic Design Documentation

#### **Board-Level Design Documentation**

The documentation that is critical for the traceability of the FPGA board-level design includes PCB schematics, mechanical PCB drawings, board layout design files, bills of material, and the data sheets for the parts used on the board. This documentation should be included in the licensee/vendor design report to facilitate the review of the reliability and the robustness of the board-level design including FPGA power-up, external FPGA interfacing, external FPGA reset, power pin decoupling, unused I/O pins, PCB layer stacking, and other features described in this guidance.

#### FPGA Internal Logic Design Documentation

The documentation necessary to verify and review the FPGA internal logic design includes FPGA design files, FPGA data sheets, pin out and package information, application notes, and white papers. This documentation should be included in the licensee/vendor design report to facilitate the review of the FPGA internal logic design including FPGA configuration start-up, simultaneous switching outputs,

output slew rate, output current drive, FPGA power dissipation, metastability, timing constraints, state machines, high fan-out lines, and other features described in this guidance.

#### 2.4 Maintainability

Maintainability of FPGA-based safety systems relates to attributes that facilitate the maintenance of a system during the operation period. The maintainability attributes address issues such as PCB design for maintainability, FPGA configuration maintainability, and FPGA design tool maintainability. The following are the base attributes relevant to maintainability of FPGA-based safety-related designs:

- Modular Design

- Standardized PCB Format

- Test Points and Indicators

- Reprogrammability

- FPGA Selection

#### Modular Design

To facilitate maintenance of FPGA-based designs, designs should be modular as much as possible (i.e., well-defined functions such as high-pressure trip, low-pressure trip, and high-flux trip) should be implemented on separate PCBs. Placing multiple FPGAs on a single board can complicate maintenance processes as well as unnecessarily challenge the safety system due to a faulty power supply for the board or due to mechanical failure of the PCB, for example.

#### Standardized PCB Format

FPGA-based PCBs should use one of the board standard formats where the size, the back plane connectivity, and the power supply are predefined to fit one of the hardware platform standards such as VME ANSI/IEEE 1014-1987, PCI, PCI-X, PC/104 IEEE P966.1, etc.

#### Test Points and Indicators

FPGA-based designs should include a number of test points and indicators for quick board diagnostic and for health monitoring of the board. These test points may include power supplies, clock sources, critical signals, temperature sensors, circuit aging sensors, etc. BIST logic for health monitoring can be placed inside the FPGA to monitor entire functions such as bus activity, occurrence of erroneous data, and time-out circuits.

#### Reprogrammability

FPGA-based PC boards should have provisions for reprogramming of the FPGA during the entire equipment design life. These provisions include physical access to the FPGA programming pins, necessary software and hardware tools for the programming of a particular FPGA, and the configuration files stored on a secure long-term storage media.

#### **FPGA Selection**

Selection of the vendor and the type of the FPGAs used in a design should be driven by maintainability of the system as well. The leading FPGA vendors with long-term presence on the FPGA market that support their legacy parts and the design tools should be considered. Furthermore, the backward compatibility of the design tools may not always be guaranteed by some vendors, which would

require the end user to store and maintain the version of the tool used during the initial design of the system.

#### 3. FPGA DESIGN ENTRY METHODS

This chapter discusses the safety-critical issues related to very high speed integrated circuits HDL (VHDL) and Verilog, the most commonly used hardware description languages for FPGA designs. The schematic entry is still used for mainstream FPGA designs, and it is recommended for safety-critical designs as well. Using the schematic entry, the designer creates the gate-level representation of the design requirements that is otherwise done by the synthesis tool in the case of HDL design entry. While it gives the designer more control over the design process, the schematic entry is more time consuming and is expected to be replaced by HDL design over time.

The following sections discuss design practices that can lead to unreliable FPGA design, and therefore should be avoided. Also, proper design practices are suggested, and corresponding code examples are given for both design languages (i.e., VHDL and Verilog). The examples cover the most commonly used HDL structures such as state machines, multiplexers, decoders, read-only memory (ROM), random access memory (RAM), first-in-first-out (FIFO) memory, etc. This chapter is organized into four sections, each addressing one of the top-level attributes.

#### 3.1 Reliability

The reliability of FPGA design entry methods is the ability of the method to capture the design requirements and to translate the requirements into the FPGA logic. A reliable HDL code gives an exact textual representation of the design requirements and provides unambiguous instructions to the logic synthesis tool. These goals cannot be completely achieved during the design entry phase of the development cycle since VHDL and Verilog are not formal languages. Therefore, the development life cycle for an FPGA-based, safety-critical system needs to include verification steps following the synthesis, place and route, configuration, and hardware implementation. The following are the base-level attributes relevant to reliability of FPGA design entry methods:

- Mixed Language Design

- Nonsynthesizable Code

- Port Data Types

- Sensitivity List

- Implementing Resets

- Implementing Latches

- Multiple-Clock Domains

- If and Case Statements

- Multiplexers/Encoders

- De-multiplexers/Decoders

- Comparators

- Adder Trees

- Arithmetic Overflow

- Binary Scaling

- Counters

- Shift Registers

- ROM Design

- RAM Design

- FIFO Design

- State Machines

#### Mixed Language Design

Even though the mixed language designs are supported by most of design tools, using different languages to code different blocks in the same design should be avoided due to potential language incompatibility and different synthesis rules. However, different languages can be used to design redundant identical blocks, redundant FPGAs, or redundant boards to provide additional diversity.

#### Nonsynthesizable Code

Nonsynthesizable code does not get materialized into the logic by the synthesizers. It is used only for simulation and it should reside in simulation-only files or test benches. The design files should contain synthesizable code only. Mixing synthesizable and nonsynthesizable code reduces readability of the code and increases probability of errors. Typical examples of nonsynthesizable codes include wait, after, and assign statements as shown below:

```

--VHDL //Verilog

wait for 10 ns; # 10;

Q <= '0' after 20 ns; assign #20 Q=0;

```

#### Port Data Types

Use std\_logic and std\_logic\_vector in VHDL code for port declaration to avoid restrictions that may apply to other data types. For example, using buffer type is convenient because it allows internal use of an output port, but it can cause errors during synthesis. Arrays in port declarations in VHDL should be avoided as well because of the inability of VHDL to represent and store array ports in the netlists such as Electronic Design Interchange Format (EDIF). Furthermore, the array ports can create incorrect correlation of the placed pin names from the names used in the port declaration. The following example shows the buffer port declaration.

```

entity acc_RAM is

port (CLK : in std_logic;

DIN : in std_logic_vector(7 downto 0);

DOUT : buffer std_logic_vector(7 downto 0));

end acc_RAM;

architecture behavioral of acc_RAM is begin

process (CLK)

begin

if CLK'event and CLK = '1' then

DOUT <= DOUT + DIN;

end if;

end process;

end behavioral;

```

#### Sensitivity List

While using the **process** statement in VHDL or the **always** statement in Verilog, the sensitivity list should be completely specified. Some of the synthesis tools may assume the presence of signals in the sensitivity list even when these signals are omitted from the list. Synthesis tools need to be unambiguously directed by the HDL code to avoid unpredictable outputs of the synthesis process.

#### Implementing Resets

Resets should be synchronous unless the reset signal comes from a different clock region or is an external signal. In that case, the asynchronous reset signal should be resynchronized to avoid metastability when the reset is released. Since the synchronous reset can be executed only in the presence of the clock, asynchronous reset should be used in the case where the clock is not running continuously. The examples below show the synchronous reset code, the asynchronous reset code, and two different reset synchronizer codes that are HDL versions of the reset synchronizers from Figures 2 and 3.

```

--VHDL synchronous reset

//Verilog synchronous reset

process (CLK)

always @ (posedge CLK)

begin

begin

if CLK'event and CLK = '1' then

if (RST)

if RST = '1' then

O = 1'b0;

Q \le '0';

else

else

Q = D;

Q \leq D;

end

end if:

end if:

end process;

--VHDL asynchronous reset

//Verilog asynchronous reset

process (CLK,RST)

always @ (posedge CLK or posedge RST)

begin

begin

if RST = '1' then

if (RST)

O <= '0';

Q = 1'b0;

elsif CLK'event and CLK = '1' then

else

Q \leq D:

Q = D;

end if:

end

end process;

```

```

--VHDL reset synchronizer I

//Verilog reset synchronizer1

process (CLK)

always @ (posedge CLK)

begin

begin

if CLK'event and CLK = '1' then

RST1 = RST EXT;

RST1 <= RST_EXT;

RST = RST1:

RST \leq RST1;

end if:

end process;

//Verilog reset synchronizer2

--VHDL reset synchronizer2

always @ (posedge CLK or posedge RST_EXT)

process (CLK, RST EXT)

begin

begin

if (RST EXT) begin

if RST EXT = '1' then

RST1 = 1'b1;

RST1 <= '1':

RST = 1'b1;

RST<= '1':

end

elsif CLK'event and CLK = '1' then

else begin

RST1 \le '0';

RST1 = 1'b0;

RST <= RST1:

RST = RST1;

end if:

end

end process;

end

```

#### Implementing Latches

Latches should be avoided in safety-critical FPGA designs because of difficult timing analysis and their transparence to glitches. However, latches can be unintentionally generated by ambiguous HDL statements intended to generate flip-flops. Most often, the latches are generated by incomplete if statements or by missing clock edges in the sensitivity list. Examples below show a correct latch implementation.

#### Multiple-Clock Domains

Multiple-clock domains in designs of safety-critical systems should be generally avoided due to difficult verification of the interface between the clock domains. If the multiple-clock domains are absolutely necessary for the proper functionality of the design, then double-registered interfacing between the clock domains should be implemented. Single-bit interfaces are relatively straightforward to design and verify, but transfer of the parallel data may be difficult to design and verify properly. Therefore, a thorough analysis of the interface should be performed to estimate the probability of occurrence of long metastability resolution times, their impact on design behavior, and necessary mitigation techniques that need to be implemented.

#### If and Case Statements

If and case statements may be used to design purely combinatorial logic such as multiplexers, encoders, de-multiplexers, and decoders as well as sequential logic such as state machines. When using ifelsif or case statements, all the branches should be defined explicitly for all possible input combinations. Also, all the outputs should be defined for every branch. If priority is not needed, use case statements instead of if statements to minimize the logic created by synthesis tools. Failing to completely define if or case statements can cause some synthesis tools to insert latches that are difficult to simulate. Examples related to if and else statements are given in the following two sections.

#### Multiplexers/Encoders

All possible multiplexer or encoder branches should be explicitly defined to avoid the possibility of creating latches and to improve the readability of the code. Case statements should be used if priority is not required. Below are the examples of **if**- and **case**-based multiplexers and encoders.

```

//Verilog 4-to-1 priority mux

--VHDL 4-to-1 priority mux

always @ (RST or SEL or IN1 or IN2 or IN3 or IN4)

process (RST,SEL,IN1,IN2,IN3,IN4)

begin

begin

if (RST == 1'b1) O = 1'b0; //reset

if RST = '1' then O <= '0': -- reset

elsif SEL = "00" then O \le IN1:

else if (SEL == 2'b00) O = IN1;

elsif SEL = "01" then O \le IN2;

else if (SEL == 2'b01) O = IN2;

else if (SEL == 2'b10) O = IN3;

elsif SEL = "10" then O <= IN3;

else O = IN4:

else O \le IN4;

end if:

end process;

--VHDL 4-to-1 mux using case statement

//Verilog 4-to-1 mux using case statement

process (SEL,IN1,IN2,IN3,IN4)

always @ (SEL or IN1 or IN2 or IN3 or IN4)

begin

begin

case SEL is

case (SEL)

when "00" \Rightarrow O \le IN1:

2'b00 : O = IN1;

when "01" => O \le IN2;

2'b01 : O = IN2;

when "10" => O <= IN3;

2'b10 : O = IN3;

when others \Rightarrow O \iff IN4;

2'b11 : O = IN4;

end case;

endcase

end process;

end

//Verilog 4-to-2 priority encoder

--VHDL 4-to-2 priority encoder

always @ (RST or IN1)

process (RST,IN1)

begin

begin

if (RST == 1'b1) O = 2'b00;

if RST = '1' then O \le "00";

else if (IN1 == 4'b0001) O = 2'b00;

elsif IN1 = "0000" then O \le 000":

else if (IN1 == 4'b0010) O = 2'b01;

elsif IN1 = "0010" then O \le 01";

else if (IN1 == 4'b0100) O = 2'b10;

elsif IN1 = "0100" then O <= "10";

else if (IN1 == 4'b1000) O = 2'b11;

elsif IN1 = "1000" then O <= "11";

else O = 2'b00;

else O <= "00":

end

end if;

```

```

--VHDL 4-to-2 encoder using case statement

//Verilog 4-to-2 encoder using case statement

process (IN1)

always @ (IN1)

begin

begin

case IN1 is

case (IN1)

when "0001" => O <= "00";

4'b0001 : O = 2'b00;

when "0010" => O <= "01":

4'b0010 : O = 2'b01;

when "0100" \Rightarrow O \Leftarrow "10":

4'b0100 : O = 2'b10;

when "1000" => O <= "11":

4'b1000 : O = 2'b11;

when others \Rightarrow O <= "00";

default : O = 2'b00;

end case:

endcase

end process;

end

```

#### De-multiplexers/Decoders

All possible de-multiplexer or decoder branches should be explicitly defined to avoid the possibility of creating latches and to improve the readability of the code. The **case** statement should be used if priority is not required. Below are the examples of **if-** and **case**-based de-multiplexers and decoders.

```

--VHDL 1-to-4 priority demux

//Verilog 1-to-4 priority demux

always @ (RST or SEL or IN1)

process (RST,SEL,IN1)

begin

begin

if (RST == 1'b1) O = 4'b0000; -//reset

if RST = '1' then O <= "0000"; -- reset

elsif SEL = "00" then O \le "000" \& IN1;

else if (SEL == 2'b00) O = {3'b000,IN1};

else if (SEL == 2'b01) O = {2'b00,IN1,1'b0};

elsif SEL = "01" then O \le "00" \& IN1 \& '0';

elsif SEL = "10" then O \le '0' \& IN1 \& "00";

else if (SEL == 2'b10) O = {1'b0,IN1,2'b00};

else O = \{IN1,3'b000\};

else O \le IN1\&"000";

end if:

end process;

--VHDL1-to-4 demux using case statement

//Verilog 1-to-4 demux using case statement

process (SEL,IN1)

always @ (SEL or IN1)

begin

begin

case SEL is

case (SEL)

when "00" => O <= "000"&IN1;

2'b00 : O = {3'b000,IN1};

when "01" \Rightarrow O \leq "00"&IN1&'0';

2'b01 : O = \{2'b00,IN1,1'b0\};

when "10" => O <= '0'&IN1&"00";

2'b10 : O = \{1'b0,IN1,2'b00\};

when others \Rightarrow O \leq IN1&"000";

2'b11 : O = {IN1,3'b000};

end case:

endcase

end process;

end

```

```

--VHDL 2-to-4 priority decoder

//Verilog 2-to-4 priority decoder

process (RST,IN1)

always @ (RST or IN1)

begin

begin

if RST = '1' then O \le "0000"; -- reset

if (RST == 1'b1) O = 4'b0000; // reset

elsif IN1 = "00" then O <= "0111":

else if (IN1 == 2'b00) O = 4'b0111;

elsif IN1 = "01" then O \le 0.0110";

else if (IN1 == 2'b01) O = 4'b0110;

elsif IN1 = "10" then O \le "1100";

else if (IN1 == 2'b10) O = 4'b1100;

else O <= "1110";

else O = 4'b1110;

end if:

end

end process:

--VHDL 2-to-4 decoder using case statement

//Verilog 2-to-4 encoder using case statement

process (IN1)

always @ (IN1)

begin

begin

case IN1 is

case (IN1)

when "00" \Rightarrow O \leq "0111";

2'b00 : O = 4'b0111;

when "01" \Rightarrow O <= "0110";

2'b01 : O = 4'b0110;

when "10" => 0 \le 1100":

2'b10 : O = 4'b1100;

when others => 0 <= "1110":

2'b11 : O = 4'b1110;

end case;

endcase

end process:

end

```

#### Comparators

Before using the greater than (>) or less than (<) statement, the designer should be aware of the format of the numbers being compared. As the example below shows, the result of the comparison depends on whether the numbers are signed or unsigned.

```

--VHDL compare statement

O <= '1' when A > X"00" else '0';

assign O = (A > 8'h00) ? 1'b1 : 1'b0;

-- if A = X"F0" is signed, O equals '0'

-- if A = X"F0" is unsigned, O equals '1'

// if A = 8'hF0 is unsigned, O equals 1'b1

```

#### Adder Trees

Addition of multiple numbers should be implemented as a synchronous cascade of two-number adders to avoid different synthesis implementations and to improve timing performance. Also, care should be taken to properly size the data path to avoid overflows in the addition tree. Below are examples of five-number adder trees.

--VHDL pipelined adder tree with 5 inputs and 3-cycle latency

```

process (CLK)

begin

if CLK'event and CLK = '1' then

LEVEL ONE SUM1 <= IN1 + IN2;

LEVEL ONE SUM2 <= IN3 + IN4;

LEVEL ONE SUM3 <= IN5;

LEVEL TWO SUM1 <= LEVEL ONE SUM1 + LEVEL ONE SUM2;

LEVEL TWO SUM2 <= LEVEL ONE SUM3;

FINAL SUM <= LEVEL TWO SUM1 + LEVEL_TWO_SUM2;

end if;

end process;

//Verilog pipelined adder tree with 5 inputs and 3-cycle latency

always @ (posedge CLK)

begin

FINAL SUM = LEVEL TWO SUM1 + LEVEL_TWO_SUM2;

LEVEL TWO SUM1 = LEVEL ONE SUM1 + LEVEL ONE SUM2;

LEVEL TWO SUM2 = LEVEL ONE SUM3;

LEVEL ONE SUM1 = IN1 + IN2;

LEVEL ONE SUM3 = IN5;

LEVEL ONE SUM2 = IN3 + IN4;

```

#### **Arithmetic Overflow**

To avoid overflow/underflow during addition or subtraction, the most significant bit (MSB) padding should be applied to the operands before the operation is executed. Alternatively, the overflow/underflow can be detected and the result saturated if the application allows it. To prevent unnecessary data-path growth, appropriate LSB trimming may be applied with the choices of rounding off to the ceiling, to the floor, or around the mid-point. The examples below show MSB padding together with the bit-trimming.

```

--VHDL MSB padding when adding two 8-bit numbers

-- otputs are trimmed to 8-bit numbers

process (CLK)

begin

if CLK'event and CLK = '1' then

FULL_SIZE_SUM <= (IN1(7)&IN1) + (IN2(7)&IN2);

FULL_SIZE_DIFF <= (IN3(7)&IN3) - (IN4(7)&IN4);

end if;

end process;

FINAL_SUM <= FULL_SIZE_SUM(8 downto 1); -- LSB dropped

FINAL_DIFF <= FULL_SIZE_DIFF(8 downto 1); -- LSB dropped

```

```

//Verilog MSB padding when adding two 8-bit numbers

// otputs are trimmed to 8-bit numbers

always @ (posedge CLK)

begin

FULL_SIZE_SUM = {IN1[7],IN1} + {IN2[7],IN2};

FULL_SIZE_DIFF = {IN3[7],IN3} - {IN4[7],IN4};

end

assign FINAL_SUM = FULL_SIZE_SUM[8:1]; // LSB dropped

assign FINAL_DIFF = FULL_SIZE_DIFF[8:1]; // LSB dropped

```

#### **Binary Scaling**

Binary scaling is prone to errors due to potential mishandling of 2's complement numbers. A proper scaling requires that the MSB is preserved during the binary up- and down-scaling, as shown below.

```

--VHDL scaling of a 16-bit number

A_DIV_BY4 <= A(15)&A(15)&A(15 downto 2);

A_MULT_BY2 <= A(15)&A(13 downto 0)&'0';

//Verilog scaling of a 16-bit number

assign A_DIV_BY4 = {A[15],A[15],A[15:2]};

assign A_MULT_BY2 = {A[15],A[13:0],1'b0};

```

#### Counters

Among all the choices for counters, the binary counters are sufficient to cover most of the design needs. Gray counters may be used in cases when the single-bit-per-count change is absolutely necessary. Ripple counters should be avoided in safety-critical designs due to difficult timing simulation and verification. The examples below show the binary counter implementation as well as the ripple counter implementations.

```

--VHDL 8-bit binary counter

//Verilog 8-bit binary counter

process (CLK)

always @ (posedge CLK)

begin

begin

if CLK'event and CLK = '1' then

if (RST)

if RST = '1' then

CNT = 8'h00;

CNT \le X''00'';

CNT = CNT + 1;

CNT <= CNT + '1';

end if:

end if:

end process;

```

```

--VHDL 3-bit ripple counter

//Verilog 3-bit ripple counter

process (CLK)

always @ (posedge CLK)

begin

begin

if CLK'event and CLK = '1' then

Q0 = !Q0;

Q0 \le not Q0;

end

end if;

end process;

always @ (posedge Q0)

begin

process (Q0)

Q1 = !Q1;

begin

end

if Q0'event and Q0 = '1' then

O1 \leq not O1;

always @ (posedge Q1)

end if:

begin

end process;

Q2 = !Q2;

end

process (Q1)

begin

always @ (posedge Q2)

if Ol'event and Ol = 'l' then

begin

O2 \le not Q2;

Q3 = !Q3;

end if:

end

end process:

process (Q2)

begin

if Q2'event and Q2 = '1' then

Q3 \le not Q3;

end if:

end process;

```

#### Shift Registers

There are many different HDL implementations of shift registers depending on their functionality. The examples below show implementations of the parallel-to-serial shift registers and the serial-to-parallel shift registers.

```

//Verilog P-to-S shift register, MSB first

--VHDL P-to-S 8-bit shift register, MSB first

always @ (posedge CLK)

process (CLK)

begin

begin

if (RST) begin // reset

if CLK'event and CLK = '1' then

SHIFT = 8'h00;

if RST = '1' then -- reset

SHIFT CNT = 3'b000;

SHIFT <= X"00":

end

SHIFT CNT <= "000";

else if (LOAD == 1'b1) begin // load

elsif LOAD = 'l' then -- load

SHIFT = PDATA:

SHIFT <= PDATA;

SHIFT CNT = 3'b000;

SHIFT CNT <= "000";

elsif SHIFT CNT < "111" then -- shift

else if (SHIFT CNT < 3'b111) begin // shift

SHIFT(7 downto 1) <= SHIFT(6 downto 0);

SHIFT[7:1] = SHIFT[6:0];

SHIFT CNT <= SHIFT CNT + '1';

SHIFT CNT = SHIFT CNT + 1;

end if:

end if;

end

end process;

assign SDATA = SHIFT[7];

SDATA \leq SHIFT(7);

```

```

//Verilog P-to-S shift register, LSB first

--VHDL P-to-S 8-bit shift register, LSB first

always @ (posedge CLK)

process (CLK)

begin

begin

if (RST) begin // reset

if CLK'event and CLK = '1' then

SHIFT = 8'h00:

if RST = '1' then -- reset

SHIFT CNT = 3'b000;

SHIFT <= X"00";

SHIFT CNT <= "000";

else if (LOAD == 1'b1) begin // load

elsif LOAD = '1' then -- load

SHIFT = PDATA;

SHIFT <= PDATA;

SHIFT CNT <= "000";

SHIFT CNT = 3'b000;

elsif SHIFT CNT < "111" then -- shift

end

else if (SHIFT CNT < 3'b111) begin //shift

SHIFT(6 downto 0) <= SHIFT(7 downto 1);

SHIFT CNT <= SHIFT CNT + '1';

SHIFT[6:0] = SHIFT[7:1];

SHIFT CNT = SHIFT CNT + 1;

end if;

end if:

end

end

end process;

assign SDATA = SHIFT[0];

SDATA <= SHIFT(0);

```

```

//Verilog S-to-P shift register, LSB first

--VHDL S-to-P 8-bit shift register, LSB first

always @ (posedge CLK)

process (CLK)

begin

begin

if (RST) begin // reset

if CLK'event and CLK = '1' then

SHIFT = 8'h00;

if RST = '1' then -- reset

SHIFT_CNT = 3'b000;

SHIFT <= X"00":

end

SHIFT CNT <= "000";

else begin

// shift

else

-- shift

SHIFT[6:0] = SHIFT[7:1];

SHIFT(6 downto 0) <= SHIFT(7 downto 1);

SHIFT[7] = SDATA;

SHIFT(7) \le SDATA;

SHIFT_CNT = SHIFT_CNT + 1;

SHIFT CNT <= SHIFT CNT + '1';

end if;

if (SHIFT CNT == 3'b000) begin

if SHIFT CNT = "000" then

PDATA = SHIFT; // parallel data

PDATA <= SHIFT; -- parallel data

PDATA EN = 1'b1; // data ready

PDATA_EN <= '1'; -- data ready

end

else

PDATA EN <= '0';

PDATA EN = 1'b0;

end if;

end

end if:

end process;

```

```

--VHDL S-to-P 8-bit shift register, MSB first

//Verilog S-to-P shift register, MSB first

process (CLK)

always @ (posedge CLK)

begin

begin

if (RST) begin // reset

if CLK'event and CLK = '1' then

SHIFT = 8'h00;

if RST = '1' then -- reset

SHIFT CNT = 3'b000;

SHIFT <= X"00":

SHIFT CNT <= "000";

end

else begin

else

-- shift

// shift

SHIFT[7:1] = SHIFT[6:0];

SHIFT(7 downto 1) <= SHIFT(6 downto 0);

SHIFT[0] = SDATA;

SHIFT(0) \le SDATA;

SHIFT_CNT = SHIFT_CNT + 1;

SHIFT CNT <= SHIFT CNT + '1';

end if:

if SHIFT CNT = "000" then

if (SHIFT CNT == 3'b000) begin

PDATA = SHIFT; // parallel data

PDATA <= SHIFT; -- parallel data

PDATA EN <= '1'; -- data ready

PDATA EN = 1'b1; // data ready

end

PDATA EN <= '0';

else

end if:

PDATA EN = 1'b0;

end if:

end

end process;

```

# **ROM Design**

Read-Only Memory (ROM) can be implemented as a look-up table using the **case** statement or as a synchronous ROM. Examples are shown below. Also, ROM can be implemented using vendor-specific core generation tools such as CORE Generator from Xilinx, MegaWizard from Altera, or SmartGen from Actel. The generated ROM components are then instantiated in the HDL code. The ROM cores generated by these tools should be simulated before instantiation to avoid different interpretations of the ROM design by different vendors.

```

//Verilog ROM design using case statement

--VHDL ROM design using case statement

always @ (ADDRESS)

process (ADDRESS)

begin

begin

case (ADDRESS)

case ADDRESS is

2'b00 : DATA = 4'h7;

when "00" \Rightarrow DATA \iff X"7";

2'b01 : DATA = 4'h6;

when "01" \Rightarrow DATA \iff X"6";

when "10" => DATA <= X"C";

2'b10 : DATA = 4'hC;

2'b11 : DATA = 4'hE;

when others \Rightarrow DATA \iff X"E":

endcase

end case:

end

end process;

```

```

--VHDL synchronous ROM

entity syncc ROM is

port (CLK: in std logic;

ADDR: in std logic vector(3 downto 0);

DOUT: out std logic_vector(7 downto 0));

end syncc ROM;

architecture behavioral of syncc ROM is

type rom is array(15 downto 0) of std logic vector(7 downto 0);

constant SROM: rom:=(X"01", X"20", X"AA", X"A0", -- ROM table

X"0F", X"1C", X"34", X"C4",

X"99", X"32", X"70", X"DD",

X"E3", X"B6", X"DB", X"12");

begin

process (CLK)

begin

if CLK'event and CLK = '1' then

DOUT <= SROM(conv integer(ADDR)); -- output data

end if;

end process:

end behavioral;

//Verilog synchronous ROM

module SROM (CLK, ADDR, DOUT);

input CLK;

input [7:0] ADDR;

output [7:0] DOUT;

reg [7:0] SROM [255:0];

reg [7:0] DOUT;

initial begin

$readmemb("rom table.list", SROM); // reads ROM data from a file

always @ (posedge CLK)

DOUT = SROM[ADDR]; // output data

end

endmodule

```

## RAM Design

Random Access Memory (RAM) can be in different forms, including single-port synchronous, dual-port synchronous, and dual-port asynchronous. Single-port synchronous RAM can be used whenever simultaneous writes and reads from two different memory locations are not required. This is the simplest RAM implementation that can be easily tested and verified. If simultaneous reads and writes are necessary, dual-port synchronous RAM should be used. Care should be taken to explicitly define RAM

behavior during simultaneous reading and writing to the same memory cell. Depending on the application, there may be either write-first or read-first RAM implementations. Dual-port asynchronous RAM should be generally avoided in safety-critical designs because of their cross-clock boundaries that are difficult to simulate and verify. Below are examples of single-port synchronous RAM and the dual-port, read-first synchronous RAM implementations. RAM can also be instantiated after the RAM component has been generated using one of the vendor-specific core generators. The cores generated by these tools should be simulated before instantiation to avoid different interpretations of the RAM design by different vendors.

```

--VHDL single-port synchronous RAM

entity sp sync RAM is

port (CLK : in std logic;

WE

: in std logic;

ADDR: in std logic vector(7 downto 0);

DIN : in std logic vector(7 downto 0);

DOUT: out std logic vector(7 downto 0));

end sp sync RAM;

architecture behavioral of sp sync RAM is

type ram is array(255 downto 0) of std logic vector(7 downto 0);

signal SP_RAM: ram;

begin

process (CLK)

begin

if CLK'event and CLK = '1' then

if WE = '1' then

SP RAM(conv integer(ADDR)) <= DIN; -- RAM write

DOUT <= SP RAM(conv integer(ADDR)); -- RAM read

end if:

end process;

end behavioral;

//Verilog single-port synchronous RAM

module sp sync RAM (CLK, WE, ADDR, DIN, DOUT);

input CLK;

input WE;

input [3:0] ADDR;

input [7:0] DIN;

output [7:0] DOUT;

reg [7:0] SP RAM [15:0];

reg [7:0] DOUT;

always @ (posedge CLK)

begin

DOUT = SP RAM[ADDR];

// RAM read

if (WE) SP RAM[ADDR] = DIN; // RAM write

end

endmodule

```

```

--VHDL dual-port read-first synchronous RAM

```

```

entity dp sync RAM is

port (CLK : in std logic;

WE

: in std logic;

RE

: in std logic;

WADDR: in std logic vector(7 downto 0);

RADDR: in std logic vector(7 downto 0);

DIN : in std logic vector(7 downto 0);

DOUT: out std logic vector(7 downto 0));

end dp sync RAM;

architecture behavioral of dp sync RAM is

type ram is array(255 downto 0) of std logic vector(7 downto 0);

signal DP RAM : ram;

begin

process (CLK)

begin

if CLK'event and CLK = '1' then

if WE = '1' then

DP RAM(conv integer(WADDR)) <= DIN; -- RAM write

end if;

if RE = '1' then

DOUT <= DP RAM(conv integer(RADDR)); -- RAM read

end if;

end process;

end behavioral;

//Verilog dual-port read-first synchronous RAM

module dp sync RAM (CLK, WE, RE, WADDR, RADDR, DIN, DOUT);

input CLK;

input WE;

input RE;

input [7:0] WADDR;

input [7:0] RADDR;

input [7:0] DIN;

output [7:0] DOUT;

reg [7:0] DP_RAM [255:0];

reg [7:0] DOUT;

always @ (posedge CLK)

begin

if (WE) DP RAM[WADDR] = DIN; // RAM write

end

always @ (posedge CLK)

begin

if (RE) DOUT = DP_RAM[RADDR]; // RAM read

end

endmodule

```

# FIFO Design

First-in-first-out (FIFO) structures are used for memory storage, data delay, data rate change, and data format change. They are usually designed as dual-port synchronous RAM with write and read counters controlling the write and the read address. The asynchronous FIFO should be generally avoided in safety-critical designs because their cross-clock boundaries are difficult to simulate and verify. Below are examples of synchronous FIFO implementations. Also, FIFO can be instantiated after the FIFO component has been generated using one of the vendor-specific core generators. However, the cores generated by these tools should be simulated before instantiation to avoid different interpretations of the FIFO design by different vendors.

# --VHDL synchronous FIFO RAM WRITE:process (CLK) begin if CLK'event and CLK = '1' then if WE = '1' and FF = '0' then - write to FIFO if not full FIFO RAM(conv integer(WADDR)) <= DIN; end if: end process; RAM READ:process (CLK) begin if CLK'event and CLK = '1' then if RE = '1' and EF = '0' then - read from FIFO if not empty DOUT <= FIFO RAM(conv integer(RADDR)); end if: end if; end process; WRITE POINTER:process (CLK,CLR) begin if CLR = '1' then - clear write pointer $WADDR \leq X"00";$ elsif CLK'event and CLK = '1' then if WE = '1' and FF = '0' then – increment write pointer if not full WADDR <= WADDR + '1'; end if: end if; end process;

```

READ POINTER:process (CLK,CLR)

begin