NUREG/CR-6962 BNL-NUREG-80141-2008

# Traditional Probabilistic Risk Assessment Methods for Digital Systems

Office of Nuclear Regulatory Research

## AVAILABILITY OF REFERENCE MATERIALS IN NRC PUBLICATIONS

#### **NRC Reference Material**

As of November 1999, you may electronically access NUREG-series publications and other NRC records at NRC's Public Electronic Reading Room at <u>http://www.nrc.gov/reading-rm.html</u>. Publicly released records include, to name a few, NUREG-series publications; *Federal Register* notices; applicant, licensee, and vendor documents and correspondence; NRC correspondence and internal memoranda; bulletins and information notices; inspection and investigative reports; licensee event reports; and Commission papers and their attachments.

NRC publications in the NUREG series, NRC regulations, and *Title 10, Energy*, in the Code of *Federal Regulations* may also be purchased from one of these two sources.

- 1. The Superintendent of Documents U.S. Government Printing Office Mail Stop SSOP Washington, DC 20402–0001 Internet: bookstore.gpo.gov Telephone: 202-512-1800

- Fax: 202-512-2250 2. The National Technical Information Service Springfield, VA 22161–0002 www.ntis.gov 1–800–553–6847 or, locally, 703–605–6000

A single copy of each NRC draft report for comment is available free, to the extent of supply, upon written request as follows:

- Address: U.S. Nuclear Regulatory Commission Office of Administration

- Mail, Distribution and Messenger Team Washington, DC 20555-0001

E-mail: DISTRIBUTION@nrc.gov Facsimile: 301–415–2289

Some publications in the NUREG series that are posted at NRC's Web site address

http://www.nrc.gov/reading-rm/doc-collections/nuregs are updated periodically and may differ from the last printed version. Although references to material found on a Web site bear the date the material was accessed, the material available on the date cited may subsequently be removed from the site.

#### **Non-NRC Reference Material**

Documents available from public and special technical libraries include all open literature items, such as books, journal articles, and transactions, *Federal Register* notices, Federal and State legislation, and congressional reports. Such documents as theses, dissertations, foreign reports and translations, and non-NRC conference proceedings may be purchased from their sponsoring organization.

Copies of industry codes and standards used in a substantive manner in the NRC regulatory process are maintained at—

The NRC Technical Library Two White Flint North 11545 Rockville Pike Rockville, MD 20852–2738

These standards are available in the library for reference use by the public. Codes and standards are usually copyrighted and may be purchased from the originating organization or, if they are American National Standards, from—

American National Standards Institute 11 West 42<sup>nd</sup> Street New York, NY 10036–8002 www.ansi.org 212–642–4900

Legally binding regulatory requirements are stated only in laws; NRC regulations; licenses, including technical specifications; or orders, not in NUREG-series publications. The views expressed in contractor-prepared publications in this series are not necessarily those of the NRC.

The NUREG series comprises (1) technical and administrative reports and books prepared by the staff (NUREG-XXXX) or agency contractors (NUREG/CR-XXXX), (2) proceedings of conferences (NUREG/CP--XXXX), (3) reports resulting from international agreements (NUREG/IA-XXXX), (4) brochures (NUREG/BR-XXXX), and (5) compilations of legal decisions and orders of the Commission and Atomic and Safety Licensing Boards and of Directors' decisions under Section 2.206 of NRC's regulations (NUREG-0750).

**DISCLAIMER:** This report was prepared as an account of work sponsored by an agency of the U.S. Government. Neither the U.S. Government nor any agency thereof, nor any employee, makes any warranty, expressed or implied, or assumes any legal liability or responsibility for any third party's use, or the results of such use, of any information, apparatus, product, or process disclosed in this publication, or represents that its use by such third party would not infringe privately owned rights.

NUREG/CR-6962 BNL-NUREG-80141-2008

. ....

# Traditional Probabilistic Risk Assessment Methods for Digital Systems

Manuscript Completed: May 2008 Date Published: October 2008

Prepared by T.L. Chu, G. Martinez-Guridi, M. Yue, J. Lehner, and P. Samanta

Brookhaven National Laboratory P.O. Box 5000 Upton, NY 11973

A. Kuritzky, NRC Project Manager

NRC Job Code N6413

Office of Nuclear Regulatory Research

## ABSTRACT

At present, there are no consensus methods for quantifying the reliability of digital systems. The U.S. Nuclear Regulatory Commission (NRC) currently is undertaking assessments of the reliability of digital instrumentation and control (I&C) systems, using traditional and non-traditional (dynamic) methods in parallel. The NRC tasked Brookhaven National Laboratory (BNL) with conducting the research on the traditional methods. In general, these are methods that are well-established but they differ from dynamic methods in that they do not explicitly model the interactions between the plant system being modeled and the plant physical processes, nor the timing of these interactions.

The principal objective of the current project is to determine the capabilities and limitations of using traditional reliability modeling methods to develop and quantify digital system reliability models, with the desired goal of supporting the development of regulatory guidance for assessing risk evaluations involving digital systems. To accomplish this objective, the following tasks will be performed:

- 1. Develop desirable characteristics for reliability models of digital systems that could provide input to the technical basis for risk evaluations related to current and new reactors.

- 2. Select two traditional reliability methods and apply them to two example digital systems to determine the capabilities and limitations of these methods.

- 3. Compare the resulting digital system reliability models to the desirable characteristics to identify areas where additional research will improve the capabilities of the methods.

- 4. Develop a method, if necessary, for integrating the digital system reliability models into a nuclear power plant probabilistic risk assessment (PRA).

This report specifically addresses the development of the desirable characteristics and lays out the process by which the first reliability study of an example digital system will be performed. This work indicates that the traditional methods of Event Tree/Fault Tree and Markov modeling appear to be useful for the PRA of digital I&C systems, but also reveals limitations in the state-of-the-art for modeling digital systems using traditional PRA methods and where additional research and development are needed. The report offers other insights and conclusions obtained during this work and proposes activities to be conducted when applying these methods to the first reliability study. Note, in keeping with the principal objective stated above, this project will generally not involve advancements in the state-of-the-art, such as the estimation of risk from software faults.

•

## FOREWORD

Nuclear power plants have traditionally relied on analog systems for their instrumentation and control (I&C) functions. With a shift in technology to digital systems as the result of analog obsolescence and digital functional advantages, existing plants have begun to replace some current analog I&C systems, while new plant designs fully incorporate digital systems.

The current licensing process for digital systems is based on deterministic criteria. In its 1995 Probabilistic Risk Assessment (PRA) Policy Statement, the U.S. Nuclear Regulatory Commission (NRC) encouraged the use of PRA technology in all regulatory matters to the extent supported by the state of the art in PRA methods and data. Though many activities are carried out in the life cycle of digital systems to ensure a high-quality product, there are no consensus methods at present for quantifying the reliability of these systems. This has been an impediment to developing a risk-informed analysis process for digital systems.

To address this limitation, the NRC is currently researching the use of both traditional PRA methods and dynamic methods for modeling digital systems. The desired goal of this research is to develop regulatory guidance for the use of risk information in regulatory decisions for new and operating reactors. This research is consistent with the recommendations from the 1997 National Research Council report on digital I&C in nuclear power plants and with the Commission staff requirements memorandum (M061108), dated December 6, 2006, which directs the staff to address deployment of digital systems, including the area of risk-informed digital I&C.

This NUREG/CR report documents the initial research into the use of traditional PRA methods for modeling and quantifying the reliability of digital I&C systems. The objectives of this initial research are to (1) determine the capabilities and limitations of using traditional reliability methods to develop and quantify digital system reliability models, (2) develop desirable characteristics for this kind of model, and (3) identify any state-of-the-art advancements needed to enhance the use of risk information associated with digital systems in regulatory decisions.

Christiana H. Lui, Director Division of Risk Analysis Office of Nuclear Regulatory Research U.S. Nuclear Regulatory Commission

# TABLE OF CONTENTS

# <u>Section</u>

| ABSTRACTiii |                                                                       |           |  |

|-------------|-----------------------------------------------------------------------|-----------|--|

|             | FOREWORDv                                                             |           |  |

|             | LIST OF FIGURES xi                                                    |           |  |

|             | OF TABLES                                                             |           |  |

| ACKN        | IOWLEDGEMENTS                                                         | xiii      |  |

| ACRC        | DNYMS                                                                 | xiv       |  |

| 1.          | INTRODUCTION                                                          | 1_1       |  |

| 1.1         | Background                                                            |           |  |

| 1.2         | Objectives                                                            |           |  |

| 1.2         | Project Scope                                                         |           |  |

|             |                                                                       |           |  |

| 1.4         | Structure of the Report                                               |           |  |

| 2.          | DESIRABLE CHARACTERISTICS FOR EVALUATING PROBABILISTIC MODEL          | SOF       |  |

|             | DIGITAL SYSTEMS                                                       | 2-1       |  |

| 2.1         | Level of Detail of the Probabilistic Model                            | 2-2       |  |

| 2.2         | Identification of Failure Modes of the Components of a Digital System | 2-4       |  |

| 2.3         | Modeling of Software Failures                                         | 2-6       |  |

| 2.4         | Modeling of Dependencies                                              |           |  |

| 2.5         | Probabilistic Data                                                    |           |  |

| 2.6         | Uncertainty                                                           |           |  |

| 2.7         | Integration of the Digital System Model with a PRA Model              |           |  |

| 2.8         | Human Errors                                                          |           |  |

| 2.9         | Documentation and Results                                             |           |  |

| 2.10        | Summary                                                               |           |  |

|             |                                                                       |           |  |

| 3.          | OVERALL APPROACH OF MODELING                                          |           |  |

| 3.1         | Operational Aspects and Risk Insights of the DFWCS                    | 3-1       |  |

| 3.2         | Major Steps to Building Models                                        | 3-2       |  |

| 3.2.1       | Definition and Scope of the Probabilistic Model                       | 3-2       |  |

| 3.2.2       | Evaluating the Frequency of an Initiating Event                       | 3-2       |  |

| 3.2.2.1     | 1 Markov Method                                                       | 3-4       |  |

|             | 2 Fault Tree Method                                                   |           |  |

| 3.2.3       | Overview of Modeling Process                                          | 3-5       |  |

| 4           | DESCRIPTION OF A DIGITAL FEEDWATER CONTROL SYSTEM                     | 4-1       |  |

| 4.1         | System Level Description.                                             |           |  |

| 4.1.1       | Control Modes and Algorithms                                          |           |  |

| 4.1.2       | Deviations and Failover Operation                                     |           |  |

| 4.1.2       | Description of Azonix µMAC 7000 Controllers and Fischer & Porter      | 4-11      |  |

| 4.2         | 53MC5000 Controllers                                                  | 4-13      |  |

| 4.2.1       | Azonix µMAC 7000 Microprocessors                                      |           |  |

| 4.2.1       | Fischer & Porter (F&P) 53MC5 Controllers                              |           |  |

| 4.2.2       | Digital Valve Controller and Speed Controller                         |           |  |

| 4.3.1       | Digital Valve Controller                                              |           |  |

| 4.3.1       | Lovejoy Speed Controller for FWP                                      | / 11-4-17 |  |

| 4.3.2       |                                                                       |           |  |

# TABLE OF CONTENTS (Continued)

# <u>Section</u>

| 4.4   | Dependencies and Interfaces                                       |            |

|-------|-------------------------------------------------------------------|------------|

| 4.4.1 | Interfaces with Operators                                         |            |

| 4.4.2 | Interfaces between Two Digital Feedwater Control Systems          | 4-19       |

| 4.4.3 | Interfaces between Main and Backup Microprocessors of the DFWCS   | 4-19       |

| 4.4.4 | Interfaces between Main/Backup Microprocessor and M/A Controllers | 4-20       |

| 4.4.5 | Interfaces Among the M/A Controllers                              |            |

| 4.4.6 | Interfaces with Sensors, Valves, and Pumps                        |            |

| 4.4.7 | Power Supply                                                      |            |

| 4.5   | Digital Features                                                  |            |

| 4.5.1 | Microlink Communication Issues.                                   |            |

| 4.5.2 | Watchdog Timers                                                   |            |

| 4.5.3 | Software                                                          |            |

| 4.5.4 | Missing Module Diagnostics                                        | 4-28       |

| 4.5.5 | Cyclic Redundancy Check                                           |            |

|       |                                                                   |            |

| 5.    | FMEA OF A DIGITAL FEEDWATER CONTROL SYSTEM                        | 5-1        |

| 5.1   | Introduction                                                      |            |

| 5.2   | Scope and Levels of Detail of FMEA                                |            |

| 5.2.1 | System Level FMEA.                                                |            |

| 5.2.7 | Module Level FMEA                                                 |            |

| 5.2.2 | Major-Component-of-Module Level FMEA                              |            |

| 5.2.5 | FMEA Approach                                                     |            |

|       | Summary of FMEAs at Different Levels                              | J-J<br>E E |

| 5.4   | FMEA at Top-Level of DFWCS                                        |            |

| 5.4.1 | FMEA at Level of DFWCS Modules                                    |            |

| 5.4.2 |                                                                   |            |

| 5.4.3 | FMEA at Level of Major-Component-of-Module of DFWCS Main CPU Mod  |            |

| 5.5   | Insights Learned from the FMEA                                    |            |

| 5.6   | General Issues Associated with FMEA of Digital Systems            |            |

| 5.7   | Concluding Remarks                                                |            |

| •     |                                                                   |            |

| 6.    | DEVELOPMENT OF A MARKOV MODEL OF DIGITAL FEEDWATER                | 0.4        |

|       | CONTROL SYSTEM                                                    |            |

| 6.1   | Development of Module-Level Markov Model                          |            |

| 6.1.1 | A Markov Model of the Main CPU                                    |            |

| 6.1.2 | Development of the Markov Model of Other Modules                  |            |

| 6.2   | Development of a System-Level Markov Model                        |            |

| 6.3   | Description of How Software Failure Rates Fit in the Model        |            |

| 6.4   | A Simplified Method for Building and Solving the Model            | 6-8        |

|       | ·                                                                 |            |

| 7.    | DEVELOPMENT OF A FAULT TREE MODEL OF THE DIGITAL                  |            |

|       | FEEDWATER CONTROL SYSTEM                                          |            |

| 7.1   | Fault Tree Construction                                           |            |

| 7.1.1 | Modeling of Failure to Control MFRV                               |            |

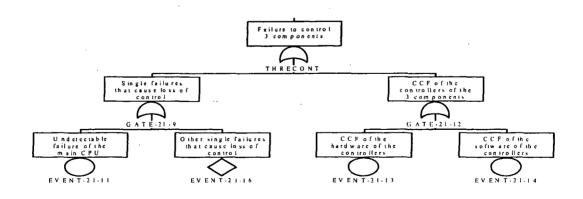

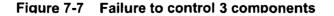

| 7.1.2 | Modeling of Failure to Control Three Components                   |            |

| 7.2   | Fault Tree Evaluation                                             | 7-7        |

# TABLE OF CONTENTS (Continued)

# <u>Section</u>

Ż

1. A. M. M.

| 8.      | DEVELOPMENT OF RELIABILITY PARAMETERS FOR DIGITAL                                 |      |

|---------|-----------------------------------------------------------------------------------|------|

|         | SYSTEM RELIABILITY MODEL                                                          | 8-1  |

| 8.1     | Categories of Potential Data Sources for Digital Systems and Components           | 8-2  |

| 8.2     | Issues in Digital System Data Analyses                                            |      |

| 8.3     | Reliability Parameters Based on Databases Using Reliability Prediction Methods    |      |

| 0.0     | (RPMs) and Other Methods                                                          | 8-4  |

| 8.3.1   | Military Handbook 217F                                                            |      |

| 8.3.2   | Telcordia                                                                         |      |

| 8.3.3   | PRISM Database                                                                    |      |

| 8.3.4   | IEEE Standard 500-1984                                                            |      |

| 8.3.5   | IEC Standard 61508                                                                |      |

|         |                                                                                   | 0-0  |

| 8.3.6   | Reliability Data for Safety instrumented Systems, PDS Data Handbook, 2006 Edition | 0 0  |

|         |                                                                                   | 0-9  |

| 8.4     | Reliability Data Collection and Analysis for Digital Systems and Components       | 0.40 |

|         | from Industrial Operational Experience                                            |      |

| 8.4.1   | Digital Core Protection Calculators of Combustion Engineering Reactor             | 0.40 |

|         | Protection System                                                                 |      |

| 8.4.2   | Eagle-21 Channels of Westinghouse Reactor Protection System                       | 8-11 |

| 8.4.3   | Operating Experience of Digital Core Protection Calculators of CE RPS             | 8-13 |

| 8.4.4   | Failure Experience of Programmable Logic Controllers Used in Emergency            |      |

|         | Shutdown Systems of Natural Gas Compression Stations                              | 8-15 |

| 8.4.5   | Operational Failure Experience of Fault-Tolerant Digital Control Systems in       |      |

|         | Different Industries                                                              | 8-19 |

| 8.4.6   | Failure Rates for Programmable Logic Controllers Used in Chemical and             |      |

|         | Nuclear Plants                                                                    | 8-21 |

| 8.4.7   | Savannah River Site (SRS) Generic Data Development Based on Data from             |      |

|         | Different Industries                                                              | 8-23 |

| 8.4.8   | Failure Parameters of Digital Trip Module (DTM) and Trip Logic Unit (TLU) in      |      |

|         | ESBWR Probabilistic Risk Assessment (PRA)                                         | 8-24 |

| 8.4.9   | Reliability Study of Digital Engineered Safety Feature Actuation System of        |      |

|         | Korean Standard Nuclear Power Plant                                               | 8-27 |

| 8.4.10  | Digital RPS and ESFAS of AP600 Reactors                                           | 8-28 |

| 8.4.11  | Digital Systems of AP1000 Reactors                                                | 8-29 |

| 8.4.12  | Reliability Modeling of Digital Instrumentation and Control Systems for Nuclear   |      |

|         | Reactor Probabilistic Risk Assessments                                            | 8-29 |

| 8.5     | Data Sources in Nuclear Industry                                                  | 8-29 |

| 8.5.1   | Licensee Event Report (LER) Database                                              | 8-29 |

| 8.5.2   | Equipment Performance and Information Exchange (EPIX) Database                    | 8-31 |

| 8.6     | Summary of Failure Data Review                                                    | 8-32 |

| 8.6.1   | Categorization of Data Collection Levels                                          |      |

| 8.6.2   | Summary of Reliability Parameters of Microprocessor or Microprocessor-Related     |      |

| J. J. 4 | Systems                                                                           | 8-33 |

| 8.7     | Generic Failure Rate Estimate Using a Hierarchical Bayesian Method                | 8-38 |

| 8.7.1   | Hierarchical Bayesian Models for Failure Rates Determination                      |      |

| 8.7.2   | Failure Rates Estimate of Digital Components Using the HBM                        |      |

# TABLE OF CONTENTS (Continued)

| Sectio                                                                          | Section Page                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 8.7.3<br>8.7.4                                                                  | Sensitivity Analysis                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 9.                                                                              | MODELING TO ADDRESS DESIRABLE CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                            |  |  |

| 10.<br>10.1<br>10.2<br>10.3<br>10.4<br>10.4.1<br>10.4.2<br>10.5<br>10.6<br>10.7 | SUMMARY AND CONCLUSIONS10-1Selection of Traditional Methods10-1Development of Desirable Characteristics for Evaluating Reliability Models of DigitalSystems10-2Performance of an FMEA of the DFWCS10-3Modeling Approach10-4Development of Markov Model10-4Development of Fault Tree Model10-5Development of Failure Parameter Database10-5Next Steps10-6Recommendations for Research10-7 |  |  |

| 11.                                                                             | REFERENCES                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| APPEI                                                                           | NDIX A SUMMARY REPORT OF THE EXTERNAL REVIEW PANEL<br>MEETING ON RELIABILITY MODELING OF DIGITAL SYSTEMS<br>(MAY 23-24, 2007)                                                                                                                                                                                                                                                            |  |  |

| APPEI                                                                           | NDIX B DETAILED FMEA OF THE DFWCS AT DIFFERENT LEVELS                                                                                                                                                                                                                                                                                                                                    |  |  |

| APPE                                                                            | NDIX C OTHER METHODS FOR MODELING DIGITAL SYSTEMS                                                                                                                                                                                                                                                                                                                                        |  |  |

х

# LIST OF FIGURES

| Figure |                                                            | <u>Page</u> |

|--------|------------------------------------------------------------|-------------|

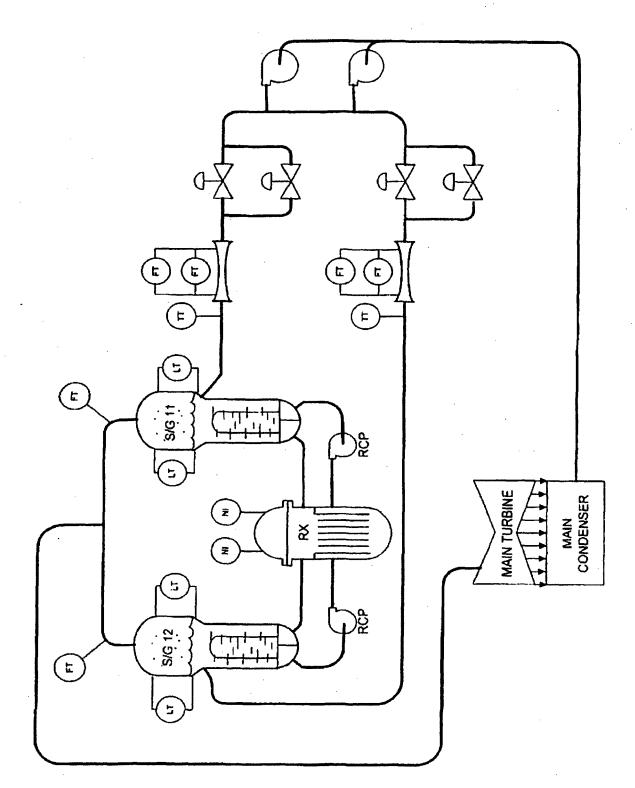

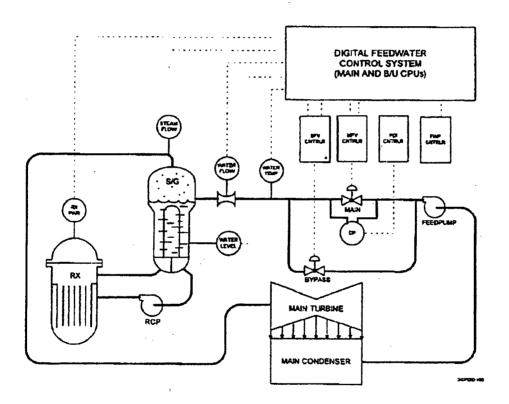

| 4-1    | A Simplified Diagram of the Feedwater System               |             |

| 4-2    | One of the Reactor Coolant Loops with Its Associated DFWCS | 4-3         |

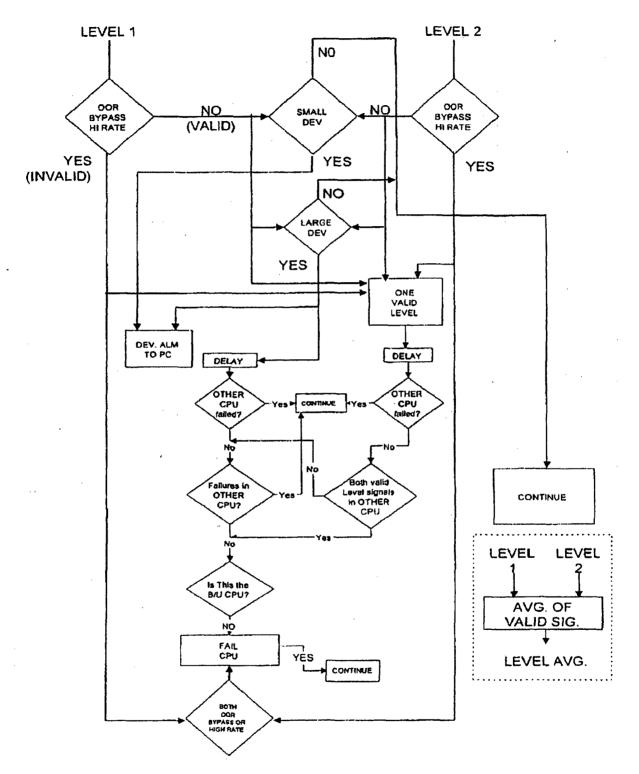

| 4-3    | S/G Level Deviation Logic                                  |             |

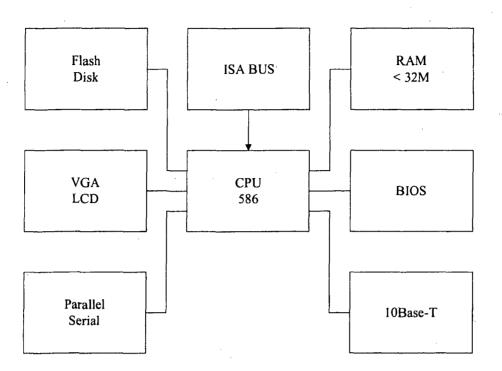

| 4-4    | PC Section - A Standard ISA Architecture                   |             |

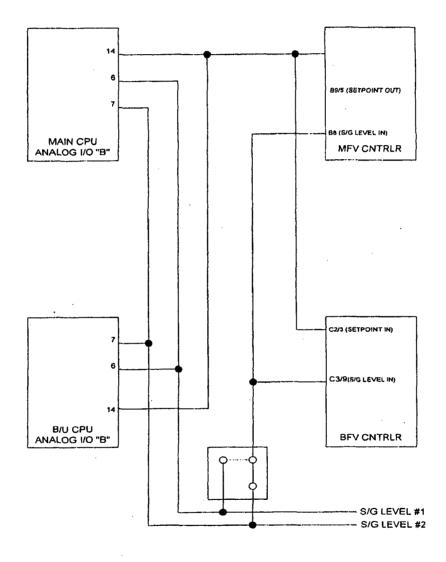

| 4-5    | S/G Level Connections                                      |             |

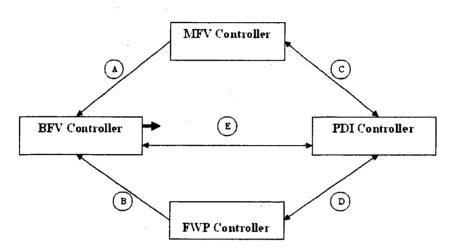

| 4-6    | Data Exchange between Device Controllers                   |             |

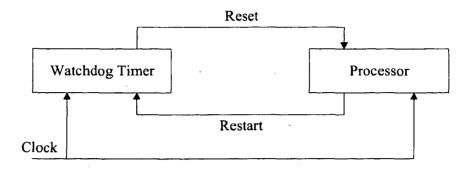

| 4-7    | A Generic Design of Watchdog Timer                         | 4-26        |

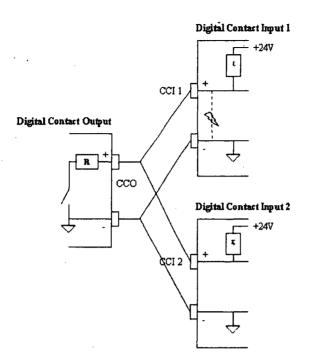

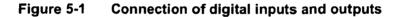

| 5-1    | Connection of Digital Inputs and Outputs                   | 5-5         |

| 6-1    | Components of Main CPU Module                              | 6-2         |

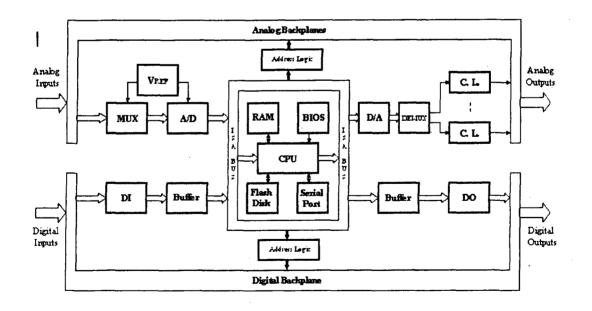

| 7-1    | Loss of Control of the Loop Associated with a DFWCS        | 7-2         |

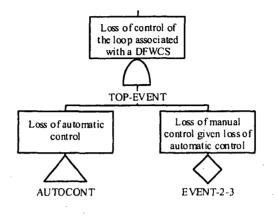

| 7-2    | Loss of Automatic Control                                  |             |

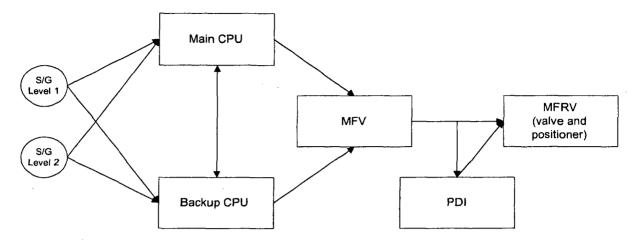

| 7-3    | Simplified Diagram of the Control of an MFRV               |             |

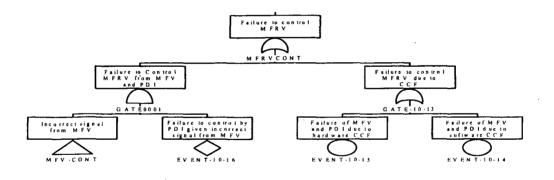

| 7-4    | Failure to Control MFRV                                    |             |

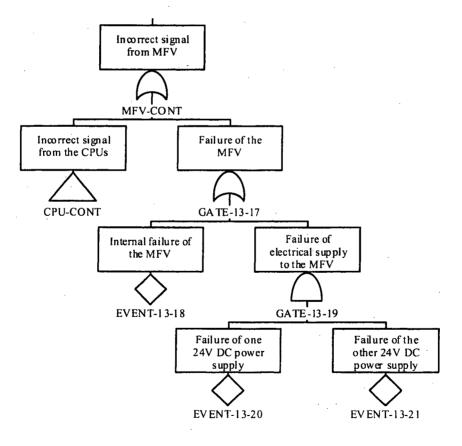

| 7-5    | Incorrect Signal from MFV                                  | 7-5         |

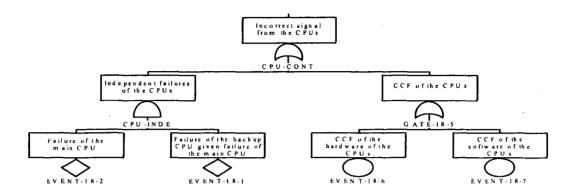

| 7-6    | Incorrect Signal from the CPUs                             |             |

| 7-7    | Failure to Control 3 Components                            |             |

# LIST OF TABLES

| <u>Table</u> | Page                                                                                                                                                           |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-1          | Summary of Desirable Characteristics                                                                                                                           |

| 4-1<br>4-2   | Analog Inputs/Outputs of the Microprocessors                                                                                                                   |

| 4-3<br>4-4   | Inputs and Outputs of PB4R Digital Signal Isolator                                                                                                             |

| 4-5          | Inputs and Outputs of BFV M/A Controller 4-10                                                                                                                  |

| 4-6<br>4-7   | Inputs and Outputs of FWP M/A Controller                                                                                                                       |

| 4-8          | Microlink Communication Summary                                                                                                                                |

| 5-1          | Failure Modes of the Main CPU Module 5-8                                                                                                                       |

| 6-1          | Postulated Failure Modes of Some Other Modules                                                                                                                 |

| 8-1          | SINTEF Recommended Input Data for Single Safety System                                                                                                         |

| 8-2          | Failure Rate of Digital Core Protection Calculator from NUREG/CR-5500,<br>Volume 10                                                                            |

| 8-3          | Failure Rate of Eagle-21 Channel Processor of Westinghouse RPS from<br>NUREG/CR-5500, Volume 2                                                                 |

| 8-4          | Failure Rates for Different Types of CPCS and/or CEACS Failures from Bickel [2006]8-16                                                                         |

| 8-5<br>8-6   | Failure Rate of PLCs Used in Emergency Shutdown Systems from Mitchell [1993] 8-18<br>Failure Data of Fault-Tolerant Digital Control Systems from Paula [1993a] |

| 8-7          | Digital System Component Failure Rates from OREDA-84 and Humphreys & Daniels 8-21                                                                              |

| 8-8          | Digital System Component Failure Rates of a TMR System from Triconex and                                                                                       |

| 8-9          | Humphreys & Daniels                                                                                                                                            |

| 8-10         | Summary of PLC Failure Data from French NPPs from Paula [1993b]8-23                                                                                            |

| 8-11         | Failure Rate and Coverage of PLCs in Chemical and Nuclear Power Plants<br>from Paula [1993b]                                                                   |

| 8-12         | Savannah River Site (SRS) Generic Data from Blanton [1993]                                                                                                     |

| 8-13         | Generic Component Data for a Korean DESFAS Reliability Analysis<br>from Varde [2003]                                                                           |

| 8-14         | Example Failure Parameters of DFWCS Components from Aldemir [2007]                                                                                             |

| 8-15         | Data Collection Level and Failure Parameters for a Microprocessor or a<br>Microprocessor-Related System from Different Sources                                 |

| 8-16         | CCF Data from Different Sources                                                                                                                                |

| 8-17         | Failure Records of a Digital Component Extracted from PRISM RACdata Database 8-44                                                                              |

| 8-18<br>8-19 | Characteristics of Population Variability Distribution of a Digital Component Data 8-46                                                                        |

| 0-19         | Error Factors Based on a Hierarchical Bayes Analysis                                                                                                           |

## ACKNOWLEDGEMENTS

The work presented in this report includes work carried out during several years under several U.S. Nuclear Regulatory Commission (NRC) projects. Many other people helped in one way or another with this work, and we are grateful to them.

In particular, we are indebted to the current NRC Project Manager, Alan Kuritzky, for his technical and managerial support. We are also especially grateful to the external peer reviewers who commented on some early parts of the work, as well as those reviewers from the NRC, the nuclear industry, other Department of Energy national laboratories, and academia who reviewed the final draft of this report.

We also express our appreciation to Avril Woodhead for her editorial review of several revisions of the report, and to Jean Frejka and Nicole Kelly who put several versions of the report together and helped with the logistical aspects of the project.

# ACRONYMS

| A/D     | Analog/Digital                                     |

|---------|----------------------------------------------------|

| A/M     | Auto/Manual                                        |

| ABWR    | Advanced Boiling Water Reactor                     |

| AIC     | Airborne, Inhibited, Cargo                         |

| ALWR    | Advanced Light Water Reactor                       |

| API     | Application Program Interface                      |

| ASIC    | Application Specific Integrated Circuit            |

| ASME    | American Society of Mechanical Engineers           |

| BFRV    | Bypass Feedwater Regulating Valve                  |

| BFV     | Bypass Feedwater Valve                             |

| BNL     | Brookhaven National Laboratory                     |

| BWR     | Boiling Water Reactor                              |

| B/U     | Backup                                             |

| CCA     | Circuit Card Assembly                              |

| CCF     | Common Cause Failure                               |

| CDF     | Core Damage Frequency                              |

| CE      | Combustion Engineering                             |

| CEA     | Control Element Assembly                           |

| CEAC    | Control Element Assembly Calculator                |

| CFR     | Code of Federal Regulations                        |

| CIP     | Communication Interface Processor                  |

| CMM     | Capability Maturity Model                          |

| CPC     | Core Protection Calculator                         |

| CPCS    | Core Protection Calculator                         |

| CPU     | Core Protection Calculator System                  |

| CRC     | Central Processing Unit                            |

| CSMA    | Cyclic Redundancy Check                            |

| CSMA/BA | Carrier Sense Multiple Access                      |

| CSMA/CA | Carrier Sense Multiple Access/Collision Avoidance  |

| CSMA/CD | Carrier Sense Multiple Access/Collision Detect     |

| D/A     | Digital/Analog                                     |

| DCS     | Digital Control System                             |

| DD      | Dangerous Detected                                 |

| DEMUX   | Demultiplexer                                      |

| DESFAS  | Digital Engineered Safety Feature Actuation System |

| DFWCS   | Digital Feedwater Control System                   |

| DOD     | Department of Defense                              |

| DPPS    | Digital Plant Protection System                    |

| DRPS    | Digital Reactor Protection System                  |

| DTM     | Digital Trip Module                                |

| DU      | Dangerous Undetected                               |

xiv

# ACRONYMS (Continued)

| EMI   | Electromagnetic Interference                      |

|-------|---------------------------------------------------|

| ENF   | Expected Number of System Failures                |

| EPIX  | Equipment Performance and Information Exchange    |

| EPRD  | Electronic Parts Reliability Date                 |

| ESRI  | Electric Power Research Institute                 |

| ESBWR | Economic Simplified Boiling Water Reactor         |

| ESD   | Emergency Shutdown                                |

| ESF   | Engineered Safety Feature                         |

| ESFAS | Engineered Safety Features Actuation System       |

| ET    | Event Tree                                        |

| F&P   | Fischer & Porter                                  |

| F-T   | Fault-Tolerant                                    |

| FIX   | Function Index                                    |

| FMEA  | Failure Modes and Effects Analysis                |

| FRV   | Feedwater Regulating Valve                        |

| FT    | Fault Tree                                        |

| FWP   | Feedwater Pump                                    |

| FWS   | Feedwater System                                  |

| HART  | Highway Addressable Remote Technology             |

| HAZOP | Hazard and Operability Study                      |

| HBM   | Hierarchical Bayesian Method                      |

| HIFT  | Hardware Implemented Fault Tolerant               |

| HRA   | Human Reliability Analysis                        |

| HSI   | Human-System Interface                            |

| HVAC  | Heating, Ventilation, and Air-Conditioning        |

| I/I   | Current/Current                                   |

| I/O   | Input/Output                                      |

| I/P   | Current-to-Pressure                               |

| I&C   | Instrumentation and Control                       |

| IDE   | Integrated Drive Electronics                      |

| IE    | Initiating Event                                  |

| IEC   | International Electrotechnical Commission         |

| IEEE  | Institute of Electrical and Electronics Engineers |

| IIS   | In-Core Instrumentation System                    |

| INL   | Idaho National Laboratory                         |

| ISA   | Industry Standard Architecture                    |

| ISR   | Interrupt Service Routine                         |

KSNPP

Korean Standard Nuclear Power Plant

# ACRONYMS (Continued)

| LER                                                                                        | License Event Report                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LVDT                                                                                       | Linear Variable Differential Transformer                                                                                                                                                                                                                                                                                        |

| M/A<br>MAC<br>MB<br>MCC<br>MCMC<br>MCS<br>MFRV<br>MFV<br>MFV<br>MFV<br>MTTF<br>MTTF<br>MUX | Manual/Automatic<br>Media Access Control<br>Mega-Byte<br>Motor Control Center<br>Markov Chain Monte Carlo<br>Minimal Cutsets<br>Main Feedwater Regulating Valve<br>Main Feedwater Valve<br>Main Feedwater Valve<br>Main Feedwater<br>Man-Machine Interface<br>Maintenance and Test Panel<br>Mean Time To Failure<br>Multiplexer |

| NAM                                                                                        | Nuclear Asset Management                                                                                                                                                                                                                                                                                                        |

| NASA                                                                                       | National Aeronautics and Space Administration                                                                                                                                                                                                                                                                                   |

| NEA                                                                                        | Nuclear Energy Agency                                                                                                                                                                                                                                                                                                           |

| NMSS                                                                                       | Office of Nuclear Material Safety and Safeguards                                                                                                                                                                                                                                                                                |

| NONC                                                                                       | Non-Critical Failures                                                                                                                                                                                                                                                                                                           |

| NPP                                                                                        | Nuclear Power Plant                                                                                                                                                                                                                                                                                                             |

| NPRDS                                                                                      | Nuclear Plant Reliability Data System                                                                                                                                                                                                                                                                                           |

| NRC                                                                                        | Nuclear Regulatory Commission                                                                                                                                                                                                                                                                                                   |

| NRO                                                                                        | Office of New Reactors                                                                                                                                                                                                                                                                                                          |

| OREDA                                                                                      | Offshore Reliability Data                                                                                                                                                                                                                                                                                                       |

| PC                                                                                         | Personal Computer                                                                                                                                                                                                                                                                                                               |

| PCB                                                                                        | Printed Circuit Board                                                                                                                                                                                                                                                                                                           |

| PDI                                                                                        | Pressure Differential Indication                                                                                                                                                                                                                                                                                                |

| PDU                                                                                        | Plasma Display Unit                                                                                                                                                                                                                                                                                                             |

| PI                                                                                         | Performance Indicator                                                                                                                                                                                                                                                                                                           |

| PLC                                                                                        | Programmable Logic Controller                                                                                                                                                                                                                                                                                                   |

| PLS                                                                                        | Plant Control System                                                                                                                                                                                                                                                                                                            |

| PMS                                                                                        | Protection and Plant Safety System                                                                                                                                                                                                                                                                                              |

| PRA                                                                                        | Probabilistic Risk Assessment                                                                                                                                                                                                                                                                                                   |

| PROM                                                                                       | Programmable Read Only Memory                                                                                                                                                                                                                                                                                                   |

| PVC                                                                                        | Population Variation Curve                                                                                                                                                                                                                                                                                                      |

| PWB                                                                                        | Printed Wiring Board                                                                                                                                                                                                                                                                                                            |

| PWM                                                                                        | Pulse Width Modulation                                                                                                                                                                                                                                                                                                          |

| PWR                                                                                        | Pressurized Water Reactor                                                                                                                                                                                                                                                                                                       |

xvi

# ACRONYMS (Continued)

| RAC    | Reliability Analysis Center                                      |

|--------|------------------------------------------------------------------|

| RADS   | Reliability and Availability Data System                         |

| RAM    | Random Access Memory                                             |

| RCP    | Reactor Coolant Pump                                             |

| RES    | Office of Nuclear Reactor Research                               |

| RFI    | Radio Frequency Interference                                     |

| ROM    | Read Only Memory                                                 |

| RPM    | Reliability Prediction Method                                    |

| RPS    | Reactor Protection System                                        |

| RTCA   | Radio Technical Commission for Aeronautics                       |

| S/G    | Steam Generator                                                  |

| SCSS   | Sequence Coding and Search System                                |

| SFC    | Single Failure of Channel                                        |

| SIFT   | Software Implemented Fault Tolerant                              |

| SIL    | Safety Integrity Level                                           |

| SINTEF | Scientific and Industrial Research at the Norwegian Institute of |

|        | Technology                                                       |

| SLC    | Software Life Cycle                                              |

| SMS    | Special Monitoring System                                        |

| SPAR   | Standard Plant Analysis Risk                                     |

| SRS    | Savannah River Site                                              |

| SSPI   | Safety System Performance Indicator                              |

| SSPS   | Solid State Protection System                                    |

| STD    | Spurious Trip Detected                                           |

| STU    | Spurious Trip Undetected                                         |

| TLU    | Trip Logic Unit                                                  |

| TMR    | Triple Modular Redundancy                                        |

| UCN    | Ulchin Nuclear Power Plant                                       |

| UMD    | University of Maryland                                           |

| URD    | Utility Requirements Document                                    |

| US     | United States                                                    |

| VGA    | Video Graphics Array                                             |

| Vref   | Voltage Reference                                                |

| WANO   | World Association of Nuclear Operations                          |

| WDT    | Watchdog Timer                                                   |

# 1. INTRODUCTION

## 1.1 Background

Nuclear power plants (NPPs) have traditionally relied upon analog systems for their monitoring, control, and protection functions. With a shift in technology to digital systems due to analog obsolescence and digital functional advantages, existing plants have begun to replace current analog systems while new plant designs fully incorporate digital systems. Since digital instrumentation and control (I&C) systems are expected to play an increasingly important role in nuclear power plant safety, the U.S. Nuclear Regulatory Commission (NRC) established a digital system research plan [NRC 2006] that defines a coherent set of research programs to support its regulatory needs.

The current licensing process for digital systems is based on deterministic engineering criteria. In its 1995 Probabilistic Risk Assessment (PRA) policy statement [NRC 1995], the Commission encouraged the use of PRA technology in all regulatory matters to the extent supported by the state-of-the-art in PRA methods and data. Though many activities have been completed in the area of risk-informed regulation, the risk-informed analysis process for digital systems has not yet been satisfactorily developed. Since, at present, there are no consensus methods for quantifying the reliability of digital systems, one of the programs included in the NRC digital system research plan addresses risk assessment methods and data for digital systems.

The objective of the NRC digital system risk research is to identify and develop methods, analytical tools, and regulatory guidance to support (1) using information on the risks of digital systems in NPP regulatory decisions, and (2) including models of digital systems into NPP PRAs. The NRC currently is undertaking assessments of the reliability of digital l&C systems, using traditional and non-traditional (dynamic) methods in parallel. For the purposes of this research, dynamic methods are defined as those that explicitly attempt to model (1) the interactions between a plant system and the plant's physical processes, i.e., the values of process variables, and (2) the timing of these interactions, i.e., the timing of the progress of accident sequences. Traditional methods are defined here as those that are well-established but that do not explicitly model the interactions between the plant system being modeled and the plant physical processes, nor the exact timing of these interactions. An example of this type of method is the traditional Event Tree/Fault Tree (ET/FT) approach.

In the past few years, Brookhaven National Laboratory (BNL) has been working on NRC projects to investigate methods and tools for probabilistic modeling of digital systems. The work included reviewing literature on digital system modeling [Chu 2004, Chu 2007], reviewing and analyzing operating experience of digital systems [Chu 2006], developing failure rate estimates using a Hierarchical Bayesian analysis [Yue 2006], and performing Failure Modes and Effects Analyses (FMEAs) of digital systems. The results of these reviews show that failures of digital systems caused several events that resulted in either a reactor trip or equipment unavailability at U.S. NPPs, and at least one event at a foreign NPP that resulted in a small loss of coolant accident during refueling [NEA 1998], as well as many significant events in other industries. This experience indicates that digital system failures have the potential to be contributors to plant risk. The NRC has now tasked BNL with conducting research on the use of traditional reliability modeling methods for digital I&C systems, which is the subject of this report. Information on the NRC research on the

use of dynamic reliability modeling methods for digital I&C systems can be found in NUREG/CR-6901 [Aldemir 2006] and NUREG/CR-6942 [Aldemir 2007].

# 1.2 Objectives

The principal objective of the current project is to determine the existing capabilities and limitations of using traditional reliability modeling methods to develop and quantify digital system reliability models, with the desired goal of supporting the development of regulatory guidance for assessing risk evaluations involving digital systems. To accomplish this objective, the following tasks will be performed:

- 1. Develop a set of desirable characteristics for reliability models of digital systems that could provide input to the technical basis for risk evaluations related to current and new reactors.

- 2. Select two traditional reliability methods and apply them to two example digital systems to determine the capabilities and limitations of these methods.

- 3. Compare the resulting digital system reliability models to the set of desirable characteristics to identify areas where additional research might improve the capabilities of the methods.

- 4. Develop a method, if necessary, for integrating the digital system reliability models into a NPP PRA.

This report specifically addresses the development of the set of desirable characteristics and lays out the process by which the first reliability study of an example digital system will be performed. Note, in keeping with the principal objective stated above, this process will generally not involve advancements in the state-of-the-art, such as the estimation of risk from software faults.

## **1.3 Project Scope**

The development of the set of desirable characteristics and the comparison of several existing digital system reliability models to these characteristics were documented in a BNL preliminary letter report to the NRC. To more fully involve the technical community in this task, an external review panel was set up to review the findings documented in the letter report. The panel was comprised of six members, all of whom have expertise in modeling and quantifying digital system reliability, and also in probabilistic risk assessment. The panel met at BNL on May 23 and 24, 2007. The updated information from the letter report, as well as a summary report of the external review panel meeting, are included as part of this NUREG/CR.

As mentioned in the previous section, this project includes the application of traditional reliability modeling methods to example digital systems to support the development of tools and methods for including this type of model into PRAs. In determining which traditional methods to select for trial application, two factors were considered. First, because the ultimate goal of this project is to support the NRC in developing regulatory guidance for using risk information related to digital systems in the licensing actions of current or future NPPs, heavy emphasis was placed on those methods likely to be used by the nuclear industry. Secondly, many dynamic methods (i.e., methods that attempt to explicitly model the interactions between a plant system and the plant's physical

processes, and the timing of these interactions) were not considered because they are the subject of a parallel NRC research project.

Considering the above factors, the two traditional reliability modeling methods selected for trial application as part of this project are the traditional ET/FT method and the Markov method. The traditional ET/FT method has been commonly used by the U.S. nuclear power industry and in other countries and industries. The Markov method can be a powerful tool for analyzing digital systems because it can explicitly model system configurations arising from the ability of some digital systems to detect failures and change their configuration during operation. The Markov method can also explicitly treat failure and repair times. Further, the Markov method was used previously to model NPP systems that are commonly included in PRAs, as well as digital systems.

A number of other methods that may be useful for developing and quantifying reliability models of digital systems are discussed in an appendix to this report. While it is not practical to further explore all of these methods as part of the current project, some of them may warrant further attention if other studies demonstrate their capability and practicality.

As part of this project, the traditional ET/FT and Markov methods will be applied to two example systems (referred to as "benchmark" test cases). The first benchmark test case involves a digital feedwater control system (DFWCS) of a two-loop pressurized water reactor (PWR); the second involves a Reactor Protection System (RPS). Both a control system (which is typically non-safety-related) and a safety-related protection system were selected because these two types of systems may entail different modeling issues.

During this phase of the project, detailed information was only available for the first benchmark system (i.e., the DFWCS). Therefore, the DFWCS is used in this report to illustrate how the traditional reliability modeling methods will be applied in the later tasks of the project (i.e., in the actual benchmark studies). In order to delineate how the PRA models of the first benchmark system will be analyzed, constructed, and quantified using each of the two methods selected in the first task, the following activities were undertaken:

- 1. The DFWCS was analyzed in detail, including its function, components, associated controllers, dependencies and interfaces, and digital features, in order to gain a full understanding of the way the DFWCS and each of its relevant components operate.

- 2. The failure modes of the DFWCS components and the impact of each of them on the system function were determined by performing an FMEA.

- 3. The relevant failure modes of the components and their impacts on the DFWCS were used in developing approaches for constructing and quantifying probabilistic models using the traditional ET/FT and Markov methods.

- 4. Probabilistic parameters needed for quantifying the probabilistic models were investigated for each digital component failure mode.

The actual detailed construction and quantification of the two PRA models for each of the benchmark systems, as well as the integration of the digital system models into an overall PRA of a NPP, will be the subject of later tasks. As stated previously, in keeping with the principal objective of this project (i.e., to determine the *existing* capabilities and limitations of traditional reliability

modeling methods when applied to digital systems), performance of the benchmark studies will generally not involve advancements in the state-of-the-art. For example, the estimation of risk from software faults is outside the scope of this project because the methods to accomplish this are not considered to be mature yet. Technical areas that require such advancements are identified in this report.

The objective of this report is to describe approaches for developing reliability models of the DFWCS using the two selected traditional methods to address the set of desirable characteristics as far as the current state-of-the-art of these methods allows. A comparison of the models against the characteristics will be carried out when the task of developing the models is complete, and results will be presented in a subsequent report.

The methods and approaches in this report are applied to attempt to develop as complete a probabilistic model of a digital system as possible, given the current limitations of the state of the art. This maximizes the insights that may be gained about aspects of digital system models, even if some of these aspects are ultimately determined to not be significant or necessary.

## **1.4** Structure of the Report

As mentioned previously, this report specifically addresses the development of a set of desirable characteristics for reliability models of digital systems and illustrates the process by which the benchmark studies will be performed. The set of characteristics is presented in Chapter 2, and these characteristics reflect feedback from the external review panel meeting (Appendix A documents the discussions that took place at the meeting)<sup>(1)</sup>.

Chapters 3 to 9 illustrate the process by which the two benchmark studies will be performed, using the DFWCS as an example. Chapter 3 presents the overall approach to modeling the DFWCS, Chapter 4 describes this system, and Chapter 5 discusses its FMEA. This information is used in Chapters 6 and 7 to describe how the Markov and fault tree models, respectively, will be developed for the DFWCS. Chapter 8 presents the probabilistic data for digital components that is planned to be used for quantifying these models. Chapter 9 discusses the way these models will address the desirable characteristics described in Chapter 2. Finally, Chapters 10 and 11 contain the conclusions and references, respectively.

FMEA tables for the DFWCS are presented in Appendix B. Appendix C provides brief information on some other methods that may be useful for developing and quantifying reliability models of digital systems, though they were not explored further as part of this project.

<sup>&</sup>lt;sup>(1)</sup> Appendix A refers to draft "evaluation criteria" for reliability models of digital systems. This nomenclature has since been changed to "desirable characteristics" of digital system reliability models.

# 2. DESIRABLE CHARACTERISTICS FOR PROBABILISTIC MODELS OF DIGITAL SYSTEMS

A probabilistic model of a system and its associated probabilistic data should adequately account for the design features of the system that could affect its reliability, and hence, contribute to plant risk. Thus, the goal of this chapter is to define those characteristics of a model of digital systems that reflect these features. To meet this goal, a draft set of desirable characteristics was generated for digital system reliability models that are based on general experience with probabilistic risk assessments (PRAs), and on the particular considerations for digital system models. The following sources were used for developing the characteristics:

- 1. A literature review on modeling methods and failure databases of digital systems, carried out under a previous task of this project, which identified reports and white papers, and is summarized in a conference paper [Chu 2004].

- 2. A review of software failure experience and hardware failure data, made under a previous activity of this project, which led to development of a model of software failures and a basis for modeling of software failures, along with a hardware failure database capturing the variability of different data sources (Chapter 8 summarizes the work on hardware failures). The concept of software failure is discussed in Section 2.3.

- 3. The development of Failure Modes and Effects Analyses (FMEAs) of the Triconex Tricon platform and the digital feedwater control system (DFWCS) of a Combustion Engineering nuclear power plant (NPP) performed under previous activities related to this project. Chapter 5 presents the FMEA of the DFWCS.

- 4. The knowledge and experience of the study team from developing and reviewing PRA models of NPPs.

The desirable characteristics are grouped into the following nine broad categories which cover the probabilistic model of a digital system and its documentation:

- 1. Level of detail of the probabilistic model,

- 2. Identification of the failure modes of the components of a digital system,

- 3. Modeling of software failures,

- 4. Modeling of dependencies,

- 5. Probabilistic data,

- 6. Uncertainty,

- 7. Ease of integration with a PRA model,

- 8. Human errors, and

- 9. Documentation and results.

For each category, background information is first provided, and then the related desirable characteristics are presented. The focus of the characteristics here is on the design features of digital systems. The PRA model would be expected to meet the general guidelines provided in documents such as the PRA Procedures Guide [Hickman 1983] and the American Society of Mechanical Engineers (ASME) standard for PRA for NPP applications [ASME 2005].

The desirable characteristics are potentially relevant to any kind of probabilistic model of a digital system. There are some characteristics for which methods and/or data may not be

currently available. The characteristics establish the important features of a probabilistic model of a digital system, but they do not specify how to achieve this goal (i.e., they do not specify methods for modeling these features). Furthermore, it is debatable whether some of the characteristics are relevant. The intent was to include all characteristics addressing design aspects that are potential contributors to system unreliability and plant risk. Some characteristics may be modified later using the findings from the benchmark studies.

## 2.1 Level of Detail of the Probabilistic Model

In its most basic form, a probabilistic model of a system (analog or digital) is a combination of a "logic model" and probabilistic data. The logic model describes the relationship of relevant failures of the components of the system leading to some undesired event, such as the failure of the system to respond adequately to a demand, while the data are some parameters of each failure, such as its failure rate.

In general, a system's logic model evolves by breaking down the failures of its major components, such as the channels of a system, into the individual failures of their constituent components. This refinement from failures of major components into failures of basic components is continued to a level of detail that the analyst considers appropriate. Rouvroye and Brombacher [1999] illustrated the difficulty in modeling digital systems. They employed different models from an early version of International Electrotechnical Commission (IEC) 61508 [IEC 61508] and other methods to determine the average probability of failure on demand of an example system. They demonstrated that the results obtained with different methods are significantly different, i.e., the failure probabilities can differ by more than an order-of-magnitude. The authors did not detail their analysis, e.g., how the methods were applied and whether or not consistent levels of detail and failure data were used. Nevertheless, these results are not surprising. Different methods model an example system at different levels of detail introducing different approximations/errors. Also, potential inconsistencies in the failure parameters used at different levels of modeling could introduce significant variations in the results.

The level of detail of the most basic failures of the model is driven by two considerations, i.e., the objective of the modeling and the availability of probabilistic data:

1. The objective of modeling the system. Modeling digital systems in a PRA is intended to support risk evaluations, particularly with regard to the digital systems themselves. Hence, the desirable characteristics in modeling, such as level of detail and quality, depend on the types of decisions to be made. In general, the decision could be about determining the acceptability of a system or component or making changes to it. For replacing an analog reactor protection system (RPS) with a digital one, it is desirable to show that the new system is no less reliable than the old one. This can be demonstrated by comparing their probabilities of failure on demand; that is, if realistic data reflecting the specific design and operating condition are available at the system level and the new system does not introduce any new dependencies, a simple analysis of these data may be adequate to demonstrate the objective.

On the other hand, a decision may be required about an issue at a lower level of detail, e.g., eliminating the redundancy within the individual channels of a four channel system. Then, the level of modeling detail must be sensitive enough to explicitly address any difference. If a decision on selecting the protocol of a communication network is to be made, then a model able to differentiate between protocols has to be developed. Also,

different cyclic redundancy check (CRC) designs have different capabilities of detecting and correcting faults [Siewiorek 1992]. Therefore, to assess the impacts of the design difference, a model at the right level of detail must be formulated.

The level of detail of a reliability model of a system (analog or digital) should capture its design features that could affect reliability. This desirable characteristic is particularly difficult for digital systems because if a single bit is askew, the whole system may collapse, as on June 28, 1999, when a stuck-at-one fault on a data line of the Traffic Collision Avoidance System of a Korean Air Cargo flight contributed to a near-miss collision with British Air Flight 027. However, it may not be feasible to model individual bits. The appropriate lowest level of detail of a reliability model of a digital system may be modeling a microprocessor as a component because the execution of software is based on the processor and because the communications between the microprocessors and other components of the digital system can be modeled. Another possibility of capturing the details of the design of a digital system is using applicable failure data at a higher level, so that the design is implicitly included, as long as the data realistically reflects all the failure modes of the specific design, the model adequately supports the study's objective, and dependencies are accounted for.