NUREG/CR-6997 BNL-NUREG-90315-2009

# Modeling a Digital Feedwater Control System Using Traditional Probabilistic Risk Assessment Methods

**Final Report**

Office of Nuclear Regulatory Research

#### AVAILABILITY OF REFERENCE MATERIALS IN NRC PUBLICATIONS

#### **NRC Reference Material**

As of November 1999, you may electronically access NUREG-series publications and other NRC records at NRC's Public Electronic Reading Room at <u>http://www.nrc.gov/reading-rm.html.</u> Publicly released records include, to name a few, NUREG-series publications; *Federal Register* notices; applicant, licensee, and vendor documents and correspondence; NRC correspondence and internal memoranda; bulletins and information notices; inspection and investigative reports; licensee event reports; and Commission papers and their attachments.

NRC publications in the NUREG series, NRC regulations, and *Title 10, Energy*, in the Code of *Federal Regulations* may also be purchased from one of these two sources.

- 1. The Superintendent of Documents U.S. Government Printing Office Mail Stop SSOP Washington, DC 20402–0001 Internet: bookstore.gpo.gov Telephone: 202-512-1800 Fax: 202-512-2250

- 2. The National Technical Information Service Springfield, VA 22161–0002 www.ntis.gov

- 1-800-553-6847 or, locally, 703-605-6000

A single copy of each NRC draft report for comment is available free, to the extent of supply, upon written request as follows:

Address: Office of Administration Reproduction and Mail Services Branch U.S. Nuclear Regulatory Commission Washington, DC 20555-0001 E-mail: DISTRIBUTION@nrc.gov Facsimile: 301-415-2289

Some publications in the NUREG series that are posted at NRC's Web site address

http://www.nrc.gov/reading-rm/doc-collections/nuregs are updated periodically and may differ from the last printed version. Although references to material found on a Web site bear the date the material was accessed, the material available on the date cited may subsequently be removed from the site.

#### **Non-NRC Reference Material**

Documents available from public and special technical libraries include all open literature items, such as books, journal articles, and transactions, *Federal Register* notices, Federal and State legislation, and congressional reports. Such documents as theses, dissertations, foreign reports and translations, and non-NRC conference proceedings may be purchased from their sponsoring organization.

Copies of industry codes and standards used in a substantive manner in the NRC regulatory process are maintained at—

The NRC Technical Library Two White Flint North 11545 Rockville Pike Rockville, MD 20852–2738

These standards are available in the library for reference use by the public. Codes and standards are usually copyrighted and may be purchased from the originating organization or, if they are American National Standards, from—

> American National Standards Institute 11 West 42<sup>nd</sup> Street New York, NY 10036–8002 www.ansi.org 212–642–4900

Legally binding regulatory requirements are stated only in laws; NRC regulations; licenses, including technical specifications; or orders, not in NUREG-series publications. The views expressed in contractor-prepared publications in this series are not necessarily those of the NRC.

The NUREG series comprises (1) technical and administrative reports and books prepared by the staff (NUREG-XXXX) or agency contractors (NUREG/CR-XXXX), (2) proceedings of conferences (NUREG/CP-XXXX), (3) reports resulting from international agreements (NUREG/IA-XXXX), (4) brochures (NUREG/BR-XXXX), and (5) compilations of legal decisions and orders of the Commission and Atomic and Safety Licensing Boards and of Directors' decisions under Section 2.206 of NRC's regulations (NUREG-0750).

**DISCLAIMER:** This report was prepared as an account of work sponsored by an agency of the U.S. Government. Neither the U.S. Government nor any agency thereof, nor any employee, makes any warranty, expressed or implied, or assumes any legal liability or responsibility for any third party's use, or the results of such use, of any information, apparatus, product, or process disclosed in this publication, or represents that its use by such third party would not infringe privately owned rights.

## Modeling a Digital Feedwater Control System Using Traditional Probabilistic Risk Assessment Methods

# **Final Report**

Manuscript Completed: June 2008 Date Published: September 2009

Prepared by T.L. Chu, M. Yue, G. Martinez-Guridi, K. Mernick, and J. Lehner, BNL A. Kuritzky, NRC

Brookhaven National Laboratory Upton, NY 11973-5000

A. Kuritzky, NRC Project Manager

NRC Job Code N6413

Office of Nuclear Regulatory Research

.

### ABSTRACT

The United States Nuclear Regulatory Commission (NRC) is currently performing research on the development of probabilistic models for digital instrumentation and control systems for inclusion in nuclear plant probabilistic risk assessments. The desired goal of this research is to develop regulatory guidance for the use of risk information in regulatory decisions for new and operating reactors. This report documents the development of a reliability model of a digital feedwater control system using Markov methods supported by an automated failure modes and effects analysis (FMEA) tool. In general, the approach developed in this study should be applicable to both control and protection systems. Although the objective of the study is only to demonstrate the feasibility of the state of the art of traditional methods and data, the development of the automated FMEA tool can be considered an enhancement to the state of the art. Due to limitations in the scope of the study and the state of the art, the current model is not suitable to support regulatory decision-making. Additional research is needed to further enhance the state of the art, and potential areas of research are documented, for example, modeling of software failures. .

.

•

#### FOREWORD

Nuclear power plants have traditionally relied on analog systems for their instrumentation and control (I&C) functions. With a shift in technology to digital systems as the result of analog obsolescence and digital functional advantages, existing plants have begun to replace some current analog I&C systems, while new plant designs fully incorporate digital systems.

The current licensing process for digital systems is based on deterministic criteria. In its 1995 Probabilistic Risk Assessment (PRA) Policy Statement, the United States Nuclear Regulatory Commission (NRC) encouraged the use of PRA technology in all regulatory matters to the extent supported by the state of the art in PRA methods and data. Though many activities are carried out in the life cycle of digital systems to ensure a high-quality product, there are no consensus methods at present for quantifying the reliability of digital systems. This has been an impediment to developing a risk-informed analysis process for digital systems.

To address this limitation, the NRC is currently performing research on the development of probabilistic models for digital I&C systems for inclusion in nuclear plant PRAs. The desired goal of this research is to develop regulatory guidance for the use of risk information in regulatory decisions for new and operating reactors. This research is consistent with the recommendations from the 1997 National Research Council report on digital I&C in nuclear power plants and with the Commission staff requirements memorandum (M061108), dated December 6, 2006, which directs the staff to address deployment of digital systems, including the area of risk-informed digital I&C.

Brookhaven National Laboratory (BNL) is supporting the NRC in this research through a project to determine the existing capabilities and limitations of using traditional (i.e., static) reliability methods to develop and quantify digital system reliability models. A previous report (NUREG/CR-6962, [Chu 2008a]) documents the initial BNL work in this area, including developing desirable characteristics for evaluating reliability models of digital systems and establishing the process for performing the reliability study of a digital feedwater control system (DFWCS) using two traditional reliability modeling methods (i.e., the event tree/fault tree method and the Markov modeling method). The current report documents the application of these methods to the DFWCS. This report also compares the resultant models to the desirable characteristics identified in NUREG/CR-6962 [Chu 2008a] to identify areas where additional research could potentially improve the quality and usefulness of digital system reliability models.

v

Christiana H. Lui, Director Division of Risk Analysis Office of Nuclear Regulatory Research U.S. Nuclear Regulatory Commission

### **TABLE OF CONTENTS**

| Section                                                            | Page       |

|--------------------------------------------------------------------|------------|

| ABSTRACT                                                           |            |

| FOREWORD                                                           | v          |

| LIST OF FIGURES                                                    |            |

| LIST OF TABLES                                                     |            |

| EXECUTIVE SUMMARY                                                  |            |

| ACKNOWLEDGEMENTS                                                   |            |

| ACRONYMS AND ABBREVIATIONS                                         | xxi        |

|                                                                    |            |

| 1. INTRODUCTION                                                    | 1-1        |

| 1.1 Background                                                     | 1-1        |

| 1.2 Objectives and Scope of Benchmark Study                        | 1-2        |

| 1.3 Overall Approach of Benchmark Study                            | 1-3        |

| 2. SYSTEM DESCRIPTION AND THE SCOPE OF MODELING                    | 2-1        |

| 2.1 Main and Backup CPUs and Their External Watchdog Timers        |            |

| 2.2 MFV Controller                                                 |            |

| 2.3 FWP Controller                                                 |            |

| 2.4 BFV Controller                                                 |            |

| 2.5 PDI Controller                                                 |            |

| 2.6 Other Components                                               |            |

| 3. IDENTIFICATION OF INDIVIDUAL FAILURE MODES AND THEIR EFFECTS FO | D          |

| THE DFWCS                                                          | <b>.</b> . |

| 3.1 General Issues with Current FMEAs for Digital Systems          |            |

| 3.2 A Generic Approach to the FMEAs of Digital Systems             |            |

| 3.3 FMEAs of the DFWCS Using the Generic Approach                  |            |

| 3.3.1 FMEA of the Main CPU Module                                  |            |

|                                                                    | 00         |

| 3.3. I |                                                                          | 3-0  |

|--------|--------------------------------------------------------------------------|------|

| 3.3.2  | FMEA of the Backup CPU Module                                            | 3-9  |

| 3.3.3  | FMEA of the FWP Controller Module                                        |      |

| 3.3.4  | FMEA of the MFV Controller Module                                        | 3-17 |

| 3.3.5  | Considerations on the BFV Controller and the PDI Controller in the       |      |

|        | Reliability Model                                                        | 3-22 |

| 3.3.6  | FMEAs of Sensors, DC Power Supplies, and 120v AC Buses                   |      |

| 3.4    | Discussion and Limitations of the Generic Approach                       | 3-25 |

|        |                                                                          |      |

| 4.     | AN AUTOMATED TOOL OF PERFORMING FMEA OR DIGITAL SYSTEMS                  | 4-1  |

| 4.1    | The Advantages of Using an Automated Tool for Evaluating Failure Effects | 4-1  |

| 4.2    | An Automated Tool for Evaluating Failure Effects                         | 4-2  |

| 4.2.1  | Scope of the Automated FMEA Tool                                         |      |

| 4.2.2  | Integrating Modules into the Automated FMEA Tool                         | 4-3  |

| 4.2.3  | Input and Output Signals of the DFWCS Modules                            |      |

| 4.2.4  | Establishing a Base Case Using Operational Data                          | 4-12 |

|        |                                                                          |      |

## TABLE OF CONTENTS (Continued)

| <u>Sectio</u>                                                               | <u>on</u>                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>Page</u>                                                          |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.3<br>4.4<br>4.5              | Timing Issues Addressed in the Automated Tool<br>Criteria for Automatically Determining System Failure<br>Generation of Failure Sequences<br>Validation of the Automated FMEA Tool<br>A Summary of the Automated Tool Development and Illustrative FMEA Examples<br>Findings Using the Automated FMEA Tool<br>Discussion and Limitations of the Automated FMEA Tool<br>General Discussion on Developing Automated FMEA Tools for Digital Systems | . 4-14<br>. 4-15<br>. 4-15<br>. 4-16<br>. 4-18<br>. 4-19             |

| 5.<br>5.1<br>5.2<br>5.3<br>5.4                                              | MARKOV MODEL OF DIGITAL FEEDWATER CONTROL SYSTEM<br>Development of a Markov Transition Diagram<br>Analytical Solution of the Markov Model<br>A Simplified Markov Model<br>Discussion and Limitations of the Markov Model                                                                                                                                                                                                                         | . 5-2<br>5-6<br>. 5-9                                                |

| 6.<br>6.1<br>6.2<br>6.3                                                     | ESTIMATION OF FAILURE PARAMETERS<br>Hierarchical Bayesian Analyses of PRISM Data and Failure Rates from Other<br>Sources<br>Failure Mode Distributions<br>Common-Cause Failures (CCFs)                                                                                                                                                                                                                                                           | 6-2<br>. 6-3                                                         |

| 7.<br>7.1<br>7.2<br>7.3                                                     | QUANTIFICATION<br>Quantification of Markov Model<br>Approximate Quantification of Markov Model<br>Comparison with Operating Experience                                                                                                                                                                                                                                                                                                           | 7-1<br>7-4                                                           |

| 8.<br>8.1<br>8.2<br>8.3<br>8.4<br>8.4.1<br>8.4.2<br>8.4.3<br>8.4.4<br>8.4.5 | UNCERTAINTY ANALYSIS AND SENSITIVITY CALCULATIONS<br>Parameter Uncertainty<br>Modeling Uncertainty<br>Completeness Uncertainty<br>Sensitivity Calculations<br>Benefit of Redundancy in CPU.<br>Effectiveness of Watchdog Timers.<br>Benefit of Main Feedwater Valve (MFV) Demand Feedback Signals<br>Benefit of Deviation Logic<br>Summary of Sensitivity Analyses                                                                               | . 8-2<br>. 8-4<br>. 8-4<br>. 8-6<br>. 8-7<br>. 8-7<br>. 8-8<br>. 8-8 |

| 9.<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5                                       | COMPARISON WITH DESIRABLE CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                        | . 9-1<br>. 9-2<br>. 9-3<br>. 9-4                                     |

## TABLE OF CONTENTS (Continued)

| <u>Sectio</u>               | <u>on</u>                                                                                                                                                                                                     | <u>Page</u>      |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 9.6<br>9.7<br>9.8<br>9.9    | Uncertainty<br>Integration of the Digital System Model with a PRA Model<br>Human Errors<br>Documentation and Results                                                                                          | . 9-11           |

| 10.<br>10.1<br>10.2<br>10.3 | COMPARISON OF RESULTS WITH THOSE FROM DYNAMIC METHODS<br>Application of Dynamic Methods to the DFWCS<br>Comparison of Scope and Level of Detail<br>Comparison of Results from Traditional and Dynamic Methods | . 10-1<br>. 10-2 |

| 11.<br>11.1<br>11.2<br>11.3 | CONCLUSIONS, INSIGHTS, AND AREAS OF POTENTIAL ADDITIONAL<br>RESEARCH<br>Conclusions<br>Insights<br>Areas of Potential Additional Research                                                                     | . 11-2           |

| 12.                         | REFERENCES                                                                                                                                                                                                    | . 12-1           |

| APPE                        | NDIX A FAILURE MODES AND EFFECTS ANALYSIS OF DFWCS                                                                                                                                                            | . A-1            |

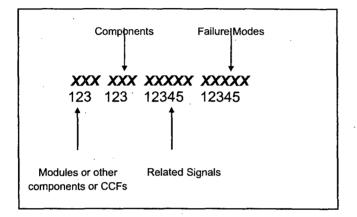

| APPE                        | NDIX B NAMING SCHEME AND COMPLETE LIST OF INDIVIDUAL FAILURE<br>MODES                                                                                                                                         | B-1              |

| APPE                        | NDIX C QUANTIFICATION OF MARKOV MODEL                                                                                                                                                                         | C-1              |

### LIST OF FIGURES

| Figure | <u>-</u>                                                                          | <u>Page</u> |

|--------|-----------------------------------------------------------------------------------|-------------|

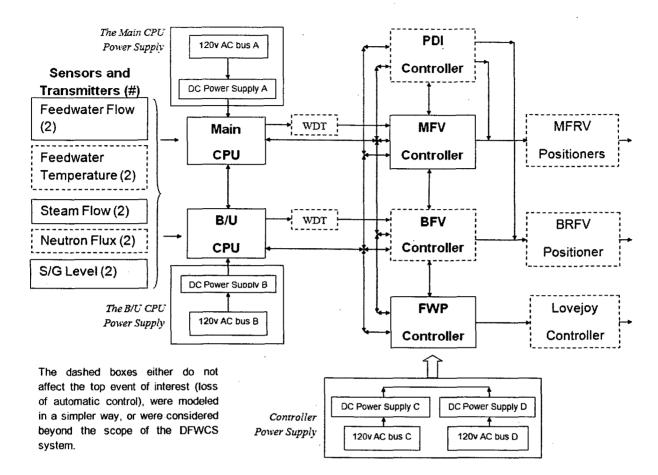

| 2-1    | Modules of the DFWCS model                                                        | . 2-2       |

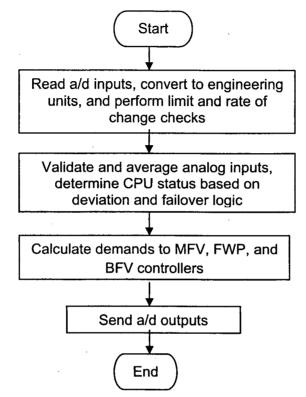

| 2-2    | High-level flow chart of application software of each CPU                         | . 2-4       |

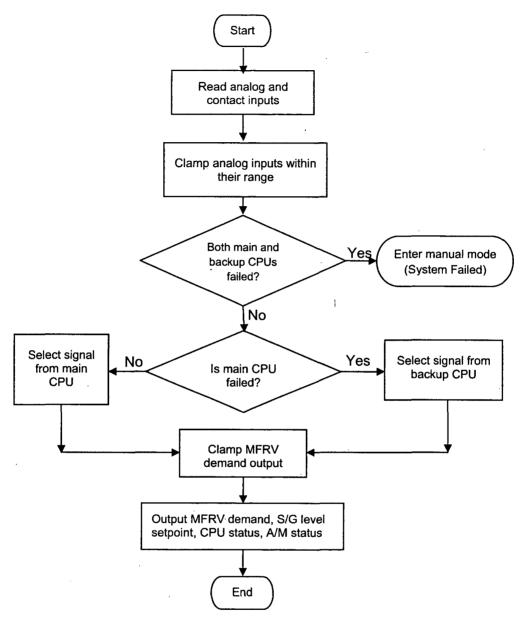

| 2-3    | High-level flowchart of MFV controller software                                   | . 2-6       |

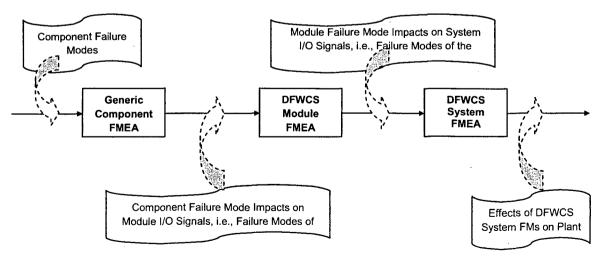

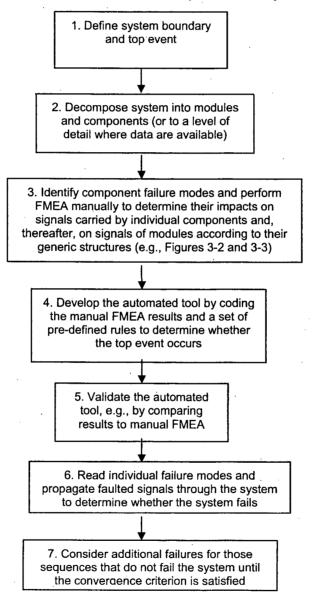

| 3-1    | Steps in the generic FMEA approach applied to the DFWCS                           | . 3-3       |

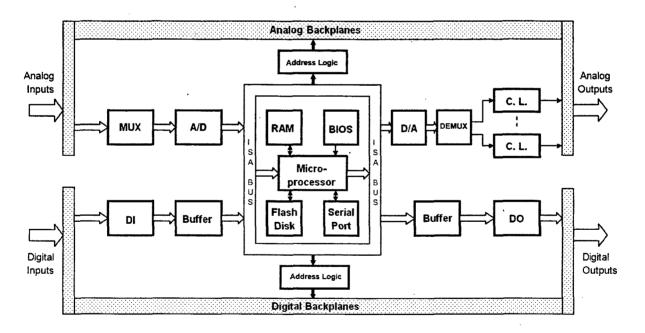

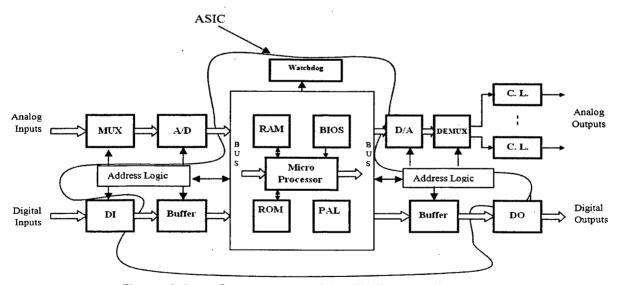

| 3-2    | Major components of the main CPU module                                           | . 3-6       |

| 3-3    | Components of the FWP controller module                                           |             |

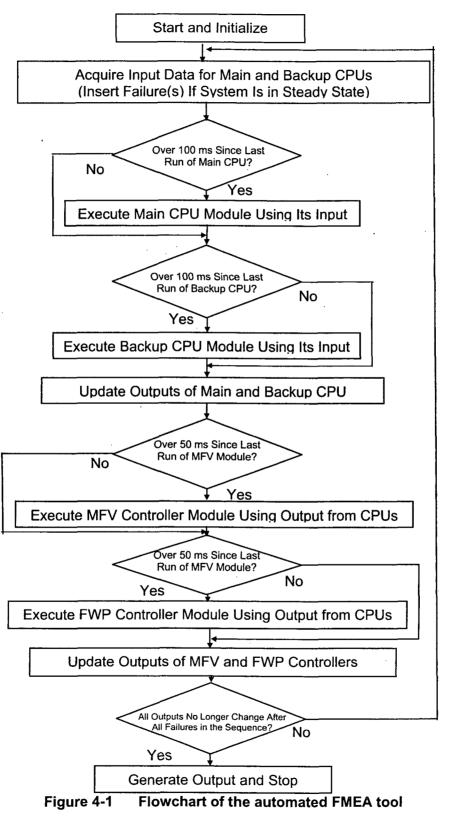

| 4-1    | Flowchart of the automated FMEA tool                                              | . 4-4       |

| 4-2    | A summary of the automated FMEA tool development and implementation               |             |

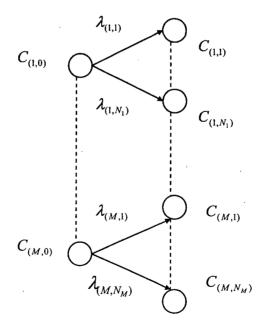

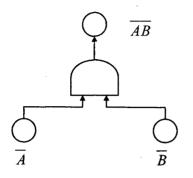

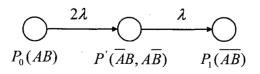

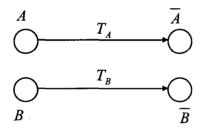

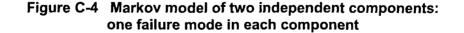

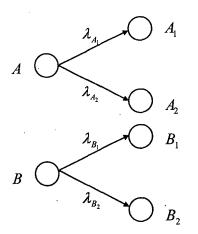

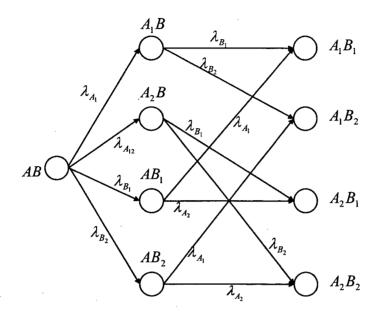

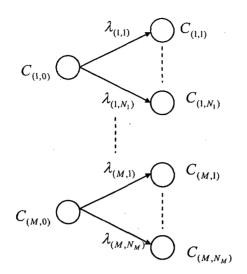

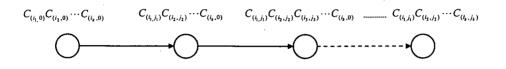

| 5-1    | Markov models for <i>M</i> independent components                                 | . 5-3       |

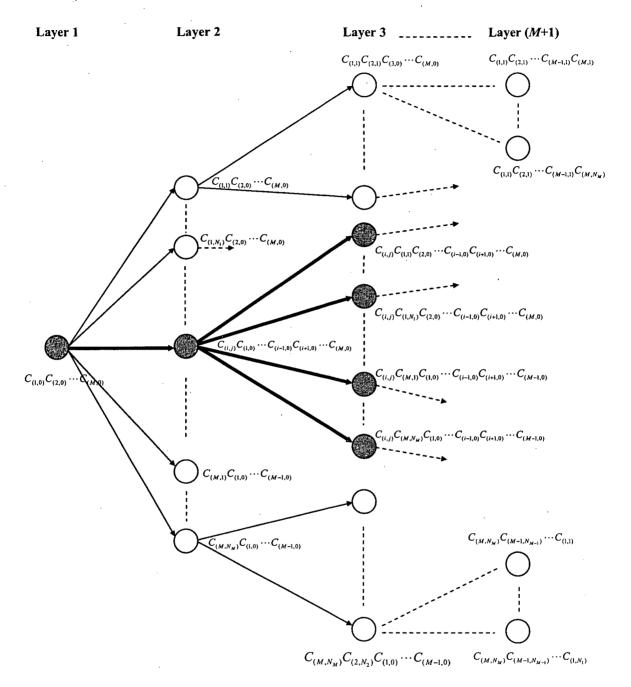

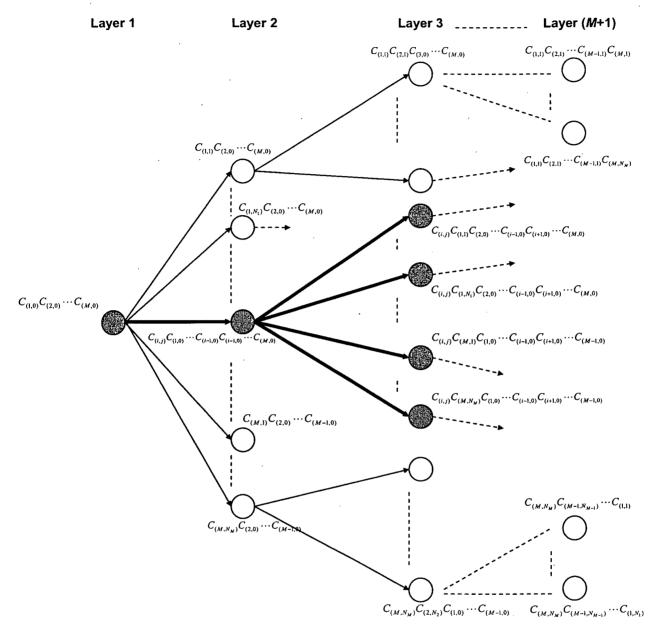

| 5-2    | Markov model of a system with M components                                        | . 5-4       |

| 5-3    | A small portion of the Markov diagram for the DFWCS                               | . 5-5       |

| 5-4    | Markov model of a system with k components and each component has one failure     |             |

| •      | mode                                                                              | . 5-9       |

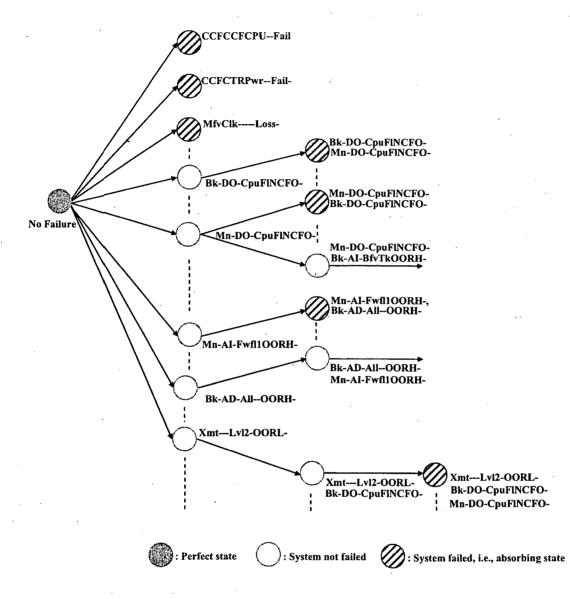

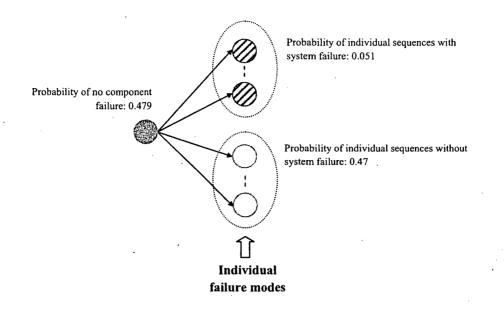

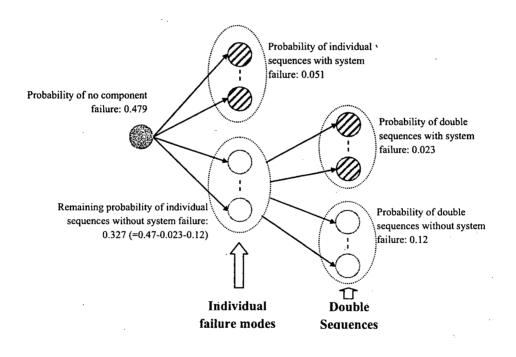

| 7-1    | Markov diagram for and quantification of individual failure modes                 | . 7-3       |

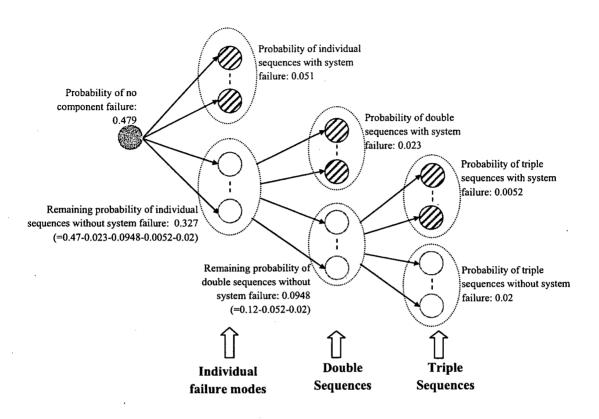

| 7-2    | Markov diagram for and quantification of both individual and double sequences     | . 7-3       |

| 7-3    | Markov diagram for and quantification of individual, double, and triple sequences |             |

х

## LIST OF TABLES

| Table_       | -                                                                                                    | <u>Page</u> |

|--------------|------------------------------------------------------------------------------------------------------|-------------|

| 3-1          | Illustrative examples of performing FMEA at component level of the main CPU module                   | . 3-10      |

| 3-2          | Illustrative examples for performing FMEA at component level of the FWP controller module            | . 3-18      |

| 4-1          | Analog input signals to the main and backup CPUs                                                     |             |

| 4-2<br>4-3   | Digital input signals to the main and backup CPUs<br>Analog input signals to the FWP controller      | . 4-8       |

| 4-4<br>4-5   | Digital input signals to the FWP controller<br>Analog input signals to the MFV controller            | . 4-9       |

| 4-6<br>4-7   | Digital input signals to the MFV controller<br>Analog output signals of the main and backup CPUs     | . 4-10      |

| 4-8<br>4-9   | Digital output signals of the main and backup CPUs<br>Analog output signals of the FWP controller    |             |

| 4-10<br>4-11 | Digital output signals of the FWP controller<br>Analog output signals of the MFV controller          |             |

| 4-12         | Digital output signals of the MFV controller                                                         |             |

| 6-1          | Failure data used in quantifying the DFWCS reliability model                                         | . 6-5       |

| 7-1<br>7-2   | Quantification of system failure probability and frequency<br>Frequency of loss of automatic control |             |

| 8-1          | Results of uncertainty analysis for frequency of loss of automatic feedwater control (per year)      |             |

| 8-2          | A summary of sensitivity analyses                                                                    | . 8-10      |

### EXECUTIVE SUMMARY

#### Background

Nuclear power plants (NPPs) traditionally have relied upon analog systems for monitoring, control, and protection functions. With a shift in technology from analog systems to digital systems with their functional advantages, existing plants have begun to replace current analog systems, while new plant designs fully incorporate digital systems. Since digital instrumentation and control (I&C) systems are expected to play an increasingly important role in NPP safety, the United States (US) Nuclear Regulatory Commission (NRC) established a digital system research plan that defines a coherent set of research programs to support its regulatory needs.

Deterministic criteria underlie the current licensing basis for digital systems. In its 1995 Probabilistic Risk Assessment (PRA) policy statement, the Commission encouraged using PRA technology in all regulatory matters to the extent supported by the state of the art in PRA methods and data. At present, no methods for quantifying the reliability of digital systems are sufficiently mature to be acceptable to the NRC. Although many activities have been completed in the area of risk-informed regulation, the risk-informed analysis process for digital systems has not yet been satisfactorily developed. Therefore, one of the research programs included in the NRC's digital system research plan addresses risk assessment methods and data for digital systems.

The objective of the NRC program on risk assessment methods and data for digital systems is to identify and develop methods, analytical tools, and regulatory guidance to support: (1) using information on the risks of digital systems in NPP licensing decisions and (2) including models of digital systems into NPP PRAs. Specifically, the NRC currently is assessing the reliability of digital I&C systems, using traditional and non-traditional (dynamic) methods in parallel. For the purposes of this research, dynamic methods are defined as those explicitly attempting to model: (1) the interactions between an NPP digital I&C system and the NPP physical processes, i.e. the values of process variables and (2) the timing of these interactions, i.e., the timing of the progress of accident sequences. Traditional methods are defined here as those that are well-established but do not explicitly model either of these two aspects. An example of this type of traditional method is the Event Tree/Fault Tree (ET/FT) approach.

In the past few years, Brookhaven National Laboratory (BNL) has been working on NRC projects to investigate methods and tools for probabilistic modeling of digital systems. The work included reviewing literature on digital system modeling, reviewing and analyzing operating experience of digital systems, developing estimates of failure rates using a Hierarchical and undertaking Failure Modes Bavesian Method (HBM) analysis, and Effects Analyses (FMEAs) of digital systems. These reviews reveal that failures of digital systems have caused several events that resulted in either a reactor trip or equipment unavailability at US NPPs, at least one event at a foreign NPP that resulted in a small loss of coolant accident during refueling, and numerous significant events in other industries. Based on this experience, the potential for digital systems failures to be contributors to plant risk cannot be ruled out. The NRC tasked BNL to conduct research on using traditional reliability modeling methods for digital I&C systems, which is the subject of this report. Information on the NRC research on the use of dynamic reliability modeling methods for digital I&C systems can be found in NUREG/CR-6901 [Aldemir 2009], NUREG/CR-6942 [Aldemir 2009], and NUREG/CR-6985 [Aldemir 2009].

The principal objective of BNL's project is to determine the existing capabilities and limitations of using traditional reliability modeling methods to develop and quantify digital system reliability models. The desired goal is supporting the development of regulatory guidance for assessing risk evaluations involving digital systems. To accomplish this objective, the following tasks were performed:

- 1. Develop desirable characteristics for reliability models of digital systems that could provide input to the technical basis for risk evaluations for current and new reactors.

- 2. Select two traditional reliability methods and attempt to apply them to an example digital system to determine the capabilities and limitations of these methods.

- 3. Compare the resulting digital system reliability models to the desirable characteristics to identify areas where additional research could potentially improve the quality and usefulness of digital system reliability models.

In keeping with the principal objective stated above, this project generally did not involve advancements in the state of the art, such as detailed analysis and quantification of software reliability.

NUREG/CR-6962 [Chu 2008a] documents the development of the desirable characteristics for reliability models of digital systems, selection of the traditional reliability methods to be applied. and establishment of the process for performing the reliability study of a digital feedwater control system (DFWCS). As stated in NUREG/CR-6962 [Chu 2008a], the DFWCS was used since. during that phase of the project, detailed information was only available for that system. The two traditional reliability modeling methods chosen for trial application are the traditional ET/FT method and the Markov method. The former is commonly used by the US nuclear power industry and in other countries and industries. The Markov method can be a powerful tool for analyzing digital systems because it can explicitly model system configurations arising from the ability of some digital systems to detect failures and change their configuration during operation. The Markov method also explicitly treats failure and repair times. Further, the Markov method was used previously to model NPP systems and digital systems. NUREG/CR-6962 [Chu 2008a] also covers preliminary work on developing reliability models of the DFWCS, such as performing an FMEA of the system, analyzing data to estimate the failure parameters needed, and developing approaches for building Markov and ET/FT models of the system.

The current report documents the application of the selected traditional reliability methods to the DFWCS (often referred to as the benchmark study) and a comparison of the models with the desirable characteristics of NUREG/CR-6962 [Chu 2008a]. As stated above, since this project was not intended to advance the state of the art in modeling digital systems using traditional reliability modeling methods, the outcome of this project does not include identification or development of a method and supporting engineering analyses that are capable of being used for regulatory applications at the present. Rather the report identifies additional areas of research that need to be pursued in order to attain the ultimate objective of this research program. Due to these modeling limitations, as well as the weakness of publicly available digital component failure data, the current model and results cannot be used to support decision-making.

#### Summary of Approach

This study develops an approach for modeling digital systems and applies it to a DFWCS to demonstrate the underlying concepts of the approach. The top event selected for this proof-ofconcept study is the loss of automatic feedwater control. A FMEA was performed at a relatively fine level of detail, e.g., at the level of multiplexers (MUXs) and analog/digital (A/D) converters. This level of detail is considered appropriate for supporting the proof-of-concept reliability analysis of the DFWCS. A simulation tool was developed that reflects the execution of the DFWCS software. The simulation tool is used to determine the system response to postulated hardware failure modes and combinations thereof. The important role of the simulation tool in determining system success or failure reduces the ET/FT and Markov models solely to means for quantifying system reliability (i.e., the ET/FT and Markov models are not used to identify the system failure paths, they are only used to quantify them). Since it was determined during the study that the order of component failures is important, ultimately only the Markov method was used for quantification. The sequences of component failure modes that lead to a system failure, as determined by the simulation tool, were used in defining the sequences of transitions in a Markov model. The Markov model was quantified to estimate the annual frequency with which a loss of automatic control of feedwater takes place, and to support sensitivity calculations that evaluate the benefits and importance of some of the features of the digital design. The quantification of the system model makes use of publicly available component failure parameters and the results of a HBM analysis of the raw data in the Reliability Analysis Center PRISM database that accounts for the uncertainty associated with different data sources.

The approach developed in this study, including the FMEA, simulation tool, and Markov model, should be generically applicable to digital systems. Also, while it is recognized that non-safety-related control systems and safety-related protection systems, such as a reactor protection system (RPS), have several significant design differences, it is believed that the insights and conclusions derived from this proof-of-concept study, which are mostly related to modeling methods, generally apply to both types of systems, unless otherwise noted.

#### Conclusions

The following conclusions were derived from performance of this study.

1. The traditional method used in the study, i.e., Markov method, must be supported by strong engineering knowledge and supporting analyses of the systems being studied. A simulation model of the system is a critical tool in facilitating reliability model development.

At the level of detail considered, the study requires a deterministic model that simulates the execution of the system software to capture the system design features, particularly those of the software, and to determine which sequences of postulated component failure modes would cause the system to fail. The simulation model is an enhancement to the state of the art<sup>(1)</sup> that allows the system behavior under failure conditions to be approximately accounted for in the reliability model, including not only the system control algorithms, but also the complex control logic based on the status of various signals of the controlled processes and that of the components of the system. Without the simulation tool, it would be very difficult, or even impossible, to directly develop a Markov or fault tree model that captures all of the details of the system design.

2. The level of detail of the DFWCS model is adequate for capturing many of the system design features, while not being too complicated to be developed and solved.

The Markov model of the DFWCS demonstrated the feasibility of the proposed approach. The level of detail of the model is consistent with that at which failure parameters are available (although the data has weaknesses, as discussed next). Even though the simulation tool does not encompass a thermal-hydraulic model of the plant, the system failure modes and sequences can be identified from information on its design. The state explosion problem of a detailed Markov model is resolved by truncating the higher order failure sequences when convergence is achieved. The usefulness of such a model is demonstrated further by performing a few sensitivity calculations that evaluate the importance of some of the digital design features, such as watchdog timers (WDTs), feedback of demand signals, and deviation logic.

#### 3. Failure parameters of digital components are scarce, and additional data are needed.

The PRISM database is one of the few publicly available sources of digital component failure parameters. NUREG/CR-6962 [Chu 2008a] performed a HBM analysis of raw data extracted from the PRISM database to account for the variability in the sources of the data. The Bayesian analysis resulted in some failure parameters with very large error factors, demonstrating large variability in the data. It may be challenging to calculate meaningful failure rates for hardware components because of this large variability. The failure parameters used in this study are only to demonstrate the reliability method and exercise the reliability model. These data are not appropriate for quantifying models intended for use in supporting decision-making (e.g., regulatory decisions or design changes).

<sup>&</sup>lt;sup>(1)</sup> While this project does not generally involve advancement in the state of the art, the development of a simulation model was deemed necessary to determine the feasibility of modeling digital I&C systems using traditional (non-dynamic) reliability methods.

#### Insights

A number of insights were obtained through performance of the DFWCS benchmark study. The key insights are summarized below.

- This study found that, for the DFWCS, the order in which component failure modes occur can affect the impact the failures have on the system. This is believed to be a generic feature of digital systems and should be captured in reliability models. The Markov method can easily account for the order in which component failure modes occur by considering different orders in different sequences. However, use of Markov quantification methods raises some issues, e.g., treatment of "non-minimal" sequences, with regard to integration with a PRA that is based on the ET/FT method.

- The model developed for the DFWCS is significantly more detailed than that of many other studies of digital systems. The experience of this study shows that it is difficult to capture the detailed interactions among the components and combinations of failures of the components using higher level modeling. It may be possible to use the detailed model of this study to develop an equivalent or approximate module level model by grouping the component failure modes of a module based on their impacts, e.g., on the input and output signals of the modules.

- Online repair is not considered to be possible for the DFWCS but may be possible for other digital systems, such as an RPS. If components can be repaired, the Markov model would have to be modified by adding transitions that represent repairs, making it much more difficult to solve. Using the simplified Markov method derived in this study, the governing equations with repair in the Laplace-transformed space can be solved analytically, and the inverse Laplace transform can be solved in the same way of solving the sequences without repair. Alternatively, it may be possible to develop a higher level model based on the detailed model and numerically solve the higher level model even if it includes repair.

- Performing the FMEA and running the simulation tool revealed two kinds of scenarios (one involving differences in signal delay times, and the other involving both central processing units [CPUs] operating in tracking mode) that represent potential weaknesses of the system design. The discovery of these scenarios, which were not identified in the plant's hazards analysis, suggests that the simulation tool potentially could serve to verify and validate the system software. Development of the simulation tool offers a capability to undertake test runs of the software and support deterministic evaluations of digital systems.

- This study did not specifically address Type I interactions (interactions with controlled processes external to the digital system), but considered Type II interactions (interactions among the components of the digital system) by studying the failure modes related to some events, such as communication between different components and multiplexing. Including plant dynamics could help capture subtle timing aspects of the performance of the DFWCS, e.g., issues associated with timing of failure sequences and the impacts of a within-the-range drifting signal. However, these issues are likely to be difficult to address even with a model of the plant included in the automated tool. In

addition, it is not clear, at present, whether the increased accuracy of modeling obtained through incorporation of a plant dynamics model would justify the increased complexity.

- The proposed approach of this study may also be capable of modeling safety related protection systems. For protection systems, it is believed that the use of dynamic methods may not offer any considerable improvements, because once a protection system is actuated, the feedback from the plant has no effect on the actuation.

- It is important that a reliability model realistically captures the fault-tolerance features of a digital system. In this study, the major fault-tolerance features include deviation logic in the application software, redundant CPUs, and independent WDTs of the CPUs. The first two features are well captured using the simulation tool. In the case of the WDTs, for each failure mode associated with a CPU module, plant information and an understanding about how the system works were used to determine if the effect of each failure mode on the module can be detected by its WDT and/or the application software. Fault-tolerant features may also be characterized in terms of "coverages" that typically represent the fraction of failures that can be detected. If fault coverage is accounted for in the failure data, then detailed models of the features do not have to be explicitly included in the reliability models.

#### Areas of Potential Additional Research

The experience of developing the probabilistic model of the DFWCS identified many areas of research to enhance the state of the art in modeling digital systems. They are summarized below.

- Improved approaches for defining and identifying failure modes of digital systems should be developed. Both software and hardware failure modes need to be considered. In this study, the hardware component failure modes may not be complete and placeholders were used for software failures. Research on software failure modes that can be incorporated in reliability models of digital systems is needed. A review of software failure experience in different industries would be beneficial.

- Software reliability methods for quantifying the likelihood of failures of both application and support software need to be developed, as well as methods for modeling software CCFs across system boundaries.

- Methods and parameter data for modeling self-diagnostics, reconfiguration, and surveillance, including using other components to detect failures, are needed. Faulttolerance features are not limited to those modeled in this study. Different hardware redundancy techniques and software fault-tolerance designs can be applied to digital system designs. Incorporation of these different designs needs to be further pursued.

- Better data for hardware failures (both independent and common cause) and a break down of the failure rates by failure modes of digital components need to be collected. The research should include collection and analysis of generic manufacturer data and specific operating data.

- Use of Markov quantification methods raises some issues with regard to integration with a PRA that is based on the ET/FT method. Integration of Markov models, such as the one developed in this study, with an ET/FT PRA should be demonstrated.

- Methods for human reliability analysis (HRA) associated with digital systems need to be investigated. In general, digital upgrades at current NPPs and the designs of new reactors introduce new human system interfaces that are significantly different from those of existing plants. HRA research is needed to address these new interfaces in support of PRAs for both existing plants and new reactors.

- This study identified that it may be beneficial to include controlled processes in modeling drifting signals of a control system, but not necessarily for a protection system. It is also not clear whether the increased accuracy of modeling obtained through incorporation of a plant dynamics model would justify the increased complexity and effort required for intensive simulation. Determining if and when a model of controlled processes is necessary in developing a reliability model of a digital system should be further researched.

### ACKNOWLEDGEMENTS

The authors are grateful to the United States Nuclear Regulatory Commission and external peer reviewers who commented on our draft report. We also express our appreciation to Avril Woodhead for her editorial review of the report, and to Jean Frejka and Nicole Kelly who put several versions of the report together and helped with the logistics of the project.

1

### ACRONYMS AND ABBREVIATIONS

| AC    | Alternating Current                     |

|-------|-----------------------------------------|

| A/D   | Analog/Digital                          |

| A/M   | Automatic/Manual                        |

| ALWR  | Advanced Light Water Reactor            |

| ASIC  | Application Specific Integrated Circuit |

| BFRV  | Bypass Feedwater Regulating Valve       |

| BFV   | Bypass Feedwater Valve                  |

| BIOS  | Basic Input/Output System               |

| BNL   | Brookhaven National Laboratory          |

| CCF   | Common-Cause Failure                    |

| CCMT  | Cell-to-Cell Mapping Technique          |

| CPU   | Central Processing Unit                 |

| D/A   | Digital/Analog                          |

| DC    | Direct Current                          |

| DEMUX | Demultiplexer                           |

| DFM   | Dynamic Flowgraph Methodology           |

| DFWCS | Digital Feedwater Control System        |

| EMI   | Electromagnetic Interference            |

| EPRI  | Electric Power Research Institute       |

| ET    | Event Tree                              |

| FMEA  | Failure Modes and Effects Analysis      |

| FT    | Fault Tree                              |

| FWP   | Feedwater Pump                          |

| HBM   | Hierarchical Bayesian Method            |

| HRA   | Human Reliability Analysis              |

| HVAC  | Heating, Venting, and Air Conditioning  |

| IC    | Integrated Circuit                      |

| I&C   | Instrumentation and Control             |

| IE    | Initiating Event                        |

| I/O   | Input and Output                        |

| I/P   | Current-to-Pneumatic                    |

| ISA   | Industry Standard Architecture          |

### ACRONYMS AND ABBREVIATIONS (Cont'd)

| mA<br>ms<br>MFP<br>MFRV<br>MFV<br>MFV<br>MFW<br>MUX | Milliamperes<br>Milliseconds<br>Main Feedwater Pump<br>Main Feedwater Regulating Valve<br>Main Feedwater Valve<br>Main Feedwater System<br>Multiplexer |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| NCFC                                                | Normally Closed, Fails Closed                                                                                                                          |

| NCFO                                                | Normally Closed, Fails Open                                                                                                                            |

| NOFC                                                | Normally Open, Fails Closed                                                                                                                            |

| NOFO                                                | Normally Open, Fails Closed                                                                                                                            |

| NPP                                                 | Nuclear Power Plant                                                                                                                                    |

| NRC                                                 | Nuclear Regulatory Commission                                                                                                                          |

| OOR                                                 | Out-of-Range                                                                                                                                           |

| OORH                                                | Out-of-Range High                                                                                                                                      |

| OORL                                                | Out-of-Range Low                                                                                                                                       |

| PAL                                                 | Programmable Array Logic                                                                                                                               |

| PDI                                                 | Pressure Differential Indicating                                                                                                                       |

| PRA                                                 | Probabilistic Risk Assessment                                                                                                                          |

| PWR                                                 | Pressurized Water Reactor                                                                                                                              |

| PWR_ON                                              | Power on                                                                                                                                               |

| RAC                                                 | Reliability Analysis Center                                                                                                                            |

| RAM                                                 | Random Access Memory                                                                                                                                   |

| ROM                                                 | Read-Only Memory                                                                                                                                       |

| RPM                                                 | Reliability Prediction Method                                                                                                                          |

| RPS                                                 | Reactor Protection System                                                                                                                              |

| S/G                                                 | Steam Generator                                                                                                                                        |

| SOKC                                                | State-of-Knowledge-Correlation                                                                                                                         |

| SRS                                                 | Savannah River Site                                                                                                                                    |

| URD                                                 | Utility Requirements Document                                                                                                                          |

| US                                                  | United States                                                                                                                                          |

| WDT                                                 | Watchdog Timer                                                                                                                                         |

xxii

### 1. INTRODUCTION

#### 1.1 Background

Nuclear power plants (NPPs) traditionally have relied upon analog systems for monitoring, control, and protection functions. With a shift in technology from analog systems to digital systems with their functional advantages, plants have begun such replacement, while new plant designs fully incorporate digital systems. Since digital instrumentation and control (I&C) systems are expected to play an increasingly important role in nuclear power plant safety, the United States (US) Nuclear Regulatory Commission (NRC) established a digital system research plan [NRC 2006] that defines a coherent set of research programs to support its regulatory needs.

Deterministic criteria underlie the current licensing basis for digital systems. In its 1995 Probabilistic Risk Assessment (PRA) policy statement [NRC 1995], the Commission encouraged using PRA technology in all regulatory matters to the extent supported by the state of the art in PRA methods and data. At present, no methods for quantifying the reliability of digital systems are sufficiently mature to be acceptable to the NRC. Although many activities have been completed in the area of risk-informed regulation, the risk-informed analysis process for digital systems has not yet been satisfactorily developed. Therefore, one of the research programs included in the NRC's digital systems.

The objective of the NRC program on risk assessment methods and data for digital systems is to identify and develop methods, analytical tools, and regulatory guidance to support: (1) using information on the risks of digital systems in NPP licensing decisions and (2) including models of digital systems into NPP PRAs. Specifically, the NRC currently is assessing the reliability of digital I&C systems, using traditional and non-traditional (dynamic) methods in parallel. For the purposes of this research, dynamic methods are defined as those explicitly attempting to model: (1) the interactions between an NPP digital I&C system and the NPP physical processes, i.e., the values of process variables and (2) the timing of these interactions, i.e., the timing of the progress of accident sequences. Traditional methods are defined here as those that are well-established but do not explicitly model either of these two aspects. An example of this type of traditional method is the Event Tree/Fault Tree (ET/FT) approach.

In the past few years, Brookhaven National Laboratory (BNL) has been working on NRC projects to investigate methods and tools for probabilistic modeling of digital systems. The work included reviewing literature on digital system modeling [Chu 2004, Chu 2007, Chu 2008a], reviewing and analyzing operating experience of digital systems [Chu 2006], developing estimates of failure rates using a Hierarchical Bayesian Method (HBM) [Yue 2006], and undertaking Failure Modes and Effects Analyses (FMEAs) of digital systems. These reviews reveal that failures of digital systems have caused several events that resulted in either a reactor trip or equipment unavailability at US NPPs, at least one event at a foreign NPP that resulted in a small loss of coolant accident during refueling [Nuclear Energy Agency 1998], and numerous significant events in other industries. Based on this experience, the potential for digital systems failures to be contributors to plant risk cannot be ruled out. The NRC tasked BNL to conduct research on using traditional reliability modeling methods for digital I&C systems, which is the subject of this report. Information on the NRC research on the use of dynamic reliability modeling methods for digital I&C systems can be found in NUREG/CR-6901 [Aldemir 2006], NUREG/CR-6942 [Aldemir 2007], and NUREG/CR-6985 [Aldemir 2009].

The principal objective of BNL's project is to determine the existing capabilities and limitations of using traditional reliability-modeling methods to develop and quantify digital system reliability models. The desired goal is supporting the development of regulatory guidance for assessing risk evaluations involving digital systems. To accomplish this objective, the following tasks were performed:

- 1. Develop desirable characteristics for evaluating reliability models of digital systems that could provide input to the technical basis for risk evaluations for current and new reactors.

- 2. Select two traditional reliability methods and attempt to apply them to an example digital system to determine the capabilities and limitations of these methods.

- 3. Compare the resulting digital system reliability models to the desirable characteristics to identify areas where additional research could potentially improve the quality and usefulness of digital system reliability models.

In keeping with the principal objective stated above, this project generally did not involve advancements in the state of the art, such as detailed analysis and quantification of software reliability. Earlier BNL work on software reliability is summarized in [Chu 2007].

NUREG/CR-6962 [Chu 2008a] documents the development of the desirable characteristics for evaluating reliability models of digital systems, selection of the traditional reliability methods to be applied, and establishment of the process for performing the reliability study of a digital feedwater control system (DFWCS). As stated in NUREG/CR-6962 [Chu 2008a], the DFWCS was used since, during that phase of the project, detailed information was only available for that system. The two traditional reliability-modeling methods chosen for trial application are the traditional ET/FT method and the Markov method. The former is commonly used by the US nuclear power industry and in other countries and industries. The Markov method can be a powerful tool for analyzing digital systems because it can explicitly model system configurations arising from the ability of some digital systems to detect failures and change their configuration during operation. The Markov method also explicitly treats failure and repair times. Further, the Markov method was used previously to model NPP systems and digital systems. NUREG/CR-6962 [Chu 2008a] also covers preliminary work on developing reliability models of the DFWCS, such as performing an FMEA of the system, analyzing data to estimate the failure parameters needed, and developing approaches for building Markov and ET/FT models of the system.

The current report documents the application of the selected traditional reliability methods to the DFWCS (often referred to as the benchmark study). This report also includes a comparison of the models with the desirable characteristics of NUREG/CR-6962 [Chu 2008a].

### **1.2 Objectives and Scope of Benchmark Study**

The objectives of the benchmark study documented in this report are twofold: (1) to apply two traditional methods, i.e., Markov and ET/FT methods, to a DFWCS, building on the work done in NUREG/CR-6962 [Chu 2008a] and (2) to compare the models against the NUREG/CR-6962 [Chu 2008a] desirable characteristics to evaluate the state of the art and identify areas where additional research would enhance this knowledge. As stated above, the DFWCS was selected as the initial benchmark system for the proof-of-concept study due to the availability of the necessary detailed system information. While it is recognized that non-safety-related control systems and safety-related protection systems have several significant design differences, it is believed that the

insights and conclusions derived from this proof-of-concept study, which are mostly related to modeling methods, generally apply to both types of systems, unless otherwise noted.

This proof-of-concept study models the DFWCS while the plant is operating at full power, and estimates the frequency that a loss of automatic control of the system takes place, including switchover to manual control and incorrect control output signals, caused by hardware failures of its components and support systems. Modeling manual control is beyond the scope of the study. In general, other top events associated with the DFWCS can be defined, and models of those top events can be developed accordingly. External causes of failure, such as fires and seismic events, and other modes of system operation are beyond the scope of this study. Due to the lack of consensus on software reliability methods, modeling software failures also is beyond the scope of this project, though placeholders for software failure rates are identified in the models. An arbitrarily selected small failure rate is used in the model quantification, such that the contribution of software failure does not mask the contribution from other modeled failures. The inclusion of placeholders for software failures is not intended to imply that it is appropriate to model hardware and software failures as separate entities, nor that software failures can be addressed probabilistically. These placeholders merely serve to indicate that ultimately software reliability should be addressed in some manner, even though it is out of the scope of the current study. Integration of the reliability model developed in this study with a nuclear plant PRA is also beyond the scope of this study.

As stated previously, the objective of the NRC program on risk assessment methods and data for digital systems is to identify and develop methods, analytical tools, and regulatory guidance to support: (1) using information on the risks of digital systems in NPP licensing decisions and (2) including models of digital systems into NPP PRAs. Since the principal objective of the current project was only to evaluate the existing state of the art in modeling digital systems using traditional reliability modeling methods, and not to advance the state of the art, the outcome of this project does not include identification or development of a method and supporting engineering analyses that are capable of being used for regulatory applications at the present. Rather the report identifies (in Section 11.3) additional areas of research that need to be pursued in order to attain the ultimate objective of this research program. Due to these modeling limitations, as well as the weakness of publicly available digital component failure data, the current model and results cannot be used to support decision-making.

#### **1.3** Overall Approach of Benchmark Study

This study found that at the level of detail that is modeled, it is not possible to deductively develop ET/FT logic or identify the Markov states that represent system failure, as is usually done in traditional ET/FT and Markov analyses. Instead, an automated FMEA tool was developed to identify the sequences of failures that lead to a system failure, and Markov and fault tree methods are only considered as a means to quantify the sequences. Although an automated tool was used, the methods applied are still referred to as "traditional," since they do not attempt to explicitly model the interactions between the DFWCS and the plant physical processes.

In this study, the approaches described in NUREG/CR-6962 [Chu 2008a] for developing ET/FT and Markov models of the DFWCS were attempted and modified, as necessary, to develop reliability models of the system. The modifications included the following:

- 1. The FMEA approach of the main central processing unit (CPU) module<sup>(1)</sup> developed in NUREG/CR-6962 [Chu 2008a] was applied to other modules in the system. To correctly determine the effects of the postulated failure modes, following the suggestion of NUREG/CR-6962 [Chu 2008a], a simulation model of the system was developed that includes the actual software of the modules and needed interfaces to automate the process of determining the system's responses. The simulation tool also was used to assess the system's response to combinations of failures.

- 2. Because the simulation tool can handle combinations of failure modes as well as individual ones, there was no need to group these modes as proposed in NUREG/CR-6962 [Chu 2008a]. This change is expected to enhance the model's accuracy.

- 3. Since the simulation tool generates combinations of failures that lead to system failure, the fault tree and Markov model approaches proposed in NUREG/CR-6962 [Chu 2008a] were not needed to identify combinations of failures. The generated failure combinations were used directly in quantification. In fact, at the level of detail considered in this study, it is not feasible to deductively develop a fault tree or Markov transition state model for the DFWCS.

- 4. The simulation tool was used to investigate the effects of the order in which failure modes occur. This investigation revealed that, in some cases, the order of failure does make a difference. Therefore, it is necessary to explicitly account for the order in which failures occur, and more appropriate to refer to the combinations of failure modes as failure (or failure mode) sequences. Since the order of the failures was found to be important, the failure sequences were quantified using a Markov model. Both an exact solution and an approximate solution to the Markov model were derived and used in quantifying the top event.

- 5. The sequences of the Markov model are similar to cutsets typically considered in a PRA, except for the way in which the sequences are quantified. Use of the Markov quantification method makes it more difficult to integrate the model with a PRA that is based on the ET/FT method. The integration is beyond the scope of this study. It can likely be done by converting the sequences into equivalent cutsets and using approximate methods of quantification.

The approach demonstrated in this proof-of-concept study should be applicable to any digital system. It is based on the use of failure modes of generic components of digital systems and publicly available component failure data. The level of detail of the model allows important digital design features to be captured. In particular, the use of an automated tool developed using the actual system software allows the software to be more realistically accounted for in the modeling. The use of a Markov model for quantifying the system-failure sequences takes into consideration the order in which failures occur in the sequences and the competition among failure modes of components. However, due to limitations in the state of the art for modeling digital systems, several significant issues remain to be resolved, as identified in this report.

<sup>&</sup>lt;sup>(1)</sup> In general, CPU represents a central processing unit, which is a generic component of digital systems. Here, a CPU module includes a CPU and its associated components such as a multiplexer, analog/digital converter, etc. In this study, a CPU of a CPU module is denoted as a microprocessor in order to avoid confusion with a CPU module, and CPU and CPU module are used interchangeably to represent a CPU module.

The following summarizes the approach used in this study with references to the chapters that provide more detailed documentation.

#### Definition of Top Event

This study is based on a DFWCS of a two-loop pressurized water reactor (PWR). Each of the two reactor-coolant loops has a DFWCS. The top event selected for the proof-of-concept study is failure of a DFWCS to automatically control feedwater to its associated steam generator while the plant is operating at full power during one year. This can be considered a contributor to the loss of main feedwater initiating event for the PRA of the plant. The defined top event does not take into consideration the possibility of manually controlling the system. For some system failure modes, manual control is still possible using the DFWCS. However, modeling manual control is beyond the scope of the study.

The system also performs its functions during low-power mode and after a reactor trip; these functions are beyond the scope of the study. Chapter 2 gives a summary description of the system and defines the system boundary of the modeling performed in this study; a more detailed description is provided in NUREG/CR-6962 [Chu 2008a].

#### Quantification of the Frequency of an Initiating Event

It is a commonly accepted PRA practice to estimate initiating event frequencies using operating experience. In case of loss of feedwater transients, a two-stage Bayesian analysis can be used. However, in order to perform such an analysis to consider the contribution of the DFWCS, it is required that the data across multiple plant and vendor designs with varying configurations be collected. Such information is not available in the public domain. As an alternative, in this study, an approach that models a digital system at the level of detail where generic component failure modes and failure data are available was developed. This approach should be applicable to modeling both digital control and protection systems.

An initiating event frequency, f, is the expected number of system failures per unit time. It is related to the reliability of the system R(T), i.e., the probability that the system is operating successfully in time period (0, T), by

(1-1)

$$f = -\frac{\ln[R(T)]}{T}$$

Equation (1-1) was derived in NUREG/CR-6962 [Chu 2008a] assuming the initiating event follows a Poisson process with a constant rate, and can be used to evaluate the initiating event frequency, using the R(T) assessed over a time period T, employing a Markov model of the DFWCS. The frequency f is, therefore, the average frequency over the time period T. Note that the actual failure rate of the Markov model changes with time and the use of the average frequency is an approximation. The equation is applicable to any reliability model that calculates a system reliability, including those models that allow component level repair and replacement.

#### FMEA and Simulation Model

A team of analysts manually undertook the FMEA documented in NUREG/CR-6962 [Chu 2008a]. In many situations, the response of the system to specific individual failures was difficult to

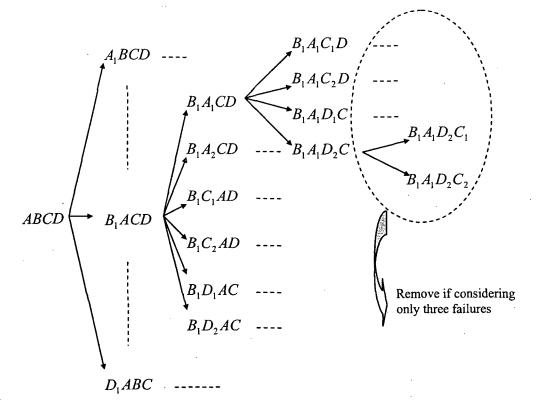

determine, mainly due to lack of documentation and the complex logic modeled in the software. However, even with more complete documentation, it is not feasible to manually determine the system response to multiple failures. Hence, in this study, a simulation tool was developed to facilitate determining the effects of postulated failures. The simulation tool incorporates the software of the CPUs and controllers, and implements rules for assessing whether a loss of automatic control occurs. The tool allows the failures and failure combinations of the components to be postulated, and then represented in terms of their impact on the input and output signals of the CPUs and controllers and associated internal variables of the software. The tool also determines whether a system failure takes place based on the internal states of the system. For example, a detected loss of a steam-generator-level sensor causing a failover, followed by a spurious signal of the watchdog timer associated with the backup CPU, will cause the main feedwater valve (MFV) and feedwater pump (FWP) controllers to switch to the manual mode, which constitutes a system failure. The simulation tool was used to systematically perform the FMEA of all modules of the DFWCS, using the approach described in NUREG/CR-6962 [Chu 2008a] for the main CPU module. It first was employed in identifying those individual failures that directly lead to a system failure, e.g., a failure of the microprocessor of the MFV controller. Such failures are single failures of the system. For those individual failures that do not fail the system, i.e., latent failures. combinations of two failures were considered to identify those sequences of double failures that lead to a system failure. Continuing this process generates higher and higher order sequences. Chapters 3 and 4 discuss the details of the FMEA and simulation tool.

The use of a simulation tool in performing the FMEA can be considered a supporting analysis which plays an important role in developing the reliability model of the DFWCS, just like thermal-hydraulic analyses are used to determine the success criteria and accident timing used in developing accident sequences of a PRA. It is especially important to digital systems due to the complexity of these systems and their use of software. The important role of the simulation tool in determining system success or failure reduces the Markov and ET/FT methods to potential methods solely for quantifying system reliability (i.e., the Markov and ET/FT methods are not used to identify the system failure paths, they are only used to quantify them). Because use of the simulation tool revealed that the order of component failures can be important, the Markov method was selected for quantifying the system failure paths, since it can explicitly account for the order of the failures by defining different sequences of transitions/failures leading to different system states.

#### Development and Quantification of a Markov Model of DFWCS

A Markov model of a system typically can be represented in terms of a transition diagram showing all the system states and possible transitions among them. It can also be expressed in terms of a set of linear differential equations modeling the transitions among system states, i.e.,

$$\frac{d\underline{P}}{dt} = \underline{MP}, \qquad (1-2)$$

where <u>P</u> represents the probabilities of the system states, and <u>M</u> is the transition matrix containing the constant transition rates among the system states. The solution of Equation (1-2) gives probabilistic information about the system. For example, the sum of the probabilities of success states is the reliability, from which the frequency of the initiating event can be calculated using Equation (1-1).

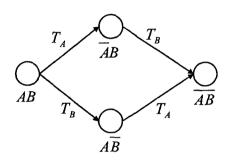

As often is the case for a Markov model, the DFWCS is assumed to initially be in an operable state (i.e., at time = 0). Every time a component of the DFWCS fails, the system transits into another state. An important feature of the Markov model of the system is that components can have different failure modes that entail different impacts on the system. In formulating the DFWCS's transition diagram, all possible transitions in any possible order should be considered. State explosion, i.e., a very large number of possible system states that makes the model too complicated to develop and solve, is a common issue with detailed Markov models. It is addressed in this study by truncating system failure sequences based on their order (i.e., the number of failures in the sequence) and demonstrating that convergence of system failure probability is achieved. This is similar to the concept of cutset truncation (on order) typically done in ET/FT analyses.

The results of the FMEA of the system specify if a system state is a failed state, in which case no additional transitions out of it need to be considered, since the system is already failed. Such a state is called an absorbing state.

For the DFWCS being modeled in this study, a failed component cannot be repaired while the system is operating; therefore, repair does not need to be included in the model. This allows the exact solution of the Markov model to be derived analytically. A simplified solution was developed to compare with the exact solution. Chapter 5 describes the Markov model, and Appendix C contains the detailed derivation of the solution of the model, along with introductory material about Markov modeling solutions. Chapter 7 provides the results of the quantification of the Markov model for the DFWCS.

#### Data Analysis

NUREG/CR-6962 [Chu 2008a] reviewed publicly available databases for digital system components and performed a Bayesian analysis that attempted to account for the variability of different raw data sources. In the review, potential weaknesses and limitations of the available databases were identified and discussed, and no attempt was made to validate or invalidate the available databases. The limitations in the publicly available failure parameters of digital components identified in NUREG/CR-6962 [Chu 2008a] indicate that additional research and development is needed in this area. This study makes use of the data of NUREG/CR-6962 [Chu 2008a] in developing and quantifying a model of the DFWCS. The data are not appropriate for quantifying models that are to be used in support of decision-making (e.g., regulatory decisions or design changes). They are only used in this project to demonstrate the reliability methods and exercise the reliability models.

The data for the quantification were derived from different sources. One important source was the raw data of the PRISM reliability prediction method [RAC PRISM]. The failure rates of many component failure modes were estimated by the HBM [Yue 2006]. For those components whose failure rates were not analyzed in this way, the PRISM RACRate model was used to estimate them [RAC PRISM]. In some cases, the failure rates were taken from other sources, such as NRC-sponsored studies, e.g., NUREG/CR-5500, Volume 10 [Wierman 2002].

In this study, different failure modes for a given component were considered. The failure rates of the different component failure modes were estimated using the failure mode distributions given by Meeldijk [1996] and Aeroflex [2005]. These sources break down the failure rate of a component into its different failure modes.

The failure parameters used in this study have very large uncertainties, and the failure mode distributions are incomplete. Chapter 6 discusses the data analysis and its weaknesses in more detail.

#### Uncertainty Analysis and Sensitivity Calculations